一 、发展过程

1 因FPGA片上资源(BRAM)有限,需要一个大存储容量芯片DDR,单位存储量大、高数据

带宽、读写速度快、价格相对便宜,DDR 的全名是 DDR SDRAM(双倍速率 同步动态随机存储器),如今 DDR 以及发展到第 5 代,随着硬件的发展,其功耗(下降)、内核电压(减小)、带宽(增加)、速度都得到大幅度提升。

带宽 :设备传输数据能力(数据吞吐量 )

2 RAM 分为SRAM(静态)和 DRAM(动态)

SRAM充电时不易丢失,多用于CPU的一级二级缓存

3

BANK :减小地址冲突,节约管脚 。

突发模式 :给出一个地址,可以连续读出数据 ,传输效率高

4

二 存储原理

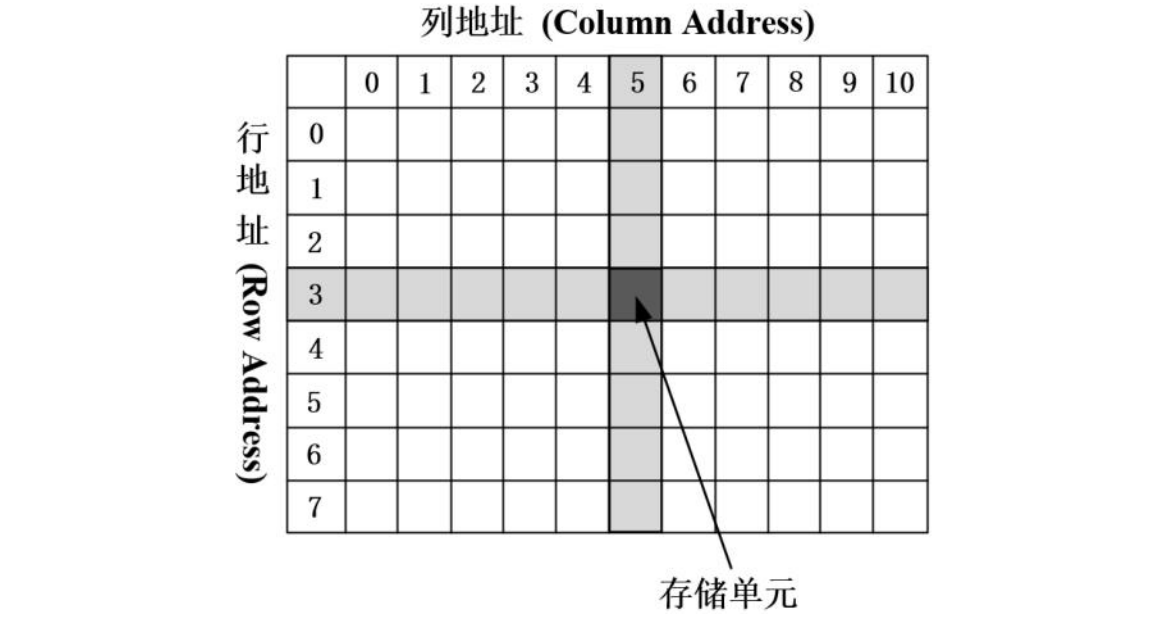

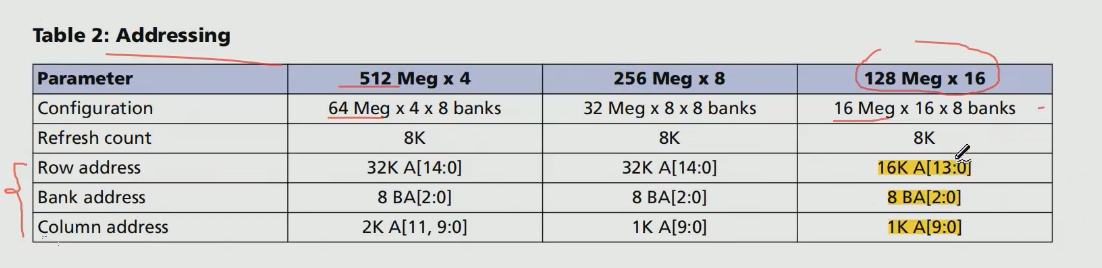

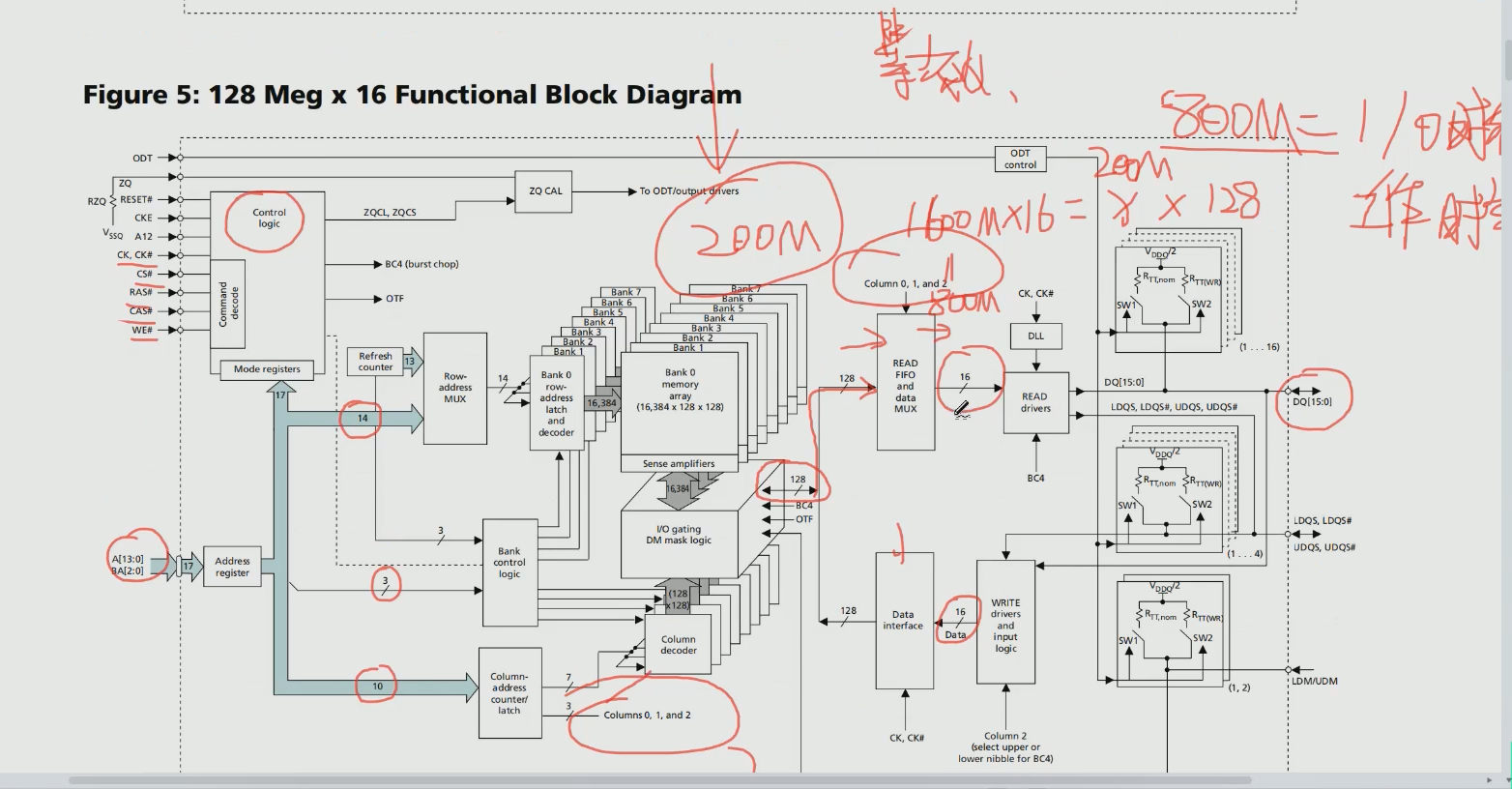

DDR3 存储空间为256MBYTE,分为8个BANK ,每个 bank 32Mbyte。每个存储单元16bit==2个字节

存储地址主要由 :bank地址,行地址和列地址构成 。行列地址共用一组管脚。同一时刻只能控制一个BANK.

![]()

DDR 存储一个 bit 数据是由一个存储电容、行选通三极管、列选通三极管、刷新放大器构成的,电容具有可充放电特性,所以需要不断刷新电容保持数据准确性 。

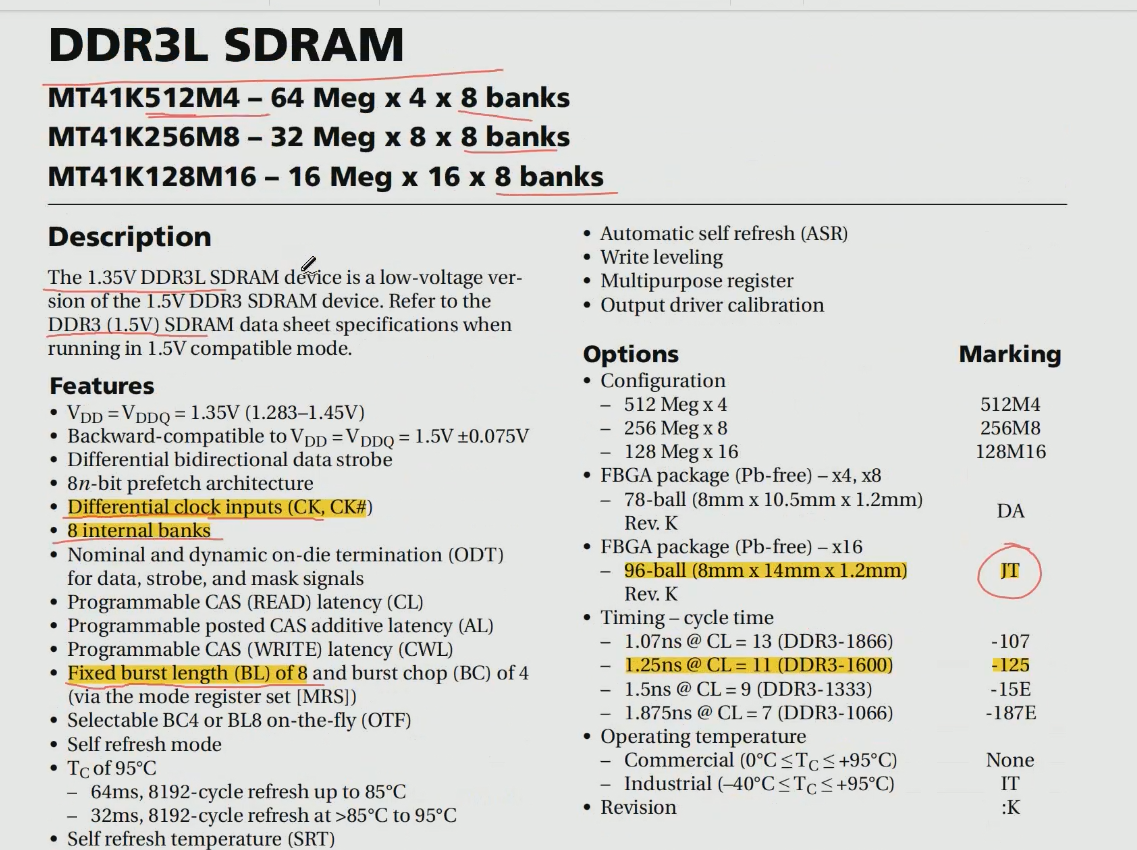

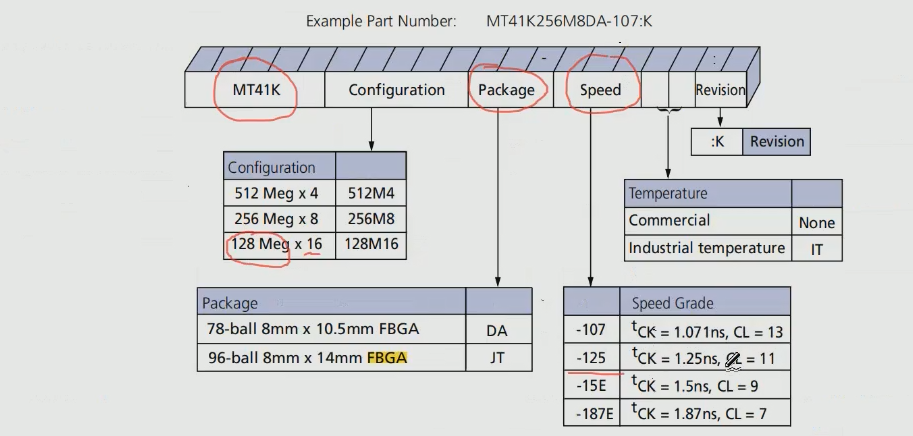

三 芯片手册

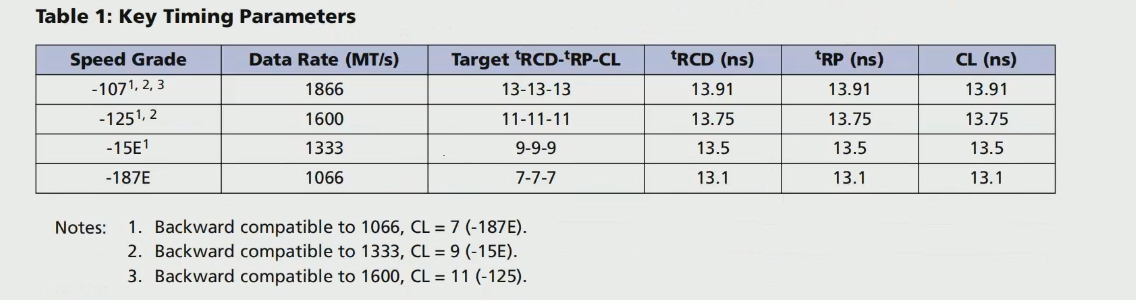

1 本 次 板 卡 上 搭 载 了 一 片 DDR3 SDRAM 芯 片 , 由 镁 光 公 司 生 产 , 其 型 号 为

MT41K128M(空间个数)16(比特数)JT-125(每个周期时间1.25纳秒),内存的主频率高达 800Mhz,数据的带宽(数据速率)为 800Mhz * 16 *2BPS,时钟速率800Mhz *2,内存大小为 256MB,半双工

Meg = MB

ROM = 行, COLUMN = 列

2 管脚

地址线(A[13:0]):传输行地址、列地址,A10 决定是否采用预充电

Bank 地址线(BA[2:0]):8 个 bank。

时钟线(CK、CK#):差分时钟,控制和地址输入都在时钟的上升沿(CK#的下降沿)采

样。

时钟使能(CKE):高电平时钟有效,两个作用:关闭时钟进入省电模式,进入自刷新。

片选信号(CS#):片选信号,高电平时,屏蔽所有的命令,拉低有效

数据掩码(输入)(LDM、UDM):数据的掩码,分为高字节、低字节,为低电平的时候数据有效。

命令控制信号(RAS#、CAS#、WE#):RAS 是行选通命令控制信号,CAS 是列选通命令控 制信号,WE 是写使能;低电平有效。

复位(RESET#):低电平有效。

数据线(DQ[15:0]):16bit 数据,一个时钟周期传输 2 次,每次 16bit。

数据选通信号(输出)(LDQS、LDQS#、UDQS、UDQS#):字节选通信号,差分信号

ODT:终端匹配电阻使能信号

3 存储架构

200M(物理时钟:传输数据使用时钟 ) 800M(IO时钟/工作时钟) 1600(等效时钟)

两个低三位决定读取数据的顺序

4 命令

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

6万+

6万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?