cache一致性问题:

因为cache中的内容是主存块副本,当对cache的内容进行更新时,就存在cache和主存如何保持一致性问题。

cache操作:两种情况 写命中 write hit):要写的单元已经在cache当中

两种处理方式

1.write through(直写)

同时写cache和主存单元

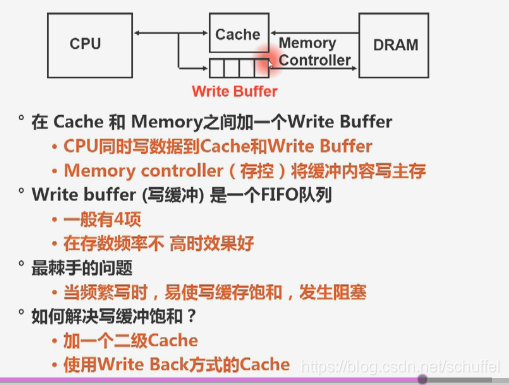

由于CPU写数据到cache很快,但是cache写到DRAM很慢,为了解决这个问题所以我们加入了写缓冲(write buffer)

2.write back( 回写)

即写cache时不管主存,直接在cache上面改就行,这个时候锁死主存那块数据(我想到了我们打开excel文件时,再修改桌面名字时发现一致性问题),

我们加入dirty-bit脏位:即判断cache里面内容修改没,没修改就不改主存

2.写不命中(write Miss):要写的单元不在cache中

有两种处理方式

1.write allocate(写分配)

将主存装入Cache,然后更新相应单元

2.no write allocate(非写分配)

直接写主存单元,不装入到cache, 与第一种相比没有利用到空间局部性,因为没有装入到cache中。

实现虚拟存储器需要解决的问题

1.块大小应该多大?2到 64kb

2.主存与辅存的空间管理 采用全相连映射,主存只要有空,就放进去,原因,缺页开销比cache大得多,而访问磁盘要几百万个时钟周期

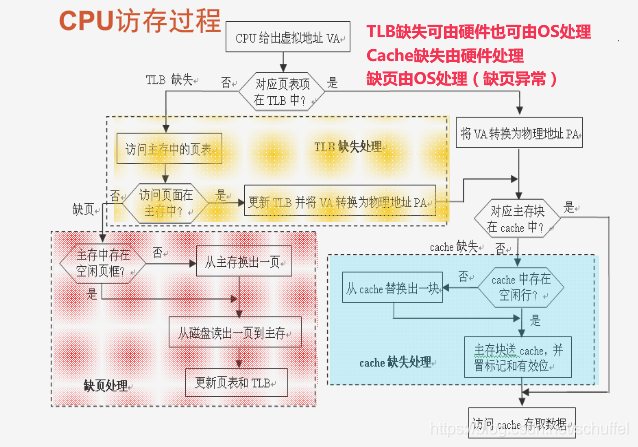

缺页 使用软件处理,cache缺失使用硬件处理

3.程序块/存储块之间如何映像

4.逻辑地址与物理地址之间如何转换,转换速度提高

5.主存辅存之间如何让进行替换

6.页表如何实现,需啊要记录啥信息 页表项

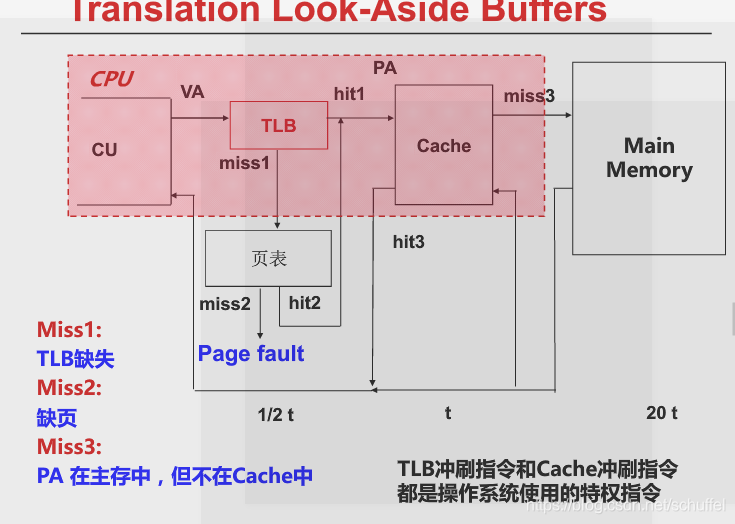

7.加快页表的访问速度 引入TLB(快表)

8.要找的内容不在主存

9.如何保护进程各自存储区不被其他进程访问 设定访问权限

cpu 访存过程:3个缺失处理,

TLB,Cache,页框

本文探讨了计算机系统中Cache一致性问题,包括Write Through和Write Back两种策略,以及Write Hit和Write Miss的处理方式。同时,介绍了实现虚拟存储器面临的关键问题,如块大小选择、空间管理、地址映射、页表实现和访问权限保护等,强调了TLB在加速页表访问中的作用。

本文探讨了计算机系统中Cache一致性问题,包括Write Through和Write Back两种策略,以及Write Hit和Write Miss的处理方式。同时,介绍了实现虚拟存储器面临的关键问题,如块大小选择、空间管理、地址映射、页表实现和访问权限保护等,强调了TLB在加速页表访问中的作用。

1345

1345

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?