【快速教程】用Multisim逻辑转换器:真值表秒变逻辑电路!

目标读者:电子设计初学者、数字电路爱好者

适用场景:课程设计、竞赛项目、快速验证逻辑功能

工具版本:Multisim 14.3

一、逻辑转换器能做什么?

Multisim的逻辑转换器(Logic Converter)支持:

✅ 真值表 → 逻辑表达式

✅ 逻辑表达式 → 电路图

✅ 表达式化简(如卡诺图优化)

优势:省去手工推导,避免计算错误,5分钟出结果!

二、操作步骤(以3输入表决电路为例)

1. 准备真值表

假设设计一个“3人投票电路”:至少2人同意(输入1)时,输出1。

| A | B | C | 输出 |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

–

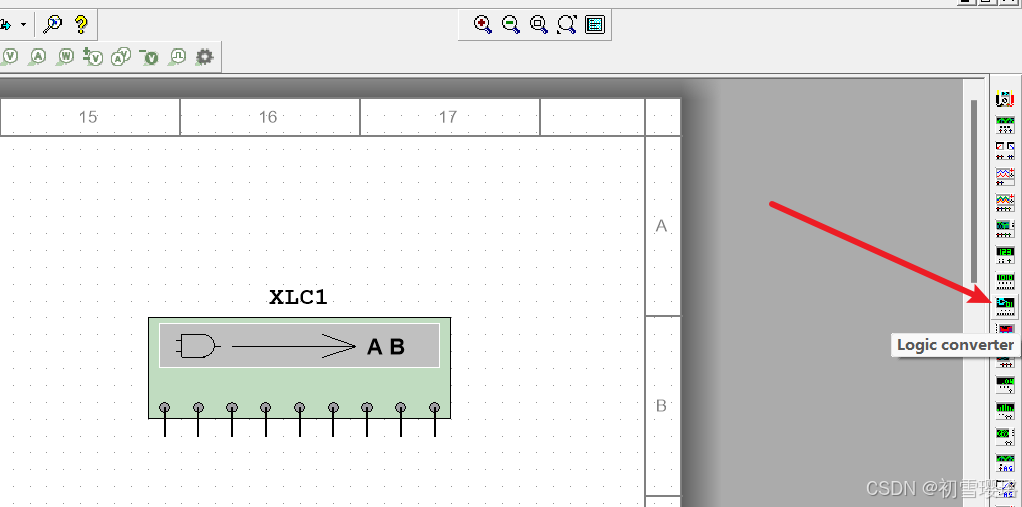

2. 打开逻辑转换器

- 在Multisim中点击菜单栏

Tools → Logic Converter。 - 将逻辑转换器图标拖入工作区。

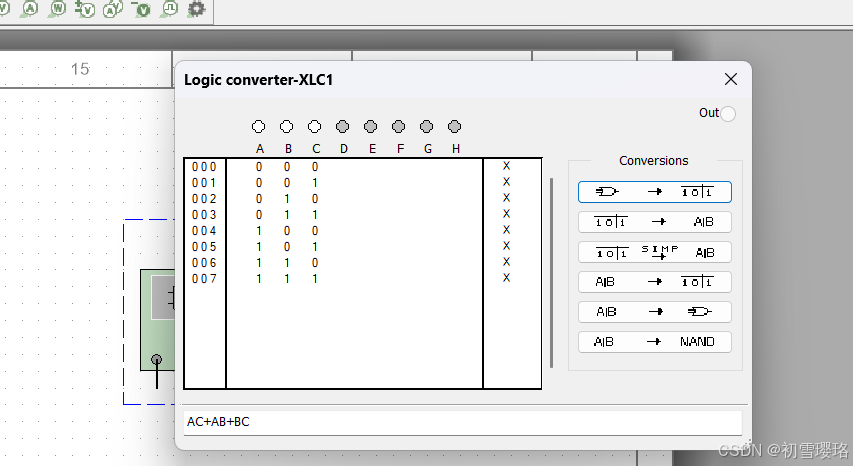

3. 输入真值表

-

双击逻辑转换器,界面如下:

-

设置输入数:顶部选择 3 inputs(A/B/C)。

-

填写输出列:根据真值表,点击输出列(Out),依次输入

0,0,0,1,0,1,1,1。

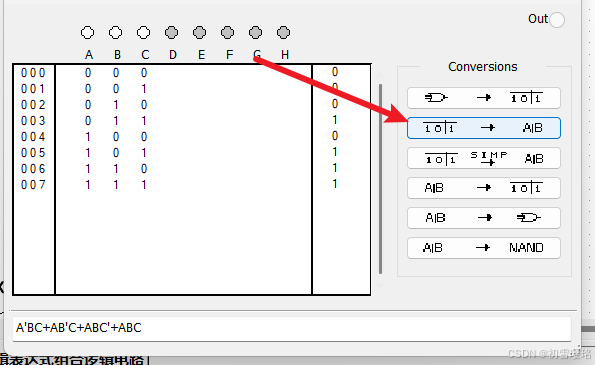

4. 生成逻辑表达式

-

点击

真值表 → 表达式按钮。

结果如下:A'BC+AB'C+ABC'+ABC

【注】上述六大功能表为大家总结如下:

2. 六大核心功能解析

| 按钮图标 | 功能描述 | 典型用途 |

|---|---|---|

| !第一个 | 电路→真值表 | 从电路转为真值表 |

| ![第二个 | 真值表→表达式 | 从真值表生成原始逻辑式 |

| ![第三个] | 真值表→最简表达式 | 自动卡诺图优化 |

| ![第四个] | 表达式→真值表 | 从表达式生成真值表 |

| ![第五个] | 表达式→与或门电路 | 生成仅用与或非门的电路 |

| ![第六个] | 表达式→ NAND电路 | 生成仅用NAND门的电路 |

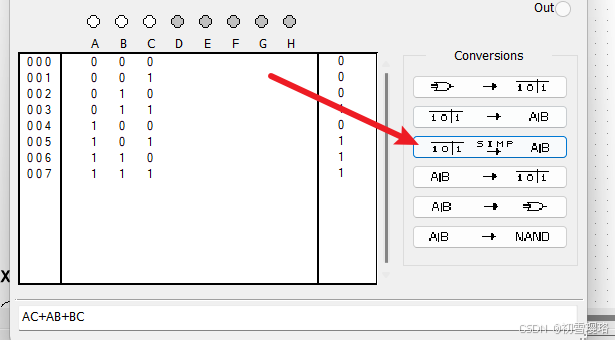

5. 表达式化简

-

点击

化简按钮(图标:SIMF)。

-

优化后表达式:

AB + AC + BC(最简与或式)。

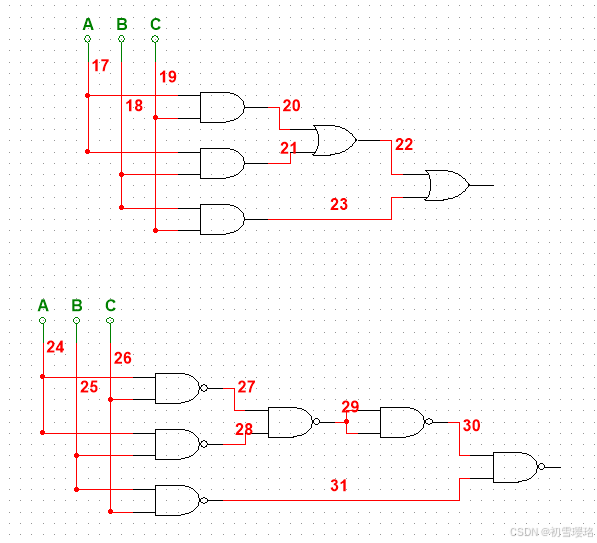

6. 生成电路图

-

点击

表达式 → 电路按钮(图标:E→NAND,可选与或门/NAND等)。 -

选择门类型:推荐 AND-OR(直接生成与或门组合)。

-

自动生成电路:Multisim会在工作区生成如下电路:

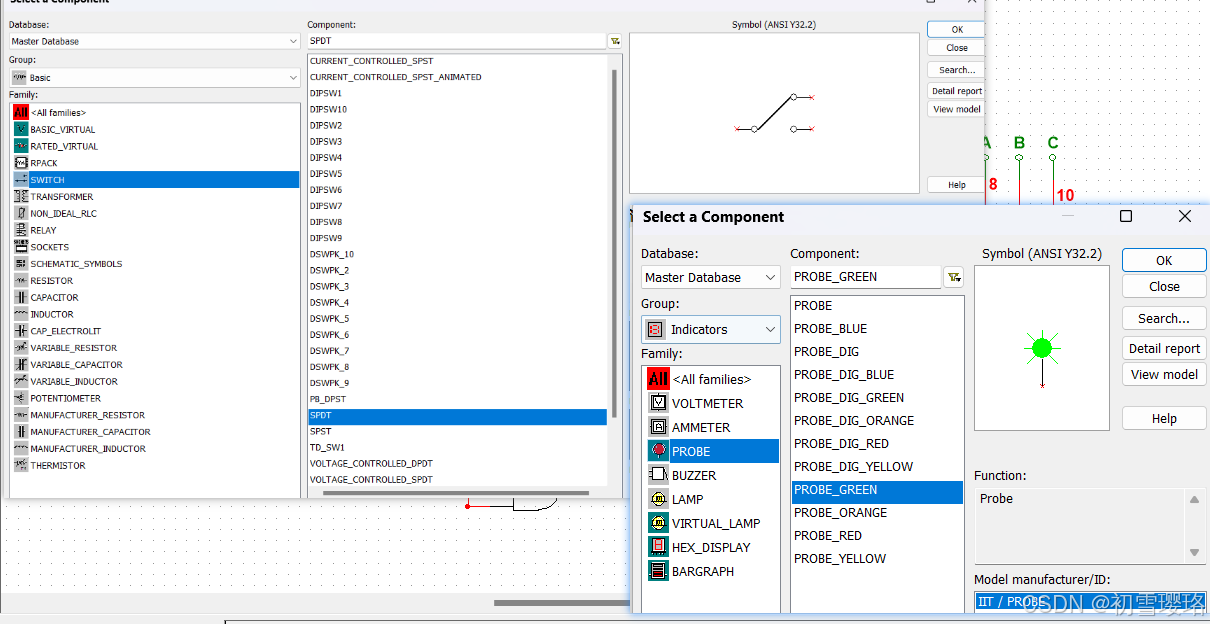

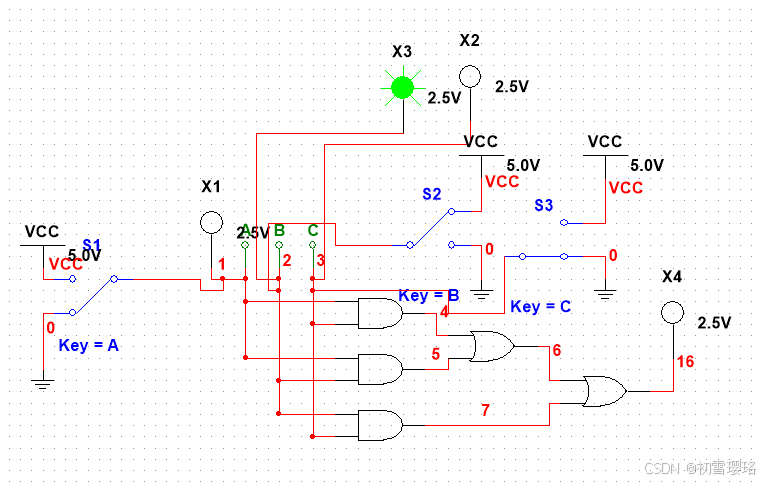

7. 仿真验证

-

添加输入双掷开关(A/B/C)和输出指示灯(Probe)。

[注]:其中双掷开关在basic的switch中,输出指示灯可以用indicators(指示器)中probe(探测)来检测0/1

切换输入组合,观察输出是否符合真值表。最终仿真结果如下:

三、注意事项

⚠️ 输入顺序:真值表按二进制顺序排列(000, 001, 010…)。

⚠️ 表达式优化:化简前检查是否勾选 Minimized 选项。

⚠️ 门电路替换:若需特定门(如全用AND),可手动替换并验证功能。

四、扩展应用

- 快速设计编码器/译码器

- 组合逻辑竞赛题秒解

- 数电实验报告救急,也可以用来偷懒,直接生成化简后的表达式

动手试试吧!从此告别卡诺图头秃~

如有问题欢迎留言,下期预告:Multisim时序电路仿真技巧!

原创声明:本文首发于优快云/知乎,转载请注明出处。

4686

4686

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?