面向可靠数字电路设计的选择性触发器优化

摘要

偏置温度不稳定性(BTI)和电源电压波动等运行时变异性源会影响超大规模集成电路电路中触发器的时序和功能。本文提出一种通过优化触发器以增强对老化和电源电压波动抗扰性的方法,从而提高超大规模集成电路电路的时序和可靠性。在所提出的选择性可靠性优化方法中,我们首先扩展标准单元库,添加针对严重BTI影响和/或电源电压波动具有更强抗扰性的优化触发器版本。然后,通过将电路中的老化关键和电压降关键型触发器替换为可靠性优化的版本,在成本效益较高的前提下提升整个电路的时序和可靠性。仿真结果表明,在处理器中引入优化的触发器后,与原始设计相比可将处理器寿命延长36.9%,从而实现更高的可靠性。该方法带来的漏电开销极小(处理器上低于0.1%),且无面积开销,便于集成到标准VLSI设计流程中。

索引词

可靠性,触发器,老化,偏置温度不稳定性(BTI),电压降,IR压降

一、引言

现代超大规模集成电路电路受到多种工艺和运行时变异性的影响[1]。其中,电源电压波动以及由偏置温度不稳定性(BTI)引起的晶体管老化是最主要的因素[2]–[4]。它们通过增加延迟来降低超大规模集成电路电路的性能,并因此缩短电路寿命。

BTI老化机制包含两个阶段:应力阶段,在此期间晶体管的阈值电压逐渐升高;以及恢复阶段,在此期间阈值电压降低至其原始值。由BTI引起的阈值电压偏移是温度、电源电压和应力占空比1的强函数。应力占空比是节点信号概率(SP)(即逻辑“1”的出现概率)的函数。因此,BTI会随着时间推移恶化电路的原始时序,并最终可能导致时序违规[5]。电源电压波动是由VLSI组件在运行时的固有功耗波动引起的,主要包括两个因素:IR压降和di/dt噪声。IR压降是由于电流流经电源分配网络(PDN)中的寄生电阻所导致的电压降,而di/dt噪声这是由于电源网络的电感和电容特性所致。由于数字门电路的延迟与电源电压成反比,瞬态电压降可能导致供电电压紧急状态,使电路在安全工作范围之外运行[6],[7]。

电压降和老化对触发器和锁存器等时序元件的影响显著。由于触发器具有内部反馈结构等特殊性,触发器中晶体管的退化以及电源电压波动可能导致严重的时序退化,甚至功能失效(无法捕获输入信号,无论其时序如何)[5]。此外,在电路综合过程中,为了实现最佳性能、面积和功耗,电路路径的延迟被平衡处理,使得几乎所有触发器的时序都处于关键状态。因此,有必要在设计阶段采用相应技术来考虑并控制逐渐发生的退化和失配问题,例如通过增加适当的时序裕量(老化和电压降保护带)以及引入缓解技术[8],[9]。

在典型的数字设计(如微处理器)中,根据各个组件的功能,某些触发器会在静态或近静态BTI应力下运行,而与工作负载无关。这些触发器会经历显著的时序退化,因为触发器输入SP非常接近0.0或1.0。由于受到严重的BTI应力,上述触发器退化更快,从而迫使整个电路采用较大的老化保护带。触发器还会经历较大的时间局部化电压降,因为它们与时钟边沿同步,并且理论上在同一时刻(时钟边沿)工作,因此会汲取大量电流,导致PDN[7]上的电压降显著增加。此外,最近的研究表明,随着工艺缩放,电压降的影响变得更加严重[4],[10]。因此,在传统的设计流程中,需考虑昂贵的电压降时序保护带来确保可靠电路操作[7]。

在这方面,已提出一些方法来应对老化和电压降对触发器的影响[11]–[14]。例如,[13]提出了一种通过调整晶体管尺寸来改善在不同工作条件(如温度和电压)下触发器可靠性的方法。这些研究大多针对动态BTI应力条件下的触发器进行优化,而静态BTI条件下的触发器则大多被忽视。正如我们将在本文后续部分所示,传统的优化技术(如功耗‐延迟积(PDP)或能量‐延迟积(EDP)的优化)无法有效解决此类应力下触发器的延迟增加问题。目前已有一些技术用于降低电压降对超大规模集成电路电路的整体影响通过在设计阶段偏移触发器的时钟输入,以降低时钟边沿[15],[16]处的峰值电流。然而,这些方法不适用于关键路径上时序裕量为零(或接近零)的触发器。在较高抽象层次上的技术,例如通过软件引导的线程调度[17]或电压紧急预测[6],也需在非电路级的其他抽象层次上引入额外开销,以应对电路级挑战。

本文针对在严重老化和电压降条件下触发器的时序退化问题,提出通过对这些触发器进行选择性优化来加以解决。我们首先通过晶体管尺寸调整对触发器设计进行优化,使其能够在严重老化和/或电压降条件下正常工作,并将优化版本添加到标准单元库中。然后,根据各个触发器实例的关键性,选择性地使用这些优化版本,以成本有效的方式提升整体系统可靠性。

在本文的初步版本[18],中,我们提出了一种技术,用于提高遭受严重BTI应力的触发器的可靠性。在此,我们通过进一步考虑电压降对触发器的影响来扩展所提出的方法。该方法的核心思想是识别出受高老化和/或电压降影响的时序关键触发器,并通过适当调整其晶体管的尺寸,选择性地重新优化这些触发器,使其能够在严重BTI应力和/或大电压降条件下正常工作。

将所提出的方法应用于处理器的仿真结果表明,采用该方法优化的触发器在引入不到0.1%漏电开销且无面积开销的情况下,表现出更小的延迟退化。根据结果,使用所提出方法的处理器相比原始处理器具有更小的时序保护带,从而实现了36.9%更长的寿命和更高的可靠性。

本文的其余部分组织如下。第二节回顾了关于触发器以及运行时变化影响的预备知识。第三节阐述了所提出的选择性触发器优化方法的动机。第四节介绍了触发器的单元级优化。第V节描述了所提出的电路级可靠性优化方法,第六节将展示该优化方法的结果。最后,第七节对全文进行总结。

II. 预备知识

A. 触发器时序指标

触发器时序指标(如建立时间(U)、保持时间(H)、时钟到输出延迟(DC Q)和数据到输出延迟(DDQ))在[19]中已有充分讨论。当建立时间足够大时,时钟到输出延迟值几乎保持恒定,但若进一步减少建立时间,该值将单调增加,直至达到某个数值,此时触发器无法捕获并锁存输入信号([19])。基于此,最佳建立时间被定义为使得时钟到输出延迟值从其最小值增加10%时的建立时间值([20])。

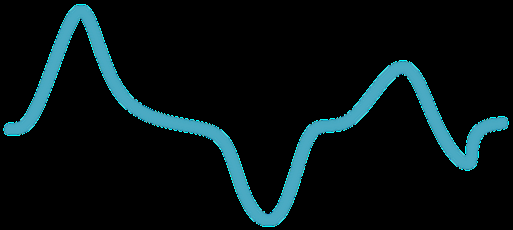

此外,每个触发器包含两条内部路径:一条用于将输入状态“零”传递至输出端,即高到低(HL)输入转换;另一条用于将输入状态“一”传递至输出端,即低电平到高电平(LH)输入转换。本质上,这两条路径的时序参数路径可能不同,如图1所示,这意味着LH和HL路径有两组时序参数:{ULH, DCQLH, DDQLH}用于LH转换,{UHL, DCQHL, DDQHL}用于HL转换。触发器延迟应被定义为无论转换类型如何,都能保证触发器的正确功能。因此,我们将触发器延迟定义为LH和HL两种转换中最差建立时间和最差时钟到输出延迟之和,如图1所示。最差建立时间确保输入信号在两种转换中都能被捕获,而最差时钟到输出延迟则确保信号能正确传播到触发器输出。

偏置温度不稳定性(BTI)

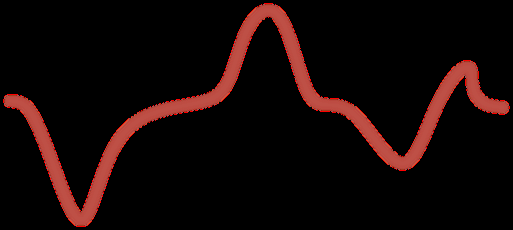

BTI的物理机制包含两个阶段:1)应力阶段,此时晶体管的阈值电压增加;2)恢复阶段,此时应力被移除,阈值电压逐渐恢复到其原始值。实际上,由BTI引起的阈值电压偏移(∆Vth)是应力占空比[21]的函数,如图2所示。当应力占空因子小于1.0时,晶体管频繁进入应力和恢复阶段(动态BTI);但当其等于1.0时,晶体管始终处于BTI应力下(静态BTI)。随着应力占空比从0.9向1.0增加,∆Vth迅速上升,因为恢复阶段变得非常短。因此,当晶体管处于静态或近静态BTI应力(即S‐BTI)时,老化对∆Vth的影响非常大,如图2所示。由于∆Vth更高,在此类S‐BTI应力下,电路的延迟退化可能显著增加。本文采用[21]中提出的模型来预测∆Vth。在我们的方法中,考虑了NBTI对PMOS晶体管的影响以及正偏置温度不稳定性(PBTI)对NMOS晶体管的影响。

C. 电源电压波动

由于工作负载执行期间的开关活动,电路组件在运行时汲取的电流会发生显著变化。从各个PDN节点汲取电流的空间和时间变化会导致接收节点处的电源电压波动。换句话说,由于变化的组件活动,电路门和触发器处的电源电压会发生波动。

当电压降超过某一阈值时,电路可能无法处于安全状态,从而导致时序错误。此类错误通常通过优化PDN来修复,例如在版图中加入去耦电容,并在电路的总时序裕量中考虑电压降时序裕量。

在现代工艺节点中,由于更高速度导致组件功耗的急剧变化,加剧了电压波动。此外,可用于优化PDN的资源更少。因此,进一步优化电路的其他部分以缓解电压波动影响变得愈发关键。例如,已在不同抽象层次提出了多种技术,通过限制组件功耗的变化[6],[17]或在更长的时间段内重新分配峰值电流[9],[15],来防止此类电压降。

III. 选择性触发器优化的动机

A. 运行时变化影响对触发器的影响

诸如电源电压波动、温度变化和晶体管老化等多种参数会影响电路中触发器的性能。虽然温度和电源电压等参数对触发器中的所有晶体管产生类似的影响,但输入SP对触发器中各个晶体管的影响则不同。这可能导致触发器中的晶体管因其应力占空比而产生非对称老化。因此,老化触发器内部低电平到高电平(LH)和高电平到低电平(HL)路径的延迟退化取决于输入SP[5]。图3a展示了C2MOS触发器[19],的原理图,其中LH和HL路径由两组独立的晶体管构成。属于这两条路径的晶体管的老化应力由输入SP决定。

图3b展示了老化C2MOS触发器[19]在不同输入SP下的LH和HL转换延迟。如图所示,当输入SP分别为0.0(SP0)和1.0(SP1)时,HL和LH转换的最严重延迟退化分别发生。此外,在这些条件下,S‐BTI非对称地改变了阈值电压,导致触发器的LH和HL路径老化不平衡。当触发器在SP0下老化时,LH路径的延迟略有增加,而HL路径的延迟显著增加。

电源电压波动对电路中触发器的影响取决于电路的工作负载变化和动态功耗。因此,每个触发器可能会经历特定程度的电压降。电压降引起的触发器性能退化非常显著,通常大于标准单元库中较简单的组合逻辑门的退化。图4比较了最高达10%的电压降对老化触发器和老化反相器延迟的影响。与无电压降情况相比,触发器的延迟增加了23.6%,而反相器的延迟增加了15%。

此外,电路中的触发器通常比组合逻辑门经历更大的电压降[23]。由于触发器在时钟信号的上升沿(或下降沿)处发生时间上集中的开关动作,导致在同步的时钟边沿从电源网络汲取的瞬态电流相对较高。这会在时钟边沿产生较大的电压降,此时触发器正在处理其数据输入信号。在时钟周期的其余部分,当组合单元处于活动状态时,该峰值电流消耗会逐渐减弱。因此,在本研究中,我们重点解决电压波动对触发器的影响。

时空温度变化也会影响电路性能。时间温度变化可能相当大2,并且一直是研究人员关注的焦点,因为它会严重影响超大规模集成电路电路的可靠性。研究表明,在110◦C的温度变化下,电路性能可能改变高达10%。时间温度变化会对电路延迟产生显著影响。然而,它对所有电路单元(即门电路和触发器)的影响是相似的。因此,所有路径上观察到的由温度引起的延迟退化程度也类似。因此,此类时间温度变化通过根据最差温度角(通常处于高温)调整电路时序来加以应对。

片上空间温度梯度对芯片晶粒上的电路组件施加了不同的应力。基于仿真[25],[26],传感器测量[27],和热像仪[26]的片上空间温度差异据报道最高可达∼20◦C。然而,与时间温度变化相比,空间温度变化的影响较小。由于这种空间温度梯度导致的核心触发器延迟退化总体差异预计小于2%(根据[24],[28],每40◦C大约引起延迟变化的4%)。因此,与电压降[29]的影响相比,温度梯度不会在电路路径的延迟之间造成显著差异,空间温度变化的影响通常被认为可以忽略不计。总体而言,相较于温度变化,测量和缓解电压降的影响要重要得多。

电压降和老化共同影响导致触发器性能显著退化。例如,一个在设计阶段通过平衡高到低(HL)/低到高(LH)延迟而优化的新触发器,在SP0条件下由于10%电压下降和5年老化的共同作用,其延迟从98.5皮秒增加到165.7皮秒,相当于延迟增加68%。如果此类触发器位于电路的关键路径上,则必须考虑可靠性约束,施加较大的时序保护带来实现时序收敛。由于电压降与老化共同影响远大于片上温度梯度的影响,本文仅关注超大规模集成电路电路中老化和电压降的影响。因此,有必要在设计阶段识别此类触发器,并针对这些条件下的工作进行优化。

选择性触发器优化的意义

在设计合理的电路中,电路路径的延迟在综合过程中得到平衡。因此,许多触发器位于电路关键路径上,属于时序关键触发器。研究表明[18],[23],在超大规模集成电路电路中,一些触发器受到严重的静态BTI影响,导致随着时间推移出现显著的时序退化。此外,电压降对触发器的影响可能非常大,因为特定时间(例如正时钟边沿)或电路布局上特定位置的局部功耗结果。

S‐BTI和电压降对触发器产生的巨大影响会显著降低电路的可靠性,特别是当这些触发器为时序关键型时。为了研究在典型数字设计中出现此类情况的可能性,我们采用第V节中提出的流程,通过在Leon3处理器上运行六个MiBench工作负载(即字符串搜索、快速排序、基础数学、位计数、快速傅里叶变换和crc32)[30],提取Leon3处理器中触发器的电压降和老化情况。为了保证公平性,我们排除了那些未被所用工作负载激活的部分中的触发器,例如中断处理程序、定时器和UART控制器。Leon3处理器的综合后的网表包含2,352个触发器,但本节中展示的结果仅包含1,686个触发器,这些触发器属于所有所用工作负载均能激活的部分。

图5展示了上述1,686个触发器的输入SP分布。结果显示,181个触发器(29个触发器)的输入SP值始终为0(始终为1)。我们的分析表明,具有此类行为的触发器通常属于错误检查与异常处理寄存器或地址寄存器的高位,这些位由于执行指令的时间和空间局部性而保持恒定。此外,大量触发器的SP值非常接近0.0或1.0。请注意,图5中报告的结果是六个所用工作负载的平均值,因此SP=0或SP=1的触发器在所有执行的工作负载中均表现出这样的SP值。在[31]中已进行了类似的实验以研究实际系统中的工作负载的影响,结果表明某些触发器在不同工作负载下始终处于S‐BTI状态。

与老化这种随时间推移而显现的缓慢现象不同,电压降具有快速瞬态特性。因此,在工作负载执行期间的任何时刻都可能出现较大的电压降。因此,有必要将所有工作负载执行过程中的最大电压降作为评估指标,因为它最终会影响触发器的特性。图6显示了影响Leon3处理器触发器的最大电压降的分布情况。为了生成该图,我们执行了多个工作负载,并提取了相应的电压降数值基于第V‐A节中提出的方法,计算触发器和门电路的电压降。然后,计算每个触发器在所有工作负载下的最大电压降。直方图中绘制的数值已归一化为电路中的最大电压降。因此,分布尾部右侧的触发器可能经历接近电路中最大电压降的较大电压降。

根据图5和图6的观察结果,一些触发器同时经历S‐BTI和高电压降,从而导致严重的退化。如果这些触发器位于处理器的关键路径上(即时序关键触发器),则这些触发器的退化应反映在电路的时序保护带上。这些触发器可根据电压降和老化的影响分为以下不同类别:

- 低电压降和低老化,

- 低电压降但存在S‐BTI老化(SP0/SP1)*

- 电压降较大但为典型老化*

- 高电压降和S‐BTI老化(SP0/SP1)*

正如我们将在本文(第VI‐F节)中展示的那样,在Leon3的时序关键触发器中,有92个触发器受到S‐BTI影响,31个触发器受到大的电压降影响。由于这些触发器位于电路的关键路径上,老化和电压降的影响可能会显著改变电路的时序,从而缩短其寿命并降低可靠性。因此,我们提出针对此类高退化条件(用*标记)专门生成优化的触发器,并将其添加到标准单元库中。通过第V节中提出的流程,我们确定这些高退化且时序关键的触发器,并将其替换为优化版本,以改善电路的时序和可靠性。

IV. 面向可靠性的触发器设计

在典型的可靠性感知电路设计中,应考虑元件在变异影响下的延迟,以确保电路在预期寿命期间的正确功能。因此,时序关键触发器的较大延迟退化会带来较大的时序保护带。在我们所提出的方法中,针对老化和电压波动等应力条件创建了触发器的优化版本,并且仅在触发器为时序关键并受到此类应力条件影响时才使用这些优化版本,以避免不必要的过度设计。这意味着在单元库中,我们通过优化触发器的晶体管尺寸调整,添加了以下触发器的抗干扰版本:

- 针对不同老化角(SP0和SP1)优化的抗老化触发器,

- 抗电压下降触发器,经优化可在电压波动下具有较低的性能退化,

- 抗老化和抗电压下降触发器。

A. 抗老化触发器设计

当触发器的LH和HL路径的初始延迟被设计为相近时(如图7中的实线所示),退化速率较高的路径最终将成为主导路径,并决定触发器的总延迟。在这种情况下,随时间推移会观察到触发器特性的显著老化。另一方面,如果退化速率较高的路径在初始时(通过设计)比退化速率较低的路径更快,则主导路径将是较慢的路径,因此较快路径的较高退化速率被掩盖。结果,触发器的整体老化将相当小。如图7中虚线所示的优化触发器即表现出此类特性。优化触发器的老化后延迟将增加∼10 ps,远低于原始触发器延迟∼40 ps的增加。我们利用此方法来设计抗老化触发器。

为了降低触发器整体受到的BTI引起的老化,我们所提出的方法通过重新调整HL和LH路径的晶体管尺寸,使触发器在老化后状态下的HL和LH路径延迟达到平衡。换句话说,该方法增加了退化速率较低的触发器内部路径的初始延迟(t= 0),以补偿老化后触发器的整体退化。尽管优化触发器的初始延迟可能比原始触发器的初始延迟略大,但考虑到老化引起的时序裕量,优化触发器的整体延迟将小于原始触发器,因为其老化速率要小得多。

请注意,该方法仅针对特定的SP(SP0或SP1)减少退化,但不可避免地会加剧该SP对角条件下的老化(SP0的对角条件是SP1,反之亦然)。例如,如果我们优化了对于SP0的触发器,如果优化触发器在SP1下工作,其退化会高得多。然而,由于S‐BTI下的这些触发器的SP由电路结构和功能决定,因此不会在其他SP对角条件下工作。因此,我们仅针对其中一个对角条件(SP0或SP1)进行优化。这意味着我们有意牺牲因电路特定功能而永远不会出现的对角条件,以获得更大的改进。

B. 抗电压降触发器设计

尽管老化会根据输入信号概率影响每个触发器晶体管,但触发器的电源电压下降会以相同的方式减缓所有触发器晶体管的速度。然而,对特定晶体管进行轻微的尺寸调整可以补偿触发器时序中的退化。因此,我们评估触发器在电压降影响下工作时的延迟,并优化触发器以改善延迟。因此,优化触发器将以更高的功耗为代价获得更好的时序性能。

C. 抗老化和抗电压降触发器设计

由于S‐BTI和电压降导致的触发器时序退化非常严重。这种时序退化可能无法通过在触发器面积内重新调整晶体管尺寸来有效补偿,而无需增大整个触发器的尺寸。因此,除了针对老化和电压降影响下的更好时序进行优化外,我们允许优化算法将触发器的面积增加一小部分。请注意,在这种情况下,可能需要额外的工程变更单(ECO)来用优化后的触发器替换原始触发器。然而,由于仅存在少量触发器受到此类退化影响,因此对布局执行工程变更单(ECO)不会成为问题。

D. 触发器弹性优化问题建模

在特定工作条件(包括温度、电压和输入SP)下,触发器的延迟可以表示为晶体管宽度的函数:

$$

delay= f(W), W=[wi] , (1)

$$

其中[wi]是包含触发器晶体管宽度的向量。此处,delay是在变化影响下的触发器传播延迟(数据到q),可能是S‐BTI应力、电压降,或根据优化方法而定的两者。

延迟函数f是晶体管宽度的一个复杂函数。我们针对不同尺寸调整的触发器实验结果表明,f无法用任何通用的闭式函数表示。因此,必须采用精确的SPICE仿真来提取延迟f(W)。同样,对于给定尺寸调整W的触发器漏电功耗,即表I中的power(W),也应基于SPICE仿真提取。提取触发器的延迟和功耗需要进行多轮SPICE仿真。我们使用Cadence Virtuoso Liberate[34],,其内部执行SPICE仿真,以对触发器进行表征并获得其延迟和功耗。

由于每次触发器表征的计算成本都很高,因此通过穷举搜索来找到最佳尺寸调整W是不可行的。因此,有必要采用优化技术,在有限的触发器表征次数内获得最佳的W。因此,我们采用序列二次规划(SQP)方法,这是一种非线性规划技术[32]。SQP在优化目标和约束均为二阶可微分的受约束连续非线性问题方面非常高效。触发器的延迟函数和功耗函数具备这些特性。因此,SQP是一种通过有限次函数评估即可高效求解该问题的方法。在SQP中,该问题被转化为二次子问题,并通过迭代求解以逐步改进尺寸调整。为此,我们采用一种迭代方法,旨在最小化方程(1)的延迟。给定初始尺寸后,延迟函数f被近似为一个二次函数:

$$

f(W) ≈ f(W0)+▽f(W0)^T ·(W − W0) + \frac{1}{2}(W − W0)^T · Hf(W0) ·(W − W0),

$$

其中▽f(W)和Hf(W)分别为延迟函数f的梯度和海森矩阵。在本节后续将讨论的一些约束条件下,对公式(2)的二次近似进行最小化,可得到优化的晶体管尺寸。然后,将获得的尺寸作为初始尺寸,并启动新一轮迭代。此循环持续进行,直到优化达到所需精度,即两次连续迭代的优化延迟之间的差值小于预定义阈值ǫdelay。因此,求解器将继续检查结果延迟的精度:

$$

|delay_{i−1} − delay_i| < ǫ_{delay} (3)

$$

其中$delay_i$表示第$i$次迭代的延迟。

使用二次近似的另一个原因是,线性问题的最优结果始终位于边界上,而二次问题的最优结果可以是边界内的任意点,也可以是边界本身。在第六节中,我们将证明最优结果不一定位于边界上,因此需要采用非线性规划技术来寻找更优的结果。表I总结了该优化问题。

| 参数 | |

|---|---|

| 初始猜测 | $W_0=$优化$W$以用于PDP(新鲜的) |

| 约束 | $w_i ≥ w_{min}$ $\sum_{1}^{n} w_i ≤(1+λ)\sum W_0$ 功耗$(W) ≤(1+ β)$ power$(W_0)$ |

| 目标 | 最小化: $f(W)$ $w_{min}$最小尺寸 |

| 常数 | $λ, β$可接受的过度面积和漏电流 |

$W=(w_1, …, w_n)$

对优化问题施加了多个约束,涉及晶体管尺寸、触发器面积和漏电流。第一个约束如表I所示,限制了晶体管的最小尺寸。第二个约束限制了优化触发器的面积。在针对S‐BTI或电压降进行优化时,我们考虑$λ= 0$,以使优化触发器的面积保持在原始触发器面积范围内,这也有助于使宽高比几乎等于原始触发器的宽高比。这样,优化触发器可以在无需修改电路级版图的情况下轻松替换原始触发器。这是通过限制晶体管宽度的总和$w_i$来实现的。然而,我们假设$λ> 0$用于同时受S‐BTI和电压降影响的触发器,以更好地补偿延迟退化。第三个约束通过参数$β$为触发器的过度泄漏设置上限。无论触发器是否受到变异影响,该约束均适用,以确保在这两种情况下都能实现低漏电操作。优化的初始猜测$W_0$是初始状态下最小PDP的最优尺寸调整。

E. 可靠性感知的触发器优化流程

图8展示了我们提出的可靠性感知优化流程。对于给定的输入SP,首先通过SPICE仿真计算所有晶体管的SP。随后,根据提取出的晶体管SP以及触发器的工作角(如温度和电源电压),获得所有晶体管的BTI引起的阈值电压偏移(∆Vth)。然后将∆Vth值反向标注到原始触发器网表中,并生成老化触发器网表。

在每次SQP迭代中,都会创建并求解二次子问题,以生成进一步改进的触发器尺寸。该优化方法使用Python实现,并通过scipy库调用触发器表征工具。延迟函数$f(W)$的梯度通过执行$n+1$次触发器表征得到线性近似(其中$n$为晶体管数量)。海森矩阵$H_f$也基于相同的仿真结果,利用割线方程对梯度计算进行近似,类似于Broyden–Fletcher–Goldfarb–Shanno(BFGS)算法[33],因此无需额外的仿真。这有效地减少了构建所需触发器表征的次数公式(2)中解释的二次子问题到$n+1$。SQP优化器由于表I中的漏电流功耗约束,也需要进行触发器表征。然而,这种情况并不频繁,因此不会带来大量的仿真。在我们的实现中,还采用了本地缓存以防止冗余(重复)的触发器表征。

每当需要对给定的$W$进行触发器表征时,尺寸调整$W$会被反向标注到先前提取的老化触发器网表中,并生成具有该尺寸调整的新老化触发器。然后使用Cadence Virtuoso Liberate[34]提取其延迟和功耗。当改进步足够小且满足公式(3)中的条件时,SQP方法终止,并将最后一次的尺寸调整作为该问题的最优解返回。在我们的仿真环境(见第VI‐A节)中,SQP仿真通常在6次迭代内结束,最多进行180次表征。

由于该过程可以在任何特定的电源电压(Vdd)下执行,因此当给定的电源电压包含了电压降的影响时,它本质上也可用于优化电压降。通过考虑输入SP为0.5,我们还可以为典型老化创建抗电压降干扰的触发器版本。因此,我们针对这些条件执行图8所示的流程,以在假设电源电压为Vdd且最大电压降为R%的情况下,创建抗干扰版本的触发器。

| 电源电压(V) | 老化条件 | 老化 | Vdd | S‐BTI(SP0, SP1) |

|---|---|---|---|---|

| 电压降: $(1 − R)Vdd$ | 100 | 典型老化(SP=0.5) | ||

| 老化和电压降: $(1 − R/100)Vdd$ | S-BTI(SP0, SP1) |

F. 技术和单元版图对触发器优化问题的影响

第IV‐D节中提出的触发器优化问题是连续优化问题。在实际中,晶体管尺寸的分辨率受限于光刻工艺的分辨率(取决于光学、蚀刻等多个参数)。因此,可制造的晶体管宽度通常是以光刻工艺分辨率为步长的离散值。尽管存在这种制造限制,仍然可以在连续空间中求解该优化问题而不损失通用性。这种方法的优势在于,可以通过计算导数来评估触发器参数对晶体管宽度变化的敏感性,并采用如序列二次规划(SQP)等连续空间方法,实现精确且快速的收敛时间。在此方法中,优化方法得到的尺寸结果需要根据制造限制进行离散化处理。为此,将优化结果中获得的晶体管的宽度四舍五入到最接近的可制造尺寸。

可以根据应用需求以多种方式创建优化的触发器的版图。在标准单元设计流程中,单元布局具有离散高度,该高度是水平网格间距[35]的倍数。在此流程中,通过扩展多晶硅和有源区重叠或通过晶体管的并联连接来创建不同宽度的晶体管。因此,晶体管可以垂直或平行于电源网格线(或在大尺寸晶体管中沿两个方向)进行扩展。在适用时通过共享晶体管的漏极/源极并利用欧拉路径理论[36],可以获得高度优化的版图。此外,还有关于阱、多晶硅和布线轨道之间间距的设计规则。因此,在最终设计完成之前,要准确估算触发器面积非常复杂。

在所提出的方法中,由于电路拓扑结构未发生变化(仅改变晶体管的尺寸),原始触发器设计的示意图可被重复利用,以降低单元布局设计的复杂性。我们还通过将宽度的总和纳入表I中的面积约束,简化了面积估算,即:

$$

\sum_{1}^{n} w_i ≤(1+ λ)\sum W_0.

$$

可以采用更复杂的面积约束近似方法,例如加权求和。只要该约束可导至二阶,就可以在所提出的方法中使用该约束。

V. 选择性可靠性优化

本节解释了如何利用第四节中的优化触发器来提高电路的可靠性。其思路是找出受S‐BTI和/或电压降影响且对电路可靠性具有重要影响的触发器,即时序关键触发器,并将其替换为优化版本。这种选择性可靠性优化的原因在于,具备可靠性感知的触发器优化在每个触发器上的漏电开销较高。因此,为了实现高性价比,仅应对经历S‐BTI和/或显著电压降的时序关键触发器进行替换。由于这些触发器仅占设计中所有触发器的一小部分,所提出的方法能够以高性价比的方式减少整体时序保护带。

我们所提出的 选择性可靠性优化 方法的整体流程如图9所示。该流程利用了超大规模集成电路设计流程中的综合和布局布线步骤的结果,由以下两部分组成:I) 老化与电压降分析 和 II) 选择性触发器替换步骤。该优化流程通过更新门级网表和电路布局,以提高电路在电压降和老化影响下的可靠性。该优化方法的输出结果可继续用于后续的VLSI设计流程中。因此,所提出的方法对VLSI设计流程是透明的,并且可以轻松地集成到其中。

A. 老化与电压降分析

在此步骤中,利用VLSI设计流程中的综合和布局布线步骤的结果,来识别老化关键、电压降关键和时序关键的触发器。

老化关键型触发器是指处于S‐BTI影响下的触发器。为了找出老化关键型触发器,我们需要提取触发器的SP。因此,我们运行一些典型工作负载进行门级仿真。典型工作负载是指通常在电路上执行的工作负载片段。门级仿真的结果是电路内所有网络的电压变化转储(VCD)。基于这些信息,我们可以收集所有触发器的SP,并确定老化关键型触发器。

电压降关键型触发器是指那些随时间受到较大电压降影响的触发器。需要指出的是,触发器的最大电压降是判断其是否为电压降关键型触发器的指标。电路中的瞬态电压降会根据电路组件的功耗特性动态变化。电路组件的动态功耗特性可以从VCD报告中提取。我们基于电路组件的功耗特性和电路的布局与封装来估算电路中的动态电压降,该估算考虑了电压波动中的电阻和电感成分。通过评估每个单元(门电路、触发器等)在不同时间和不同工作负载下的最大电压降,生成电路的电压降分布图。由此,我们得到各个触发器在时间过程中所经历的最大电压降量,并据此提取出经历较大电压降的触发器。

此外,使用门级仿真结果进行电压降和老化感知的时序分析,以获得在变异性影响下电路路径的延迟。我们通过考虑与电压降相关的信息,扩展了[37]中的老化感知时序分析。具体方法是在两种不同的电源电压下对单元进行表征:标称 Vdd以及考虑最大电压降后的电源电压 $(1 − R/100)Vdd$。然后,针对门级网表中的每个门电路/触发器,根据该门电路上的电压降大小,我们在标准单元库中对应两个电源电压值的条目之间进行线性插值,以获得相应的时序信息。在线性电源电压有限变化的假设下,线性插值是一种有效的方法,如图4所示。对于更剧烈的电压波动,可能需要对若干中间供电电压值的标准单元库进行表征,并采用分段三次埃尔米特插值多项式(PCHIP)方法。据此,我们找出时序关键触发器,这些触发器是考虑变化影响后电路的关键路径或近关键路径的一部分。

B. 选择性触发器替换

第V‐A节中提出的老化与电压降分析步骤引入了三组触发器,即时序关键触发器(T C)、老化关键型触发器(AC)和电压降关键型触发器(V C)。在选择性触发器替换步骤中,我们将同时属于老化关键和/或电压降关键的时序关键触发器替换为针对这些老化和/或电压降条件优化的版本。这类触发器仅占整体的一小部分。然而,此类选择性触发器替换可能会改变电路的整体版图、时序和功耗,因为原始电路触发器的尺寸、时序和功耗可能与被替换的触发器不同。因此,所提出的选择性触发器替换是一个迭代过程,在每次迭代中将若干触发器替换为优化版本,该迭代过程持续进行,直到不再需要将任何触发器替换为优化版本为止。

在第 $i$次迭代中,我们假设根据时序分析结果,电路延迟为 $D_i$,且 $d_{ij}$ 是终止于第 $j$个触发器的路径的最大延迟(包括该触发器的延迟)。因此,在每次迭代中:

1) 我们选择时序裕量值小于电路延迟 $k\%$的时序关键触发器,或者:

$$

FF_j \in TC; \quad \text{when} \quad d_{ij} \geq (1 - k/100)D_i \

j: \text{index of flip-flops}

$$

2) 在这些触发器中,那些同时也是老化关键和/或电压降关键的触发器将被替换为优化版本:

$$

FF_j \rightarrow FF_{j,opt}; \quad \text{when} \quad FF_j \in TC \cap (AC \cup VC)

$$

3) 执行试验性电压降和老化感知时序分析,并在考虑已替换的触发器的情况下确定电路延迟($D_{i+1}$)。

4) 我们可以通过比较 $FF_j$ 在优化前的路径延迟(即 $d_{ij}$)与第3步中获得的电路延迟(即 $D_{i+1}$),来确定替换 $FF_j$ 是否对电路时序产生显著影响。仅当 $d_{ij} > D_{i+1}$ 时,用优化后的 $FF_{j,opt}$ 替换 $FF_j$ 才是有利的。事实上,当 $d_{ij} < D_{i+1}$ 时,无需优化 $FF_j$,因为它对电路时序没有影响。因此,我们只需要将那些对电路时序有影响的触发器替换为优化版本。因此,仅当满足以下条件时,我们才保留 $FF_{j,opt}$:

$$

d_{ij} > r \times D_{i+1} \quad (4)

$$

不满足公式(4)的触发器将回滚到原始版本,以防止产生任何不必要的开销。请注意,我们还在公式(4)中考虑了比例 $r< 1$值,以补偿由于仿真引起的计算误差。

5) 电路的版图和门级网表已更新。只有在使用了更大的单元时,才会更新版图(特别是适用于第四节中所述的老化和电压降情况下的触发器)。

6) 如果在本次迭代中任何触发器被替换为优化版本,我们需要启动新一轮迭代,因为电路的时序和功耗规格已发生改变。这通过重新执行老化与电压降分析来实现。而门级仿真这一耗时的过程则无需重复,因为其结果不受触发器替换的影响。

上述流程将有限数量的触发器替换为优化版本,并为电路带来可忽略的开销。在我们的仿真中,该流程在几次迭代内即终止,因为电路布局、功耗和时序的变化并不显著。

VI. 优化结果

在本节中,我们基于仿真结果评估了所提出的处理器选择性可靠性优化的效率。

A. 仿真设置

我们将该方法应用于几种触发器拓扑结构,即 C2MOS锁存器、动态/静态单晶体管时钟锁存器(DSTC/SSTC)和半动态触发器(SDFF)[19]。这些触发器采用45nm体硅CMOS预测技术模型(PTM)晶体管实现[38]。所有触发器最初均在初始状态(原始设计)下针对最小PDP进行优化。所采用模型的老化参数经过调整,使得在SP=0.5条件下,经过5年老化后,扇出4(FO4)反相器的延迟增加10%。在进行延迟和漏电流测量时,触发器的输出负载设置为FO4,各单元在室温及不同电源电压下进行表征,电源电压范围为工艺节点标称电源电压的80%至100%。

我们使用Leon3处理器作为所提出方法的案例研究。我们使用Nangate 45nm开放单元库进行组合逻辑设计,老化假设与本节开头所述相同。该处理器使用Synopsys Design Compiler进行综合,并使用Cadence EDI进行布局布线。

我们在综合后的Leon3处理器上执行了各种MiBench工作负载,并提取了电压变化转储(VCD)文件。基于这些VCD文件,提取了每个节点的SP综合电路被计算,并使用Synopsys功耗编译器计算门电路和触发器的功耗。同时,使用VoltSpot工具提取处理器的电压降分布图[22],,该工具能够提取由电阻性(IR压降)和电感性(Ldi/dt)组件引起的电压降程度。

请注意,所提出的技术不限于特定的工作条件或触发器拓扑。接下来,我们将针对C2MOS触发器展示详细的结果与分析,然后简要讨论其他类型触发器的结果。随后,将研究所提出的方法带来的改进对过度泄漏的依赖性。在本节末尾,将展示使用优化触发器对Leon3处理器寿命的影响。

B. C2MOS触发器的详细优化结果

我们将第IV‐E节中提出的优化流程(见图8)应用于C2MOS触发器设计,以创建抗老化和抗电压降的优化触发器。为了生成C2MOS触发器的抗老化版本,我们允许优化器考虑漏电功耗比原始触发器最多高出25%的设计,即将表I中的系数 $\beta$设为0.25。此时,我们将触发器的面积限制为与原始触发器相同,即 $\lambda= 0$。请注意,整个电路的漏电功耗总开销可以忽略不计,因为设计中优化的触发器数量有限。例如,根据第三节‐B,若12.45%的触发器工作在S‐BTI条件下,且每个优化触发器的漏电开销小于25%,则这些触发器引入的漏电开销最多为3.11%(在考虑整个处理器设计时,实际开销要小得多)。通过允许最多20%的额外面积,可构建抗老化和抗电压降的C2MOS触发器版本。为此,我们假设 $\lambda \in {0, 0.1, 0.2}$分别对应0%、10%和20%的额外面积。利用额外面积,优化器能够为受老化和电压降影响严重的时序关键型触发器找到更优的设计方案。由于这类触发器非常稀少,但对整体处理器寿命和可靠性具有重大影响,因此适当增加面积以提升可靠性和寿命是值得的。

表II比较了原始C2MOS触发器的特性,包括建立时间(U)、时钟到输出延迟(DC Q)、数据到输出延迟(DDQ)、延迟和漏电流,以及三种不同的优化场景:

1) 老化后PDP,针对老化后状态下的PDP进行优化。

2) 所提出的方法(针对老化优化),其中触发器通过最小化老化后状态的延迟来优化其抗老化能力。可接受的额外面积和漏电流分别为0%和25%($\beta= 0.25, \lambda= 0$)。

3) 所提出的方法(针对老化+vdrop优化),其中触发器通过最小化老化后状态以及电压降影响下的延迟,来优化其对抗老化和电压降的抗扰性。可接受的额外面积和漏电流分别为20%和100%($\beta= 1, \lambda= 0.2$)。

表II中报告了在初始状态(无老化或电压降)、老化状态(在S‐BTI老化SP0条件下持续5年)以及aging+vdrop状态(在S‐BTI条件下老化5年且电源电压下降10%)下的优化结果。针对LH/HL转换,列出了建立时间、时钟到输出延迟和数据到输出延迟,并根据第二节‐A计算延迟。延迟退化是指设计在老化后状态相对于原始设计的初始延迟的相对延迟增加量(表中以粗体标出):

$$

\text{delay degradation} = \frac{\text{delay}

{\text{opt.,aged}} - \text{delay}

{\text{orig.,fresh}}}{\text{delay}_{\text{orig.,fresh}}} \quad (5)

$$

由于优化触发器将替换设计中对应的触发器,因此将延迟退化与原始触发器的初始延迟进行比较,以便更好地理解优化触发器的老化后延迟与原始设计的初始延迟的接近程度。

基本上,场景1与许多触发器优化工作(如[13],[14],)中提出的方法类似,因为它们都将能量和延迟的乘积(例如功耗‐延迟积(PDP)或能量‐延迟积(EDP))作为优化目标。场景1能够通过增加延迟并减少漏电流来有效降低PDP,但这可能导致S‐BTI角下的时序无法接受。表II显示,由于未将触发器延迟作为优化目标,PDP方法无法找到适用于S‐BTI角的最优抗老化尺寸调整方案。

如所示,对于原始触发器,LH和HL路径的初始延迟几乎相同(见DDQ,LH和DDQ,HL),但在老化后,HL路径比LH路径慢得多。这导致仅老化引起的延迟退化为35%,而当老化和电压降共同影响触发器时,延迟退化约为68%。当该触发器在场景1中进行优化时,延迟未能充分降低,因为主要关注的是PDP而非延迟。另一方面,在场景2(所提出的方法,仅针对老化)中,优化器调整尺寸以均衡LH/HL路径的老化后延迟,从而在满足约束条件的情况下实现尽可能小的老化后延迟(119.4 ps)。在这种情况下,老化后延迟相比原始触发器的初始延迟仅增加了21%。同时,漏电开销被限制在4.7%。由于该触发器工作在S‐BTI区域,动态功耗在总功耗中占很小一部分。因此,这些工艺角下的总功耗由漏电功耗决定。

对于仅受老化影响的触发器,场景2设计相比原始和最先进的[13]触发器设计要好得多。然而,10%电压降在此场景下导致49%的延迟退化,这是显著的。场景3的触发器优化结果表明,此类触发器对老化和电压降的影响均具有更强的韧性。这些触发器的漏电流消耗约增加53%,但在老化和电压降同时存在的情况下,延迟退化仅为32%。请注意,在此种条件下处于该状态的触发器数量非常小。因此,使用场景3优化的触发器对处理器功耗的整体影响可以忽略不计。

C. 其他触发器的优化结果

图10 提供了一组代表性触发器的优化结果。它比较了原始触发器和优化触发器在新鲜状态和老化后的延迟与漏电流。所有延迟值均归一化为相应原始触发器的新鲜延迟(C2MOS 为 114.8 ps,SDFF 为 28.5 ps,SSTC 为 71.0 ps)。

对于C2MOS触发器,所提出的方法在SP1处将延迟退化(公式(5))降低至11%,而原始设计的延迟退化为35%(提升了24%)。该触发器具有对称结构,意味着其在LH/HL转换中可实现平衡的时序(如图3b所示),而某些触发器结构(如SDFF)由于其内部结构的原因,总是在LH/HL转换中表现出不平衡的时序。例如,在SDFF中,HL转换的延迟总是小于LH转换的延迟。原因在于,当进行LH转换时,该触发器中的一个中间预充电节点必须放电,才能将输入的“1”传递到输出;而对于HL转换,则不需要这样的放电过程。因此,较慢的路径始终是LH 路径。如果与不均衡的老化耦合,可能会加剧老化。

对于这些触发器,优化器通过从较快路径尽可能多地占用面积并将其分配给较慢路径,以最小化较慢路径的延迟。对于 SDFF,这在 SP0 下会导致额外 15.8% 的漏电流,但能提高 S‐BTI 抗扰性。

D. 延迟‐漏电流权衡

为了探究额外泄漏与延迟之间的权衡关系,我们对一个C2MOS触发器进行了优化,设置了从0%到50%的多种过度泄漏量($\beta \in {0, 0.125, 0.25, 0.5}$)。如图11所示,通过允许优化方法设计具有更高漏电流的触发器,可以实现更低的延迟退化。然而,随着 $\beta$的增加,改进效果趋于饱和。因此,向优化器提供额外的泄漏仅在约25%以内是有益的,因为超过该值后延迟的改善不再显著。请注意,具有更宽松漏电流约束(即更高的 $\beta$)所设计的触发器不一定具有非常高的漏电流。如表II所示,在场景2(仅老化)中,优化触发器仅消耗4.7%的额外漏电流,却相比原始触发器和场景1(最先进的工作)提供了明显更好的抗 S‐BTI老化能力。

E. 延迟‐面积权衡

少量额外面积对触发器抗老化和电压降影响的抗扰性的作用通过改变参数来研究过大的面积开销 $\lambda$(见表I)。我们在第四节中运行优化流程,针对$\lambda \in {0, 0.2}$值进行,并将结果与原始触发器设计进行比较。根据图12所示的结果,无额外面积的触发器设计,即场景2,表现出良好的抗老化能力,但在10%电压降影响下,其延迟退化最高可达49%。在电压降影响下,具有20%额外面积的触发器设计表现出更优的特性,最大延迟退化为32%。这一观察结果证实,在老化和电压降影响均严重的情况下,使用具有20%额外面积的触发器是有利的。

F. 电路级结果

我们将第V节中提出的 选择性可靠性优化方法 应用于第VI‐A节所述设置下的Leon3处理器,以评估其对处理器时序和可靠性的整体影响。针对特定输出负载在初始状态下实现最小PDP的“原始触发器”设计进行了优化,而“优化触发器”设计则分别针对“老化”和“老化+vdrop”情况通过所提出的方法获得。因此,对于每个特定输出负载的原始触发器设计,均存在五个针对S‐BTI角SP0和SP1以及无电压降和最大电压降条件的优化设计(依据第IV‐E节)。

为了评估选择性可靠性优化的影响,我们使用所提出流程中的“老化与电压降分析”步骤提取并比较Leon3处理器的时序(见图9)。该步骤采用了一种改进的老化感知时序分析工具[37],该工具还考虑了第V‐A节中所述的电源电压变化影响。时序报告的结果确定了处理器在运行时变化影响下的处理器延迟。

图13展示了Leon3触发器在处理器布局上的时序,以及计算得到的电压降和老化对处理器时序的影响。所展示的图表均已归一化到最大值(最大电压降、最大延迟、最大老化),以便于可视化。因此,较高的值(较深的颜色)代表临界情况。图13a显示了使用“老化与电压降分析”提取的触发器的电压降。步骤。电压降值已归一化为仿真期间提取的最大电压降值。如图所示,在工作负载执行期间,许多触发器至少经历了中等程度的电压降。然而,版图左上角的触发器经历了严重的电压降。触发器的时序关键性也在图13b中显示。在此图中,时序裕量较低的触发器取值更接近1.0(颜色更深)。有趣的是,一些位于版图左上角的触发器也是时序关键的。此外,图13c展示了触发器的老化关键性。如图所示,许多处于S‐BTI下的触发器也是时序关键的。最重要的是,少数时序关键触发器同时受到老化和电压降的影响。

在此,我们将原始处理器(在应用所提出的方法之前)的时序与优化后的处理器的时序进行比较。原始处理器使用原始触发器设计进行综合。我们评估该处理器在运行时变化影响(老化和电压降)下经过7年后的延迟。然后,我们以两种模式应用所提出的选择性可靠性优化:I)仅考虑老化影响;II)同时考虑老化和电压降的影响。由此得到两个版本的优化后的处理器。在优化过程中,我们假设参数 $k= 15$和 $r= 0.90$(定义见第V‐B节)。因此,所有裕量值小于处理器延迟15%的触发器被视为时序关键触发器。在根据所提出的方法替换关键触发器后,再次通过“老化和电压降分析”步骤获得处理器延迟。

表III展示了处理器在初始状态(即无老化或电压降)以及在受到老化和电压降影响下的处理器延迟。结果报告如下:

1) 原始处理器:仅使用原始触发器;

2) 针对老化的优化处理器:在优化过程中仅考虑老化影响;

3) 针对老化和电压降的优化处理器:在优化过程中同时考虑老化和电压降的影响。

根据表格,使用原始触发器时,处理器延迟在7年后增加了9.97%。这相当于电路运行7年所需的 138.6ps时序保护带,即 $T_{clk} \geq 1528.2ps$。通过应用选择性可靠性优化并仅考虑老化影响所得到的优化后的处理器,在老化和电压降共同影响下的延迟更低 1494.8ps ,从而在7年运行期间将所需时序保护带减少了 33.4ps,进而优化了性能。此外,若将优化后的处理器与原始处理器的时序裕量($T_{clk} = 1528.2ps$)配合使用,则该方法中优化后处理器的退化速率使其可运行9.2年(寿命提升30.8%)。最后,若处理器针对老化和电压降影响进行了优化,则与原始处理器相比,所需时序保护带进一步减少了 41.5ps。在这种情况下,处理器的寿命提升了36.9%(9.6年)。

表III中实现的改进原因由图14解释。在此,我们仅绘制了处理器延迟时序关键触发器的延迟,这些触发器的裕量小于处理器延迟的15%(在老化和电压降影响下)。基于此假设,共有261个时序关键触发器。在这些时序关键触发器中,有92个触发器受到S‐BTI影响(即 $0 \leq SP< 0.01$或 $0.99< SP \leq 1$)。此外,有31个触发器是电压降关键的,经历至少50%的电路最大电压降。因此,将它们替换为优化版本可减少整体延迟退化,并改善最关键部分的延迟。

由于所提出的方法中替换的触发器数量限制在212个触发器以内,因此该方法的整体漏电流开销小于0.3%。此外,由于被替换的触发器大多处于S‐BTI影响下且很少切换,动态功耗开销几乎可以忽略不计。因此,整体功耗开销小于0.1%。根据电路中所有单元面积的总和计算得出的面积开销也微乎其微,因为只有43个触发器被替换为加大尺寸版本(面积开销小于0.1%)。ECO流程通过轻微移动其他单元即可轻松将这些触发器集成到现有布局中,而无需改变芯片尺寸。请注意,电压降和老化对驱动逻辑路径的影响远小于对触发器的影响。因此,这些路径的退化速率要低得多。

| 处理器延迟 初始状态下的 | 7年后 +电压降 | 退化延迟 | 保护带减少 | 寿命改进 | |

|---|---|---|---|---|---|

| 使用原始触发器 | 1,389.6 皮秒 | 1,528.2 皮秒 | 9.97% | – | – |

| 选择性可靠性优化 (仅老化) | 1,391.3 皮秒 | 1,494.8 皮秒 | 7.44% | 33.4 皮秒 | 30.8% |

| 选择性可靠性优化 (老化和电压降) | 1,379.7 皮秒 | 1,486.7 皮秒 | 7.75% | 41.5 皮秒 | 36.9% |

七、结论

超大规模集成电路电路的性能和可靠性受到电源电压波动和偏置温度不稳定性(BTI)等运行时变异性源的影响。电路触发器中可能有相当一部分会受到严重BTI或大的电压降影响,从而导致时序和功能故障。因此,需要对这些触发器进行单独处理,并采用特定的抗应力设计,以提高可靠性和寿命。本文提出了一种选择性可靠性优化一种选择性优化在严重BTI应力和/或电压降条件下工作的触发器的方法。所提出的优化流程通过调整触发器晶体管尺寸来获得变异性弹性单元。利用开发的考虑变异的静态时序分析工具确定受老化和/或电压降影响的电路触发器,并将其替换为能够更好承受老化和电压降影响的优化触发器。仿真结果表明,所提出的选择性可靠性优化方法可减少Leon3处理器时序保护带,并将处理器寿命提高36.9%,同时漏电开销低于0.1%,且无面积开销。

1514

1514

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?