板卡型号:MA703FA开发板调试

FPGA主控芯片型号:XC7A35T-FGG484

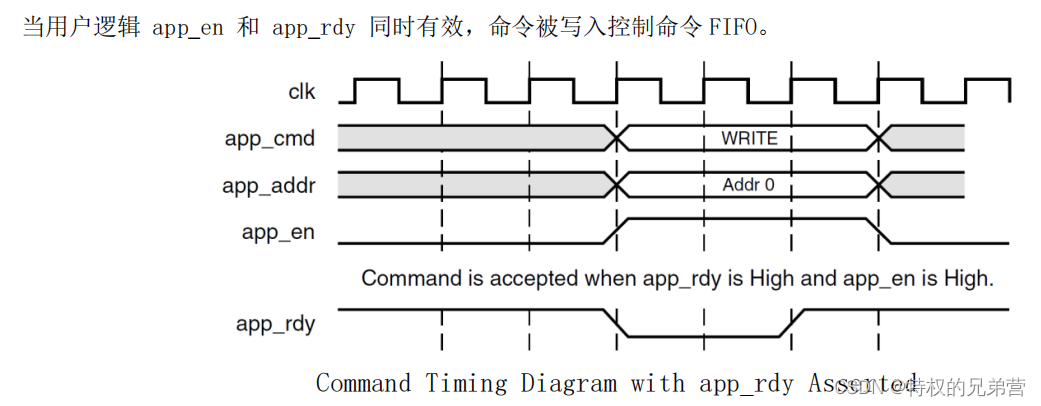

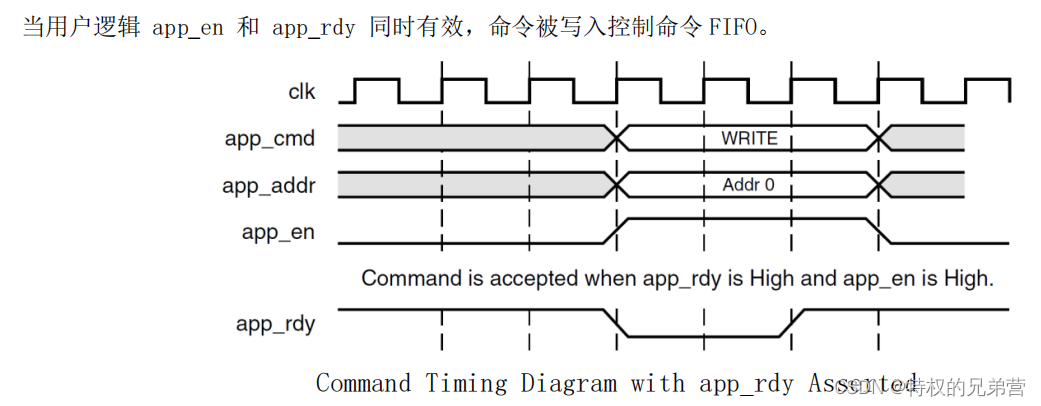

首先研究如何发出控制命令:发出命令的时许如下所示,

上图中的clk表示用户接口时钟ui_clk,本工程设置为100MHz。

app_cmd表示命令控制字,001表示读命令,000表示写命令。

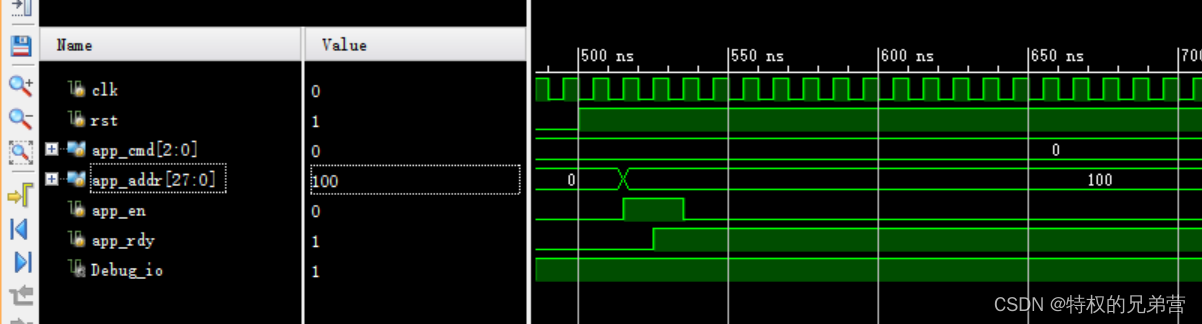

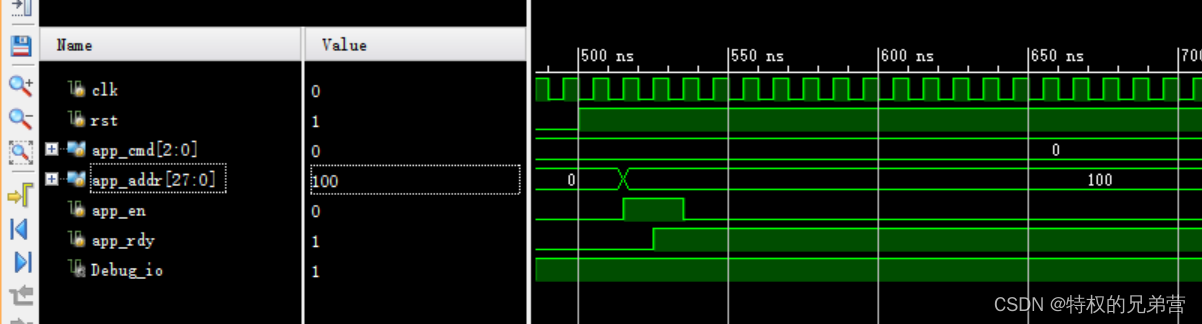

地址直接给‘d100

上面的图为用户接口写命令的时序

本文详细介绍了在使用MA703FA开发板时,如何通过XC7A35T-FGG484 FPGA的用户接口(UI_CLK@100MHz)发送控制命令,包括读写操作的时序图示,并重点讲解了地址和命令字的配置。

本文详细介绍了在使用MA703FA开发板时,如何通过XC7A35T-FGG484 FPGA的用户接口(UI_CLK@100MHz)发送控制命令,包括读写操作的时序图示,并重点讲解了地址和命令字的配置。

板卡型号:MA703FA开发板调试

FPGA主控芯片型号:XC7A35T-FGG484

上面的图为用户接口写命令的时序

9503

9503

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?