springboot 2.0配置WebMvcConfigurationSupport之后,会导致默认配置被覆盖,此时访问页面,会认为是访问controller对应的路径,要访问静态资源需在webmvcconfig中重写addResourceHandlers方法。

idea报错:

No mapping for GET /index.html

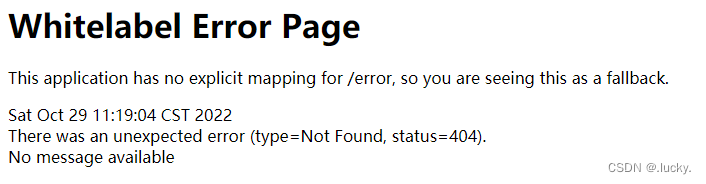

网页报错:

@Override

protected void addResourceHandlers(ResourceHandlerRegistry registry) {

registry.addResourceHandler()

.addResourceLocations("classpath:/templates/")

.addResourceLocations("classpath:/static/");

super.addResourceHandlers(registry);

}

3638

3638

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?