分析:

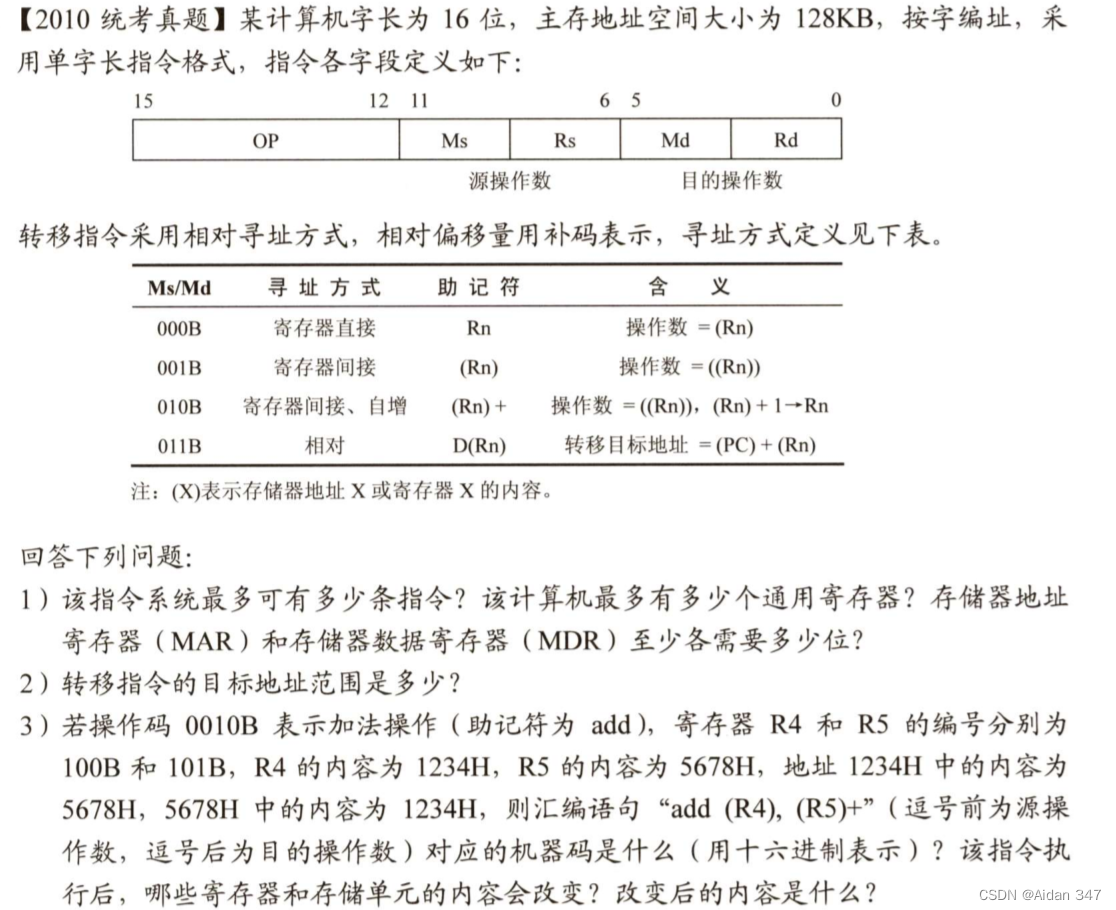

- 由题目可知操作码占4位,所以支持的操作指令为 2 4 2^4 24种指令

- 操作数占6位,其中寻址3位,寄存器编号3位,所以最多有 2 3 2^3 23个通用寄存器

- 主存大小为128KB,机器字长为16位,且按字编址,所以有 128 K B 2 B = 2 16 \frac{128KB}{2B} \quad = 2^{16} 2B128KB=216个存储单元,即MAR至少16位

- 机器字长为16为,那么MDR至少也是16位

- 存器字长为16 位,PC 可表示的地址范围为 [ 0 , 2 16 − 1 ] [0, 2^{16}-1] [0,216−1],Rn可表示的相对偏移量为 [ − 2 15 , 2 15 − 1 ] [-2^{15} ,2^{15}-1] [−215,215−1],而主存地址空间为 2 16 2^{16} 216,因此转移指令的目标地址范围为[0000H, FFFFH] ( [ 0 , 2 16 − 1 ] ) ([0, 2^{16}-1]) ([0,216−1])

- add:0010,寄存器间接寻址:001,R4:100,寄存器间接寻址且自增:010,R5:101,0010 0011 0001 0101B = 2315H

- 指令的功能是将 R4 的内容所指的存储单元的数据与 R5的内容所指的存储单元的数据相 加,并将结果送入 R5的内容所指的存储单元中。(R4)=1234H,(1234H)=5678H;(R5)= 5678H,(5678H)=1234H;执行加法操作5678H+1234H=68ACH。之后R5自增;

该指令执行后,R5和存储单元5678H的内容会改变,R5的内容从5678H变为5679H,存 储单元 5678H中的内容变为该指令的计算结果68ACH

分析:

1.由题意,执行周期内有间址和执行指令两种微操作

2.

C

1

到

C

4

为取指令和指令译码,

C

5

到

C

7

为间址,

C

8

到

C

10

为执行阶段

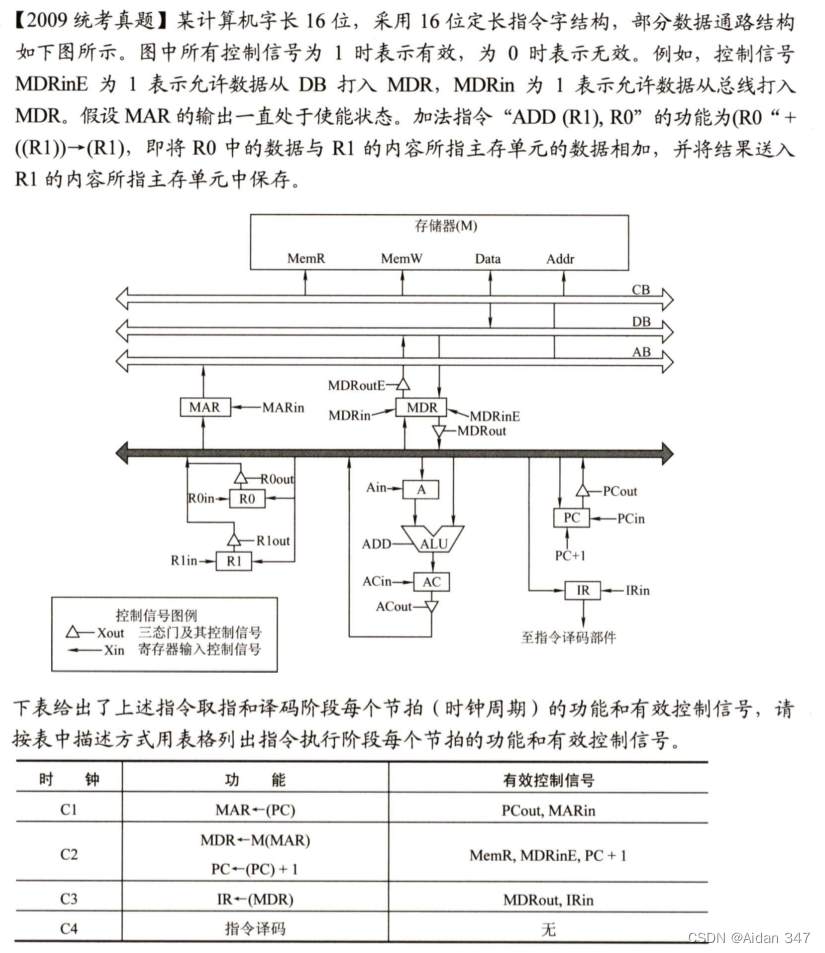

C_1到C_4为取指令和指令译码,C_5到C_7为间址,C_8到C_{10}为执行阶段

C1到C4为取指令和指令译码,C5到C7为间址,C8到C10为执行阶段

时钟

功能

有效控制信号

C

1

(

P

C

)

−

>

M

A

R

P

C

o

u

t

,

M

A

R

i

n

C

2

(

M

A

R

)

−

>

M

D

R

,

P

C

+

1

M

D

R

i

n

,

M

e

m

R

,

P

C

+

1

C

3

(

M

D

R

)

−

>

I

R

M

D

R

o

u

t

,

I

R

i

n

C

4

指令译码

−

−

C

5

(

R

1

)

−

>

M

A

R

R

1

o

u

t

,

M

A

R

i

n

C

6

M

(

M

A

R

)

−

>

M

D

R

M

e

m

R

,

M

D

R

i

n

E

C

7

M

(

M

D

R

)

−

>

A

M

D

R

o

u

t

,

A

i

n

C

8

(

A

)

+

(

R

1

)

−

>

A

C

R

0

o

u

t

,

A

C

i

n

,

C

U

向

A

L

U

发送

A

D

D

信号

C

9

(

A

C

)

−

>

M

D

R

A

C

o

u

t

,

M

D

R

i

n

C

10

(

M

D

R

)

−

>

M

(

M

A

R

)

M

D

R

o

u

t

,

M

e

m

W

\begin{array}{c|c|c} 时钟&功能&有效控制信号\\ \hline C_1&(PC)->MAR&PC_{out},MAR_{in}\\ \hline C_2&(MAR)->MDR,PC + 1&MDR_{in},MemR,PC + 1\\ \hline C_3&(MDR)->IR&MDR_{out}, IR_{in}\\ \hline C_4&指令译码&--\\ \hline C_5&(R_1)->MAR&R1_{out},MAR_{in}\\ \hline C_6&M(MAR)->MDR&MemR,MDR_{in}E\\ \hline C_7&M(MDR)->A&MDR_{out},A_{in}\\ \hline C_8&(A) + (R_1)->AC&R0_{out},AC_{in},CU向ALU发送ADD信号\\ \hline C_9&(AC)->MDR&AC_{out},MDR_{in}\\ \hline C_{10}&(MDR)->M(MAR)&MDR_{out},MemW \end{array}

时钟C1C2C3C4C5C6C7C8C9C10功能(PC)−>MAR(MAR)−>MDR,PC+1(MDR)−>IR指令译码(R1)−>MARM(MAR)−>MDRM(MDR)−>A(A)+(R1)−>AC(AC)−>MDR(MDR)−>M(MAR)有效控制信号PCout,MARinMDRin,MemR,PC+1MDRout,IRin−−R1out,MARinMemR,MDRinEMDRout,AinR0out,ACin,CU向ALU发送ADD信号ACout,MDRinMDRout,MemW

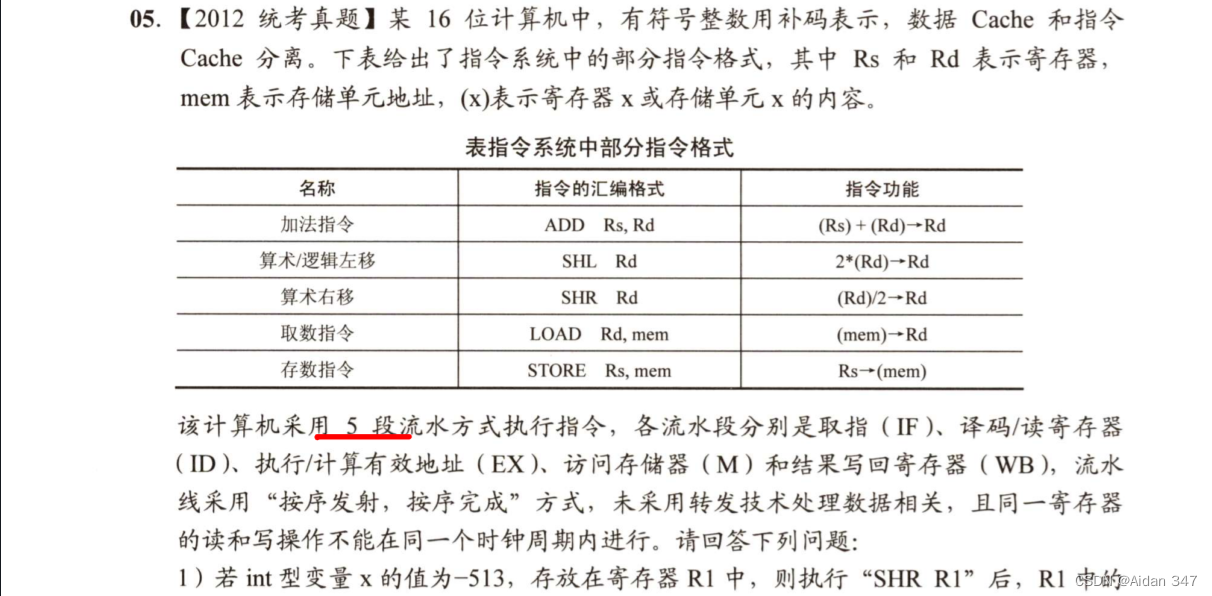

分析:

- [ − 513 ] 补 [-513]_补 [−513]补 = 1111 1101 1111 1111,负数补码右移数值位从高填1,为1111 1110 1111 1111,转16进制后,(R1) = FEFFH

- 由于是5段流水线方式,周期为5,有4条指令,5 + 4 - 1 = 8个周期

-

I

3

I_3

I3的ID段被阻塞是由于

I

3

I_3

I3与

I

2

I_2

I2存在数据相关,

I

3

I_3

I3要等到

I

2

I_2

I2执行结束将结果回写到寄存器后,

I

3

I_3

I3才能读取寄存器的内容;

I

4

I_4

I4的IF段被阻塞是由于下一条指令的IF段必须与上一条指令的ID段并行执行,而

I

3

I_3

I3的ID段被阻塞;

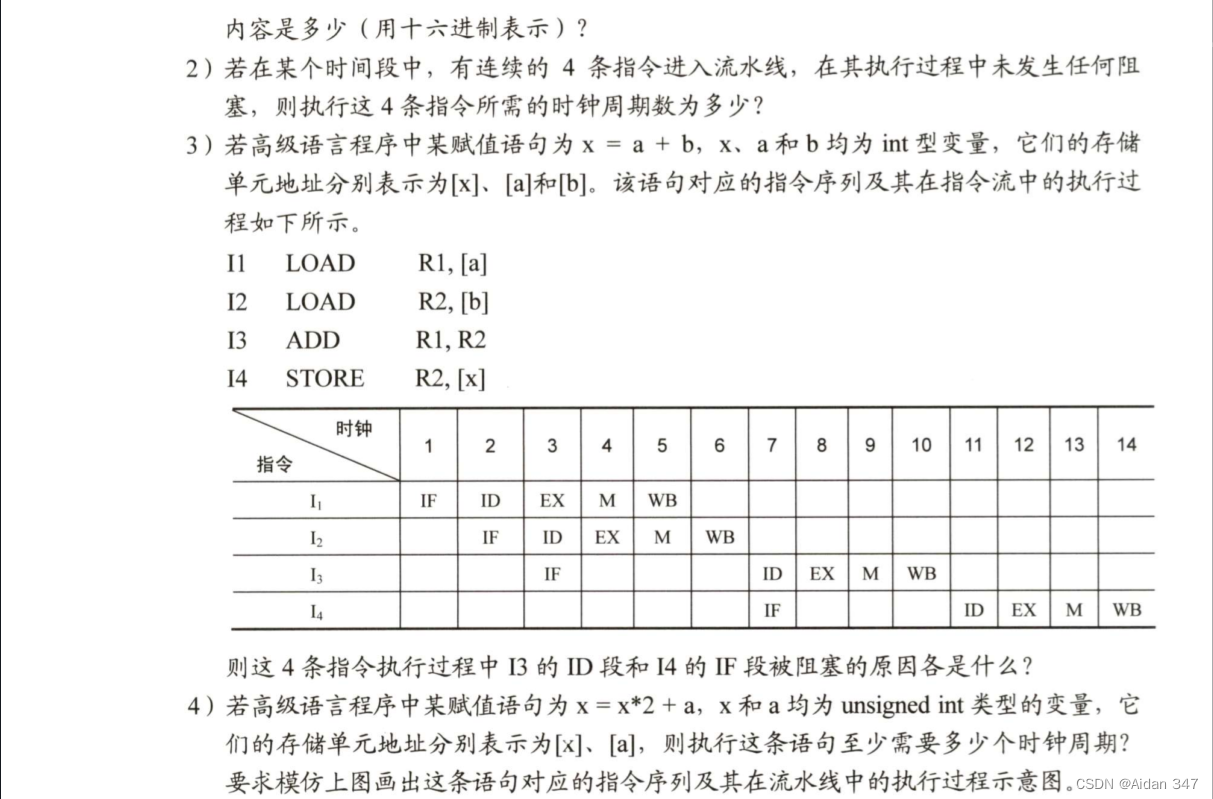

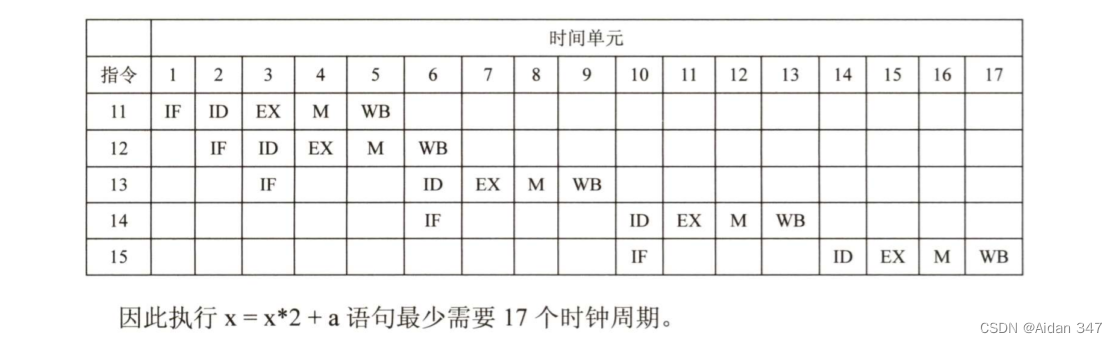

4.分析:取数a,x,x左移一位,相加后存到x中

指令 过程 I 1 L O A D R 1 , [ x ] I 2 L O A D R 2 , [ a ] I 3 S H I R 1 I 4 A D D R 1 , R 2 I 5 S T O R E R 2 , [ x ] \begin{array}{c|c|c} &指令&过程\\ \hline I_1&LOAD&R_1,[x]\\ \hline I_2&LOAD&R_2,[a]\\ \hline I_3&SHI&R_1\\ \hline I_4&ADD&R_1,R_2\\ \hline I_5&STORE&R_2,[x]\\ \end{array} I1I2I3I4I5指令LOADLOADSHIADDSTORE过程R1,[x]R2,[a]R1R1,R2R2,[x]

由于 I 3 I_3 I3的ID段需要访问寄存器,所以要等到 I 1 I_1 I1的WB段结束后才可以执行

1849

1849

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?