---------------------------------------------------------------------------------------------------------------------------------

声明 ①极简

②可能有误

③持续更新中

---------------------------------------------------------------------------------------------------------------------------------

目录

一、计系

1.1、计的发展

纸条编程,有孔-0,无孔-1

计系=硬件+软件

软件

①系统软件,管理整个计系

②应用软件,按需编的各种程序

硬件的发展

①电子管

②晶体管

③中小规模集成电路

④(超)大规模集成电路

1.2、计系的层次结构

1,硬件

硬件的基本组成

①早期冯诺依曼机的结构

②现代计算机的结构

存储程序(冯首次提出)

将指令,以二进制代码的形式,事先输入计的主存储器,然后按其首地址,执行程序的第一条指令,然后按该程序的规定顺序,执行其他指令,直至程序结束

早期冯诺依曼机

1️⃣软件

数据+程序

2️⃣硬件①输入设备,把信息转换成,机器能识别的形式

②存储器,存数据+程序

③运算器,算术运算+逻辑运算

④控制器,指挥程序运行

⑤输出设备,把结果转换成,人熟悉的形式

计系中,软件和硬件,在逻辑上等效

冯——特点

①计算机,由五大部件组成

②指令和数据,以同等地位存于存储器,可按地址寻访

③指令和数据,用二进制表示

④指令,由操作码和地址码组成

⑤存储程序

⑥以运算器为中心(⇒低效)

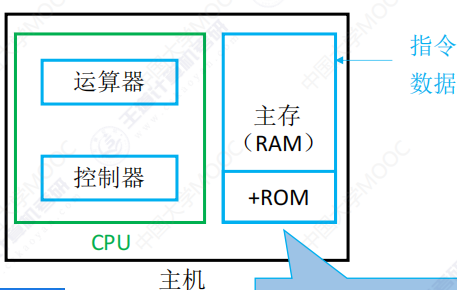

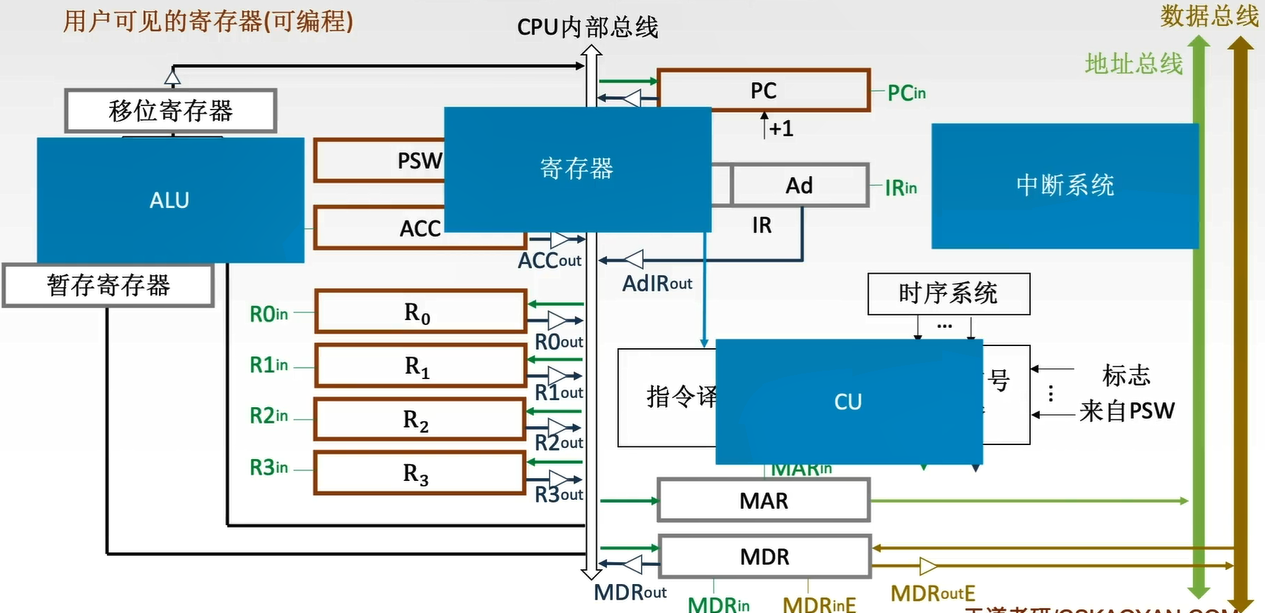

现——特点

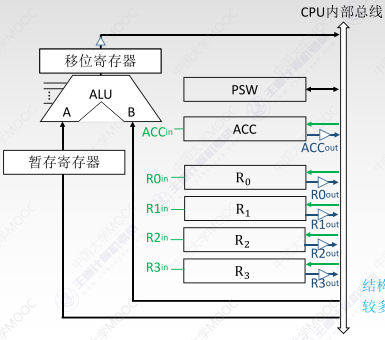

①以存储器为中心

②CPU=运算器+控制器

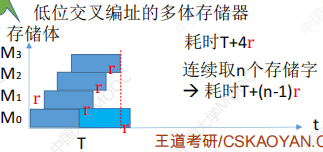

2,主存储器

存储体,按地址存数据

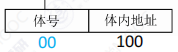

MAR位数=地址码长度,反映存储单元的个数

MDR位数=存储字长

··

MAR=4位⇒总共有2⁴个存储单元

MDR=16位⇒ 每个存储单元可存放16bit

1个字 (word)= 16bit

1个字节(Byte)= 8bit

1B=1个字节

1b=1个bit

存储体——内部概念

存储单元:存一串二进制代码

存储单元=多个存储元件(一元件,存1bit)(每个地址,对应一个存储单元)

存储单元中

①存储字(word):二进制代码的组合

②存储字长:二进制代码的位数

存储元:存二进制的电子元件,1存储元可存 1bit

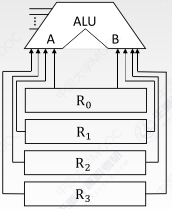

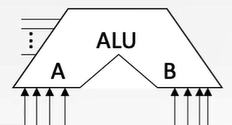

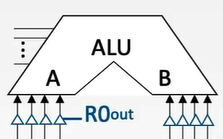

3,运算器

运算器——功能

算术运算(+-*/)

逻辑运算(与或非)

运算器——组成

1️⃣ACC,累加器

①存操作数

②存运算结果

2️⃣MQ,乘商寄存器,*/时①存操作数

②存运算结果

3️⃣X,通用的操作数寄存器存操作数

4️⃣ALU,算术逻辑单元(最贵)通过电路,算数运算+逻辑运算

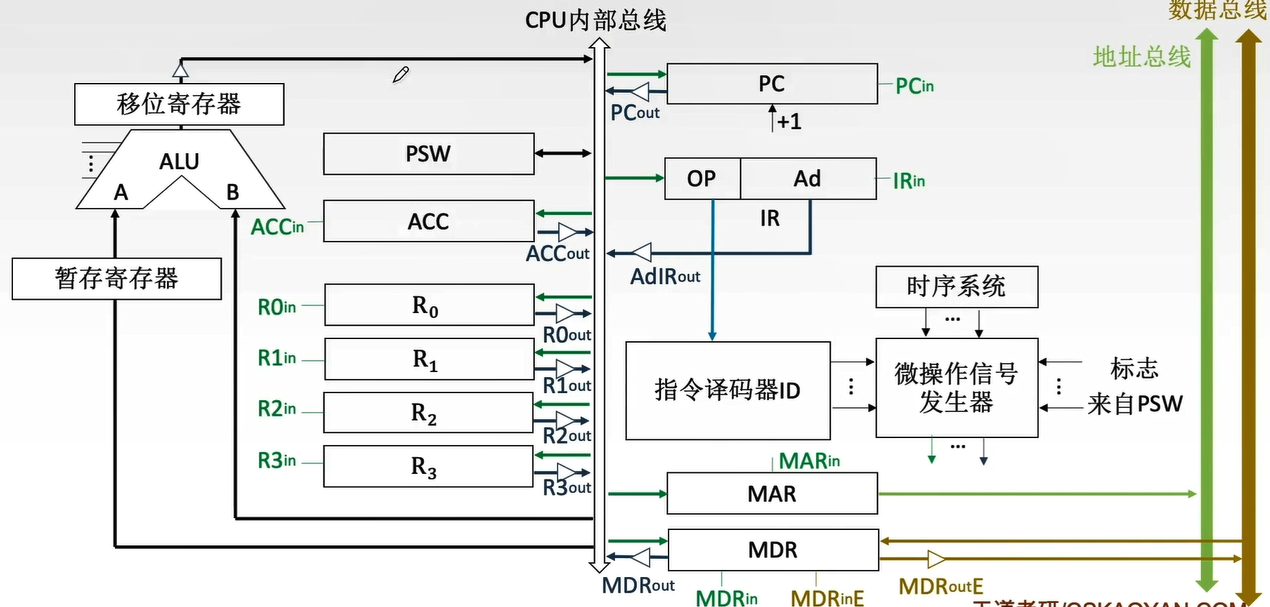

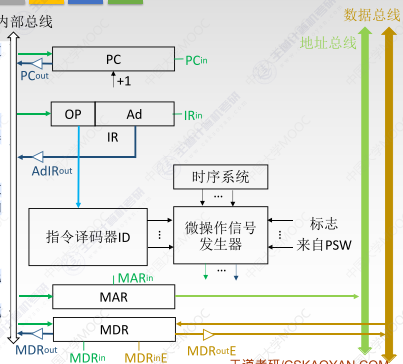

4,控制器

控制器——基本组成

①CU:控制单元,分析指令

②IR:指令寄存器,存当前指令

③PC:程序计数器,存放下一指令的地址,能自动+1

完成一条指令——步骤

①取指令 PC——取指

②分析指令 IR——取指

③执行指令 CU——执行

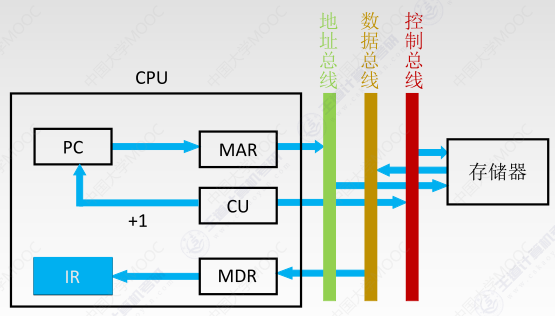

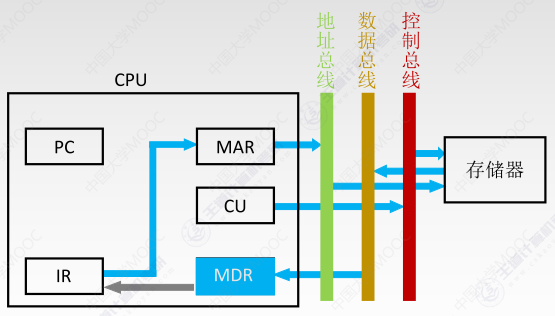

计——工作过程

必经步骤

①(PC) —> MAR

②M(MAR) —> MDR

③(MDR) —> IR

④取指令结束 (PC)+1 —> PC

⑤OP(IR) —> CU

⑥分析指令结束

可能步骤

①Ad(IR) —> MAR

②M(MAR) —> MDR

③(MDR) —> ACC

④执行指令结束

CPU区分指令和数据:指令周期的不同阶段

现在的计算机,把MAR、MDR也集成在CPU

5,计软

计软——种类

①应用软件,为了解决某问题,而编制的程序

②系统软件,管理硬件资源,并向上层应用程序提供基础服务

语言

①高级语言:C/C++、Java、Python

②汇编语言:助记符

③机器语言:二进制代码

(低语=汇语、机语)

(all程序运行前都要先—>机语程序)

高语——>机语

翻译程序

①编译器(一下全部翻译)

②汇编器

③解释器(同步翻译)

软件和硬件的逻辑功能等价,同一功能

①可用硬件实现(性能高成本高)

②可用软件实现(性能低成本低)

指令集体系结构(ISA),软件和硬件之间的界面

(低语程序员)

设计系的ISA,需要定义

①一台计,可支持哪些指令

②每条指令的作用

③每条指令的用法

(控制信号不由ISA管,而是cpu的控制单元)

6,计系

计——层次结构

软件

M4,高语机器⇒执行高语

M3,汇语机器⇒执行汇语

M2,OS机器⇒向上提供广义指令

硬件

M1,传统机器⇒执行机语指令

M0,微程序机器⇒执行微指令

计系——工作原理

1.3、计的性能指标

MAR位数,存储单元最多有多少个

MDR位数=存储字长=每个存储单元的大小

总容量=存储单元个数×存储字长 bit

总容量=存储单元个数×存储字长/8 Byte

总容量——例题

MAR=32位

MDR=8位

总容量=2^32 * 8 bit = 4GB

CPU——性能指标

CPI(更准确的说法)

一指令耗时多少个时钟T

cpu周期(机器周期)

=多个时钟T

数据通路带宽(路有多宽)

数据总线一次,所能并行传送信息的位数

吞吐量(淘宝能收多少信息)

指系统,在单位时间内处理请求的数量

响应时间

①人向计,发送1请求

②系统对该请求,做响应

③人获得结果

的等待时间

基准程序(跑分软件)

测量计处理速度的一种实用程序

数量单位

二、数据的表示和运算

2.1、数制与编码

1,无符号数

定点数,小数点的位置固定 Eg:9.007 ——常规计数

浮点数,小数点的位置不固定 Eg:9.96*10² ——科学计数法

无符号数——定义

整个机器字长的全部二进制位,all为数值位,没有符号位,=|数|

(只有无符号整数,没有无符号小数)

无符号数——范围

位数=n,范围∈[0,2ⁿ-1]

2,有符号数

真值——范围

若机器字长=n+1,真值∈[-2ⁿ, 2ⁿ - 1]

(原因,真值有+0和-0)若机器字长=n+1,真值∈[0,2ⁿ⁺¹-1](不确定对错)

真值

①+0,原码=0,0000000

②-0, 原码=1,0000000

原码

原码——定义

①符号位,0+,1-

②数值位(尾数),=|真值|

原码——写法

例1,-19

一般,[x]原 =1,0010011

机器字长未知,[x]原 =1, 10011

例2,-0.75

[x]原 = 1.1100000

原码——范围

若机器字长=n+1

①原码整数∈[-(2ⁿ-1),2ⁿ-1]

②原码小数∈[-(1-2⁻ⁿ),1-2⁻ⁿ]

原码——缺

①符号位,不能运算

②解决①,贵

补码

补码的真值,只有一种,全0

[+0]补= [-0]补= 00000000

补码——范围

(多出一个)(机器字长=8,10000000代表-128,记住就行,自己算不出来)

若机器字长=n+1

①补码整数,∈[-2ⁿ,2ⁿ-1]

②补码小数,∈[-1,1-2⁻ⁿ]

补码——作用

减变加,省硬件成本

移码

移码——定义(只能表整数)

补码的符号位取反

[+0]移= [-0]移= 10000000

移码——范围(=补码的范围)

若机器字长=n+1

①移码整数,∈[-2ⁿ,2ⁿ-1]

②移码小数,∈[-1,1-2⁻ⁿ]

移码——作用

便于对比大小

转换

原——>反

1️⃣+

原=反

2️⃣-

数值位取反

反——>原

1️⃣+

原=反

2️⃣-

数值位取反

原——>补

1️⃣+

原=补

2️⃣-

法一,机算

①原码,数值位取反⇒反码

②反码,末位+1⇒补码

法二,手算

①找最右1

②1,左边,数值位取反

,右边,不变(没有1,就不管)

(例,原=10000000 则补=10000000)

补——>原

1️⃣+

补=原

2️⃣-

法一

①数值位取反

②末位+1

法二

①找最右1

②1,左边,数值位取反

,右边,不变

补——>-补

①符号位+数值位,都取反

②末位+1

补<——>移

符号位取反

3,进制

二进制B

八进制O

十六进制H

十进制D

r进制,逢r进1(其基数=r)

基数,每个数码位所用到的不同符号的个数

二进制——最适用于计的原因

①可用两个稳定状态的物理器件表示

②0-假,1-真,便于逻辑运算

③便于逻辑门电路,实现算术运算

十六 ——> 二

十—>二

1️⃣算

①整数——除基取余

②小数——乘基取整(∞小数,二进制不能精确表示)

2️⃣拼凑法

十—>八

1️⃣直接转

①整数——除基取余

②小数——乘基取整

2️⃣十—>二—>八

①十—>二,①整数——除基取余

②小数——乘基取整

②二—>八

3️⃣十—>二—>八

①十—>二,拼凑法

②二—>八

引入BCD码——原因

①十—>二,麻烦

②快速转,一一对应

十—>8421

1️⃣手算

①十+

②十—>8421

2️⃣机算

①8241+

②若超过1010~1111(10~15),+0110(6)

映射关系

①8421

②余3码

③2421

2.2、运算方法和运算电路

0,逻辑门电路

逻辑门电路——图

异或——作用

①奇个 1,异或结果=1

②偶个 1,异或结果=0

逻辑运算——公式

逻辑运算——优先级

①非>与>或

②()优先级,更高

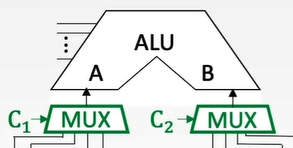

1,多路选择器

多路选择器——作用

①电路守门员

②多输入,just通过1个

多路选择器——图

2,三态门

三态门——作用

①电路守门员

②根据op,决定是否通过输入

三态门——图

三态门和非门——区别

三态门

①输入

②输出

③控制信号

非门

①输入

②输出

3,加法器

一位全加器

(支持1bit加法)

nbit加法器

没封装的

封装的

nbit加法器——缺

进位信息串行,计算V慢

nbit加法器——缺原因

①V=V进位产生+V传递

②位数越多,V越慢

③电信号稳态耗时,V进位产生有延迟

④串行进位/行波进位,进位信号逐级形成(多米诺骨牌)

nbit加法器——别称

①两个输入端,允许并行输入⇒并行加法器

②进位信息,串行产生⇒串行进位加法器

③综上,串行进位的并行加法器

并行进位的并行加法器

all进位信息,同时产生,几乎无延迟

nbit加法器——标志位

①OF(Overflow Flag)溢出标志

判,带符号数+-,是否溢出

OF=1,溢出

OF=0,未溢出

②SF(Sign Flag)符号标志

判,带符号数+-,结果的正负性

SF=1,=负

SF=0,=正

③ZF(Zero Flag)零标志

判,+-,结果是否为0

ZF=1,=0

ZF=0,≠0

④CF(Carry Flag)进位/借位标志

判,无符号数+-,是否溢出

CF=1,溢出

CF=0,未溢出

标志位——公式

①

最高位的进位⊕次高位的进位

②符号位

③bit 全0,ZF=1

④

4,算术逻辑单元ALU

CPU——图

运算器——核心=ALU

ALU——核心=加法器

ALU——功能

①算术运算,+-*/

②逻辑运算,与、或、非、同或、移位

③求补码

④求直送

ALU——图

5,算术移位

注

由于原、反、补码位数有限,算术移位,不能精确等效×、÷

补充

移位不用记这么多东西,看我标蓝的

(服了哈哈哈哈哈哈哈,白看了这么多移位)

定点整数

①有符号整数,补码

②无符号整数,无符号数

定点数的移位

①算术移位,补码

②逻辑移位,无符号数

(移位运算,计不区分算术还是逻辑,由数据类型决定)

算术移位——原码

原码——移位原理

①符号位不变

②移数值位

原码——右移

①高位补0

②低位舍弃,若舍=0,等价于÷2

舍≠0,丢精度

原码——左移

①低位补0

②高位舍弃,若舍=0,等价于X2

舍≠0,大误差

算术移位——反码

正数的反码——移位=原码

+数的反码——右移

①高位补0

②低位舍弃

+数的反码——左移

①低位补0

②高位舍弃

-数的反码——右移

①高位补1

②低位舍弃

-数的反码——左移

①低位补1

②高位舍弃

算术移位——补码

+数的补码——移位=原码

+数的补码——右移

①高位补0

②低位舍弃

+数的补码——左移

①低位补0

②高位舍弃

-数的补码——右移=反

①高位补1

②低位舍弃

-数的补码——左移=原

①低位补0

②高位舍弃

6,逻辑移位

逻辑移位=无符号数的算术移位

逻辑右移

①高位补0

②低位舍

逻辑左移

①低位补0

②高位舍

逻辑移位——应用

用3B,存RGB

循环移位

带进位位CF,可留着循环移位

7,定点数的加减

原码——加

(符号位不参与运算,自己判断)

①正+正——>绝对值做加法,结果=正

②负+负——>绝对值做加法,结果=负

③正+负——>|大|—|小|,符号同|大|

④负+正——>|大|—|小|,符号同|大|

原码——减

转成加

①正-负——>正+正

②负-正——>负+负

③正-正——>正+负

④负-负——>负+正

补码——加

①真值——>原

②原——>补

③补相加(符号位参与运算)

④补——>原

补码——减

(减转加)

①真值——>原

②原——>补

③-补——>补

④补相加(符号位参与运算)

⑤补——>原

补码加减——溢出情况

①上溢,正+正=负

②下溢,负+负=正

补码加减——溢出判断

①一位符号位

V=0,无溢出

V=1,溢出

②一位符号位,看进位

V=0,无溢出

V=1,溢出

③双符号位

正数符号=00

负数符号=11

V=0,无溢出

V=1,溢出

注

双符号位补码,模4补码

(实际只存1个符号位,运算时复制1个符号位,不会增存储所需空间)

单符号位补码,模2补码

8,无符号数的加减

无符号整数——加法

①从右往左,按位加,进1

②溢出,只留n位

无符号整数——减法

①被减数不变

②减数all取反,末位+1

③加

(减转加,原因=加法电路便宜)

无符号数——加减法判溢出

1️⃣手算

超出[0,2ⁿ-1],溢出

2️⃣机算①加

最高位的进位=1,溢出

②减

(减转加)

最高位的进位=0,溢出

9,补码加减运算电路

补码加减运算电路——图

(也可用于无符号数+-)

10,原码一位乘法

原码一位乘法——元件

①ACC,存乘积高位

②MQ,存乘积、乘积低位

③X,存被乘数

原码一位乘法——方法

①先加法

②再逻辑右移

③重复n次(符号位不参与运算)

原码一位乘法——机算步骤

题目

①机器字长n+1=5

②[A]原=1.1101

③[B]原=0.1011

求A×B

步骤

原码一位乘法——手算步骤

题目

①机器字长n+1=5

②A=−0.1101

③B=+0.1011

求A×B

步骤

①

②符号位=A符⊕B符=1

③结果

真值=-0.10001111

其原码机器数=1.10001111

11,补码一位乘法

原码一位乘法——元件

①

灰,MQ中最低位

红,辅助位,初始=0

②寄存器,all统一为n+2位,⇒双符号位补码

补码一位乘法——方法

①先加法

②再算术右移

③重复n次④最后再加一次

(符号位参与运算)

加法——规则

①辅助位-MQ中最低位=1,ACC+[x]补

②辅助位-MQ中最低位=0,ACC+0

③辅助位-MQ中最低位=-1,ACC)+[-x]补

补码一位乘法——手算步骤

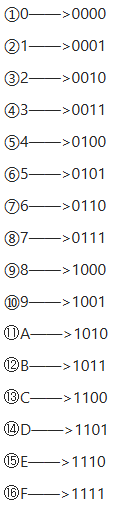

12,原码除法

题目

①机器字长n+1=5,含1位符号位

②A=0.1011

③B=0.1101

求A÷B

手算除法(二进制)——步骤

恢复余数法——机算

恢复余数法——手算规律

①不管小数点

②每确定一位商,减一次,得到4位余数

③余数末尾补0,确定下一位商

④确定5位商即可停止(机器字长为5位)

恢复余数法——手算

①写

|A|=0.1011

|B|=0.1101

[|B|]补=0.1101

[−|B|]补=1.0011

②

加减交替法(不恢复余数法)——手算

恢、加——区别

恢

①余数=负,商0

②余数+除数(恢复)

③左移

④余数-除数

加

①余数=负,商0

②左移

③+除数

①余数=正,商1

②左移

③余数-除数

注

加减交替法,余数的正负=商,商也是⊕

加减交替法——计算次数

一般

①加/减n+1次,每次加减确定一位商

②左移n次

最终,若余数=负,商0,并+[|B|]补,得到正余数

①加/减n+2次

②左移n次

13,补码除法

补码——加减交替法

对比原码——加减交替法

补

①符号位参与运算

②双符号位

③数据

A补

B补

(-B)补

补码——加减交替法步骤

14,扩展

零扩展

用0扩展高位

(适用无符号整数)

符号扩展

用符号位扩展高位

(适用有符号整数)

C语言中定点整数

int、short、long,用补码存

强制类型转换

①int—>unsigned int

数据内容不变

解释方式不变

②int—>short

截高位,留低位

③short—>int

符号扩展

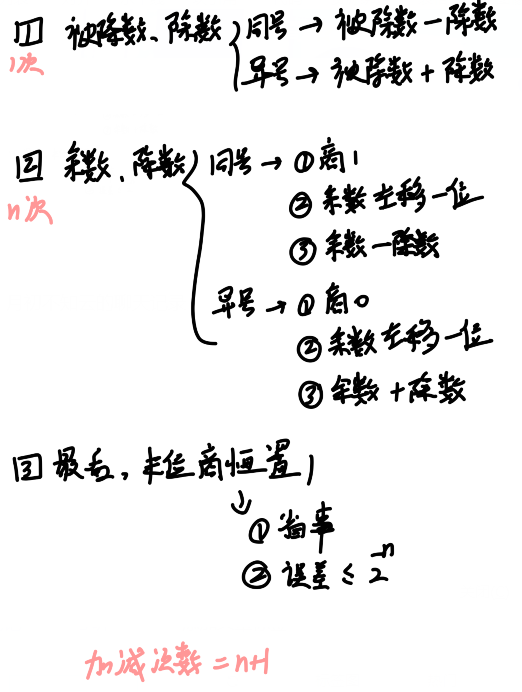

大小端模式

多字节数据在内存,占连续字节

15,数据的存储和排列

现代计算机按字节编址,每个字节对应一个地址

16位系统,1字=2B

32位系统,1字=4B

64位系统,1字=8B

char,1B

short,2B

int,4Bfloat,4B

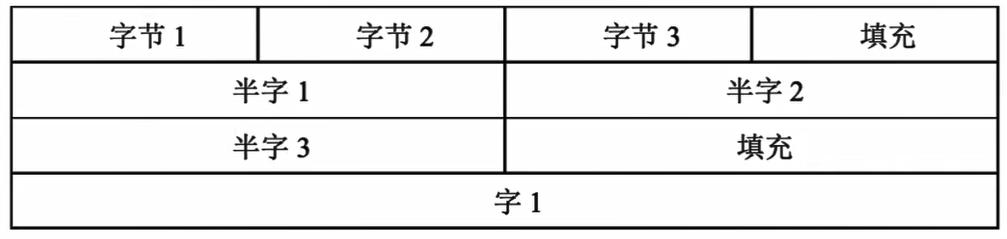

边界对齐——图

边界不对齐——图

边界对齐,访存=1次,浪费空间

边界不对齐,访存=2次,不浪费空间(访存,以字或者B为单位)

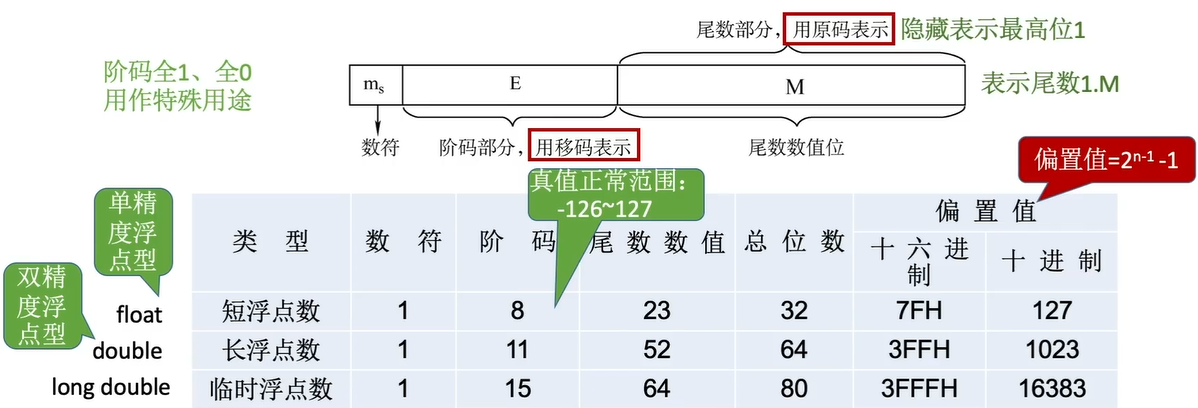

2.3、浮点数

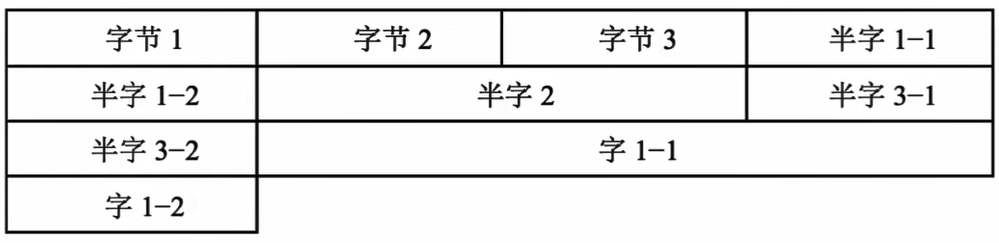

1,浮点数的表示

阶码

①数值大小(浮点数的范围)

②补/移码表示的定点整数

尾数

①精度

②原/补码表示的定点小数

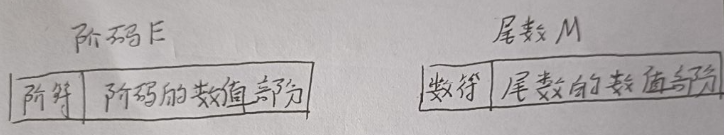

浮点数——尾数规格化

尾数的最高数值位是有效值(≠0)

左规,尾数算术左移一位,阶码-1

右规,尾数算术右移一位,阶码+1

双符号位

溢出时可挽救,更高的符号位是对的符号位

规格化的原码尾数,最高数值位=1

规格化的补码尾数,符号位和最高数值位相反

浮点数——范围

2,IEEE 754

移码只能表示整数,可用来表示阶码

移码=真值+偏置值

偏置值一般取2ⁿ⁻¹,也可取其他值

此时,移码=补码符号位取反

阶码全0、全1——用途

3,浮点数的加减

浮点数加减——步骤

1️⃣对阶

求阶差—>对阶,小向大靠齐,小的尾数每右移一位,阶码+1

2️⃣尾数加减

3️⃣规格化

4️⃣舍入

①0 舍 1

末位删 1,尾数 + 1

末位删 0,不管

②恒置 1

末位删啥,末位最后都 = 1

5️⃣判溢出(阶码+1,符号一样,无溢出)

①阶码上溢,抛出异常

②阶码下溢,按机器 0 处理

强制类型转换

一般考32位

int

①表整数

②范围 [-2³¹,2³¹-1]

float

①表整数、小数

②范围 ±[2⁻¹²⁶,2¹²⁷ ×(2−2⁻²³)]

转换——损失

范围、精度从小到大,转换无损失

①char —> int —> long —> double

②float —> doubleint—>float,损精度

float—>int

①float>int 时,溢出

②float 表小数时,损精度

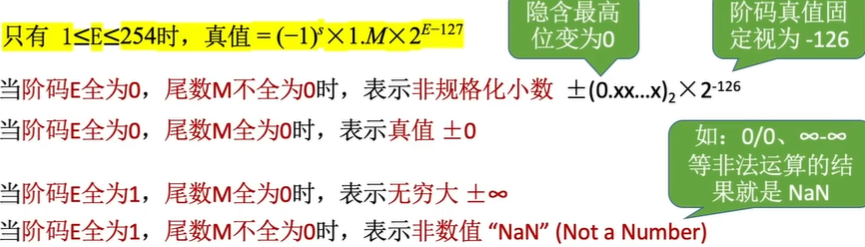

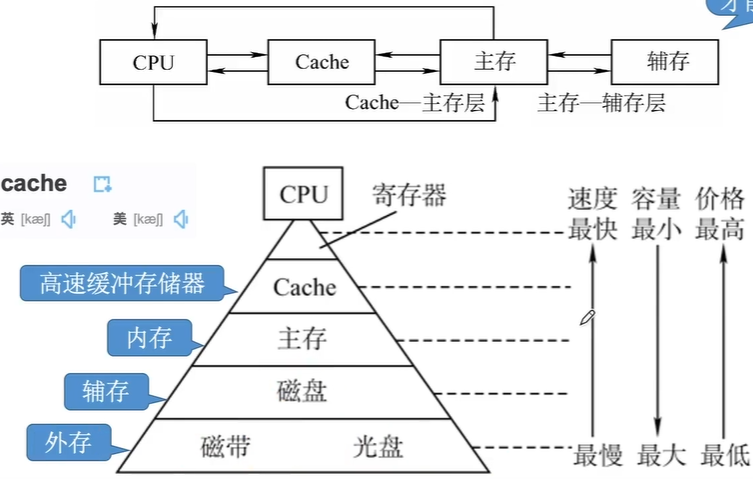

三、存储系统

3.1、存储器

1,层次化结构

主存<——>辅存,硬件+OS实现——>虚存

Cache<——>主存,硬件自动完成——>解决主存与cpu速度不匹配

2,分类

1️⃣存储介质

①半导体存储器(主存、Cache)

②磁表面存储器(磁盘、磁带)

③光存储器

2️⃣存取方式

①随机存取存储器(RandomAccess Memory,RAM):读写任一单元,时间一样

②顺序存取存储器(Sequential Access Memory,SAM):读写一单元,时间取决于物理位置

③直接存取存储器(Direct AccessMemory,DAM):可随机存取、顺序存取。先选区,再按顺序存取

(SAM和DAM,统称为串行访问存储器:读写某单元,时间与物理位置有关)

3️⃣信息的可更改性

①读写存储器(Read/Write Memory):读、写(磁盘、内存、Cache)

②只读存储器(Read Only Memory):读(实专 CD-ROM,电影光碟,BIOS 写在 ROM 中)

4️⃣信息的可保存性

①易失性存储器(主存、Cache):断电后,信息没了

②非易失性存储器(磁盘、光盘):断电后,信息没了破坏性读出(如DRAM芯片,读出后重写):信息读出后,被破坏

非破坏性读出(如SRAM芯片、磁盘、光盘):信息读出后,不破坏

3,性能指标

①存储容量:存储字数×字长

②单位成本:每位价格=总成本/总容量

③存储速度:数据传输率(主存带宽,每秒从主存进出信息的最大数量)=数据的宽度/存储周期 (存储字长=数据的宽度)

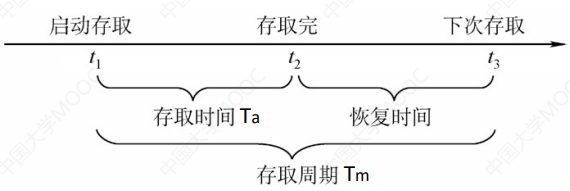

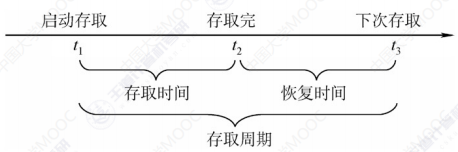

存储周期

① 存取时间(Ta):从启动一次存储器操作,到完成的时间

=读出时间+写入时间

② 存取周期(Tm):(读写/访问周期)

存储器进行一次完整的读写操作,所需时间

即连续两次独立地访问存储器操作(读或写操作)之间所需的最小时间间隔

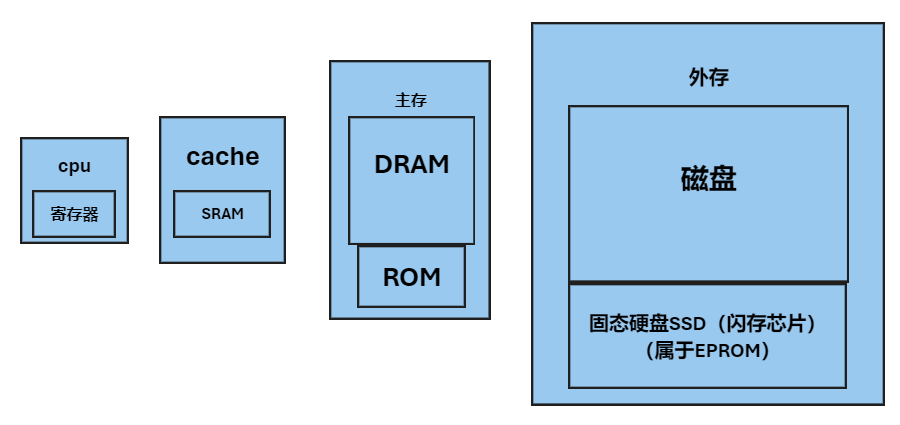

3.2、主存

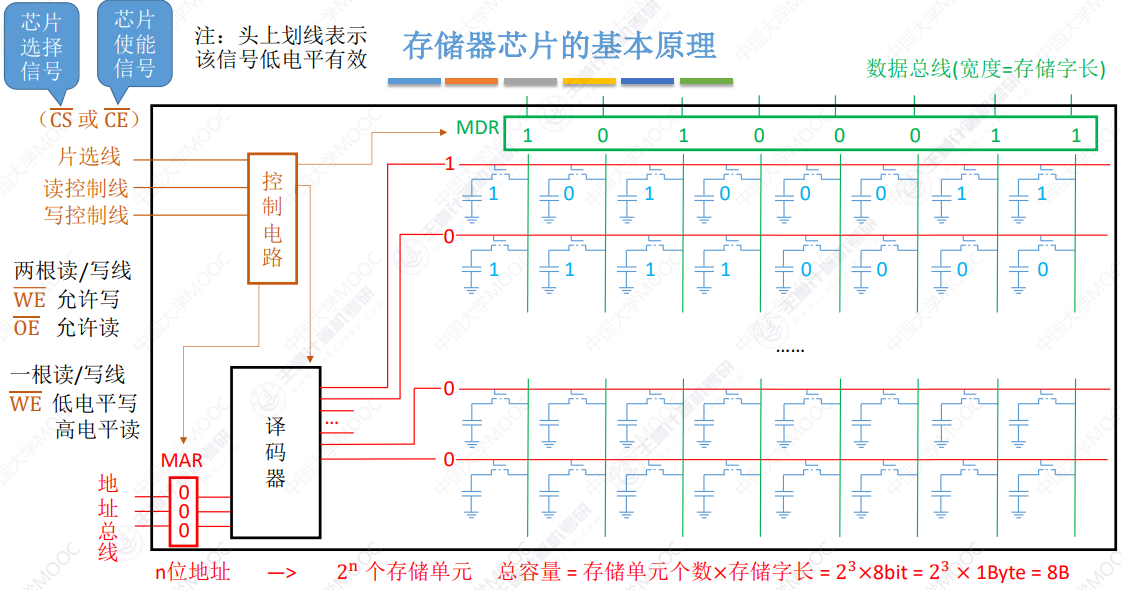

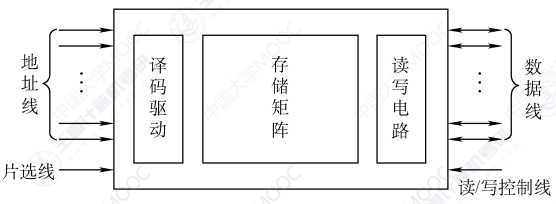

1,基本组成

MOS管,一种电控开关,输入电压达到某个阈值时,MOS管就可以接通

充电1,写数据

放电0,读出数据

cpu通过数据总线,从MDR中取数据

多个存储单元,构成存储体/矩阵

存储字/单元的长度(存储字长),取决于存储体

每根线对应一金属引脚

(还有供电引脚、接地引脚)

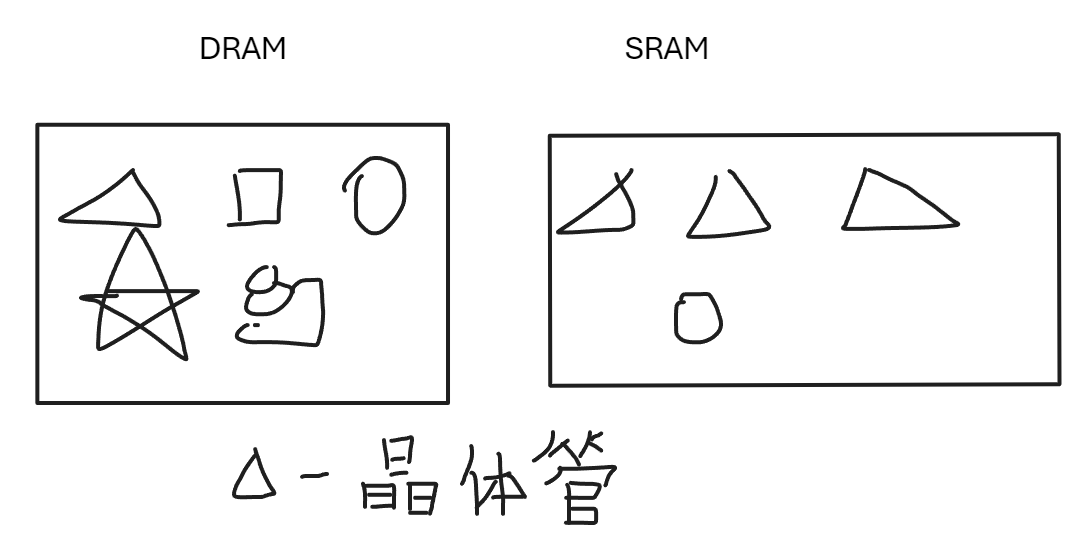

2,SRAM和DRAM

SRAM(Static Semiconductor Memory)(静态半导体存储器)

DRAM(Dynamic Semiconductor Memory)(动态半导体存储器)

集成度,DRAM>SRAM

对比图

SRAM,用双稳态电路的两个稳定状态,存0和1

DRAM,用电容暂存信息,无电荷-0,有电荷-1

注

地址复用,地址引脚减半,数据引脚不变

DRAM——刷新

刷新,定期对DRAM的电容充电

①刷新周期=2ms

②以行为单位,每次刷新一行存储单元

③行列地址,可↓选通线的量

④有硬件支持,不需 cpu 控制

⑤读出一行的信息后重新写入,占用 1 个读/写周期(存取/储周期)

传统DRAM与cpu,异步交换数据

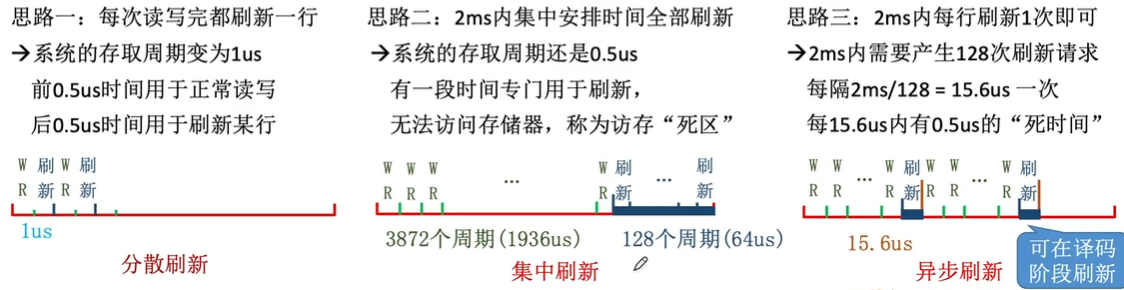

刷新——方法

设DRAM排列成128×128,读/写周期=0.5us

行、列地址分两次送,可使地址线更少,芯片引脚更少

3,ROM

RAM——易失性,断电后数据消失

ROM——非易失性,断电后数据不会丢失

分类

1️⃣MROM(Mask Read-Only Memory)(掩模式只读存储器)

不可重写,只能读

可靠性高、灵活性差、生产周期长、只适合批量定制

2️⃣PROM(Programmable Read-Only Memory)(可编程只读存储器)

用专门的PROM写入器,写入信息,写一次后不可改

3️⃣EPROM(Erasable Programmable Read-Only Memory)(可擦除可编程只读存储器)

①紫外线,擦

②写次数有限

③擦复杂

4️⃣UVEPROM(ultraviolet rays)

紫外线照8~20分钟,擦除all信息

5️⃣EEPROM(E2PROM)(电可擦除可编程只读存储器)(第一个E是Electrically)

电擦除,擦除特定的字①电信号,擦

②更多次的写

③可随时改(速度,EEPROM>EPROM)

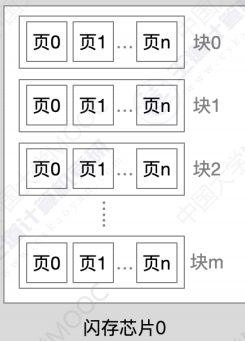

6️⃣Flash Memory(闪速存储器)

①U盘、SD 卡

②每个存储元只需单个 MOS 管,位密度>RAM

③以 EEPROM 为基础,断电后也能保存信息

④可多次快速擦除重写

⑤先擦除,再写入⇒速度,写<读

7️⃣SSD(Solid State Drives)(固态硬盘)

①=控制单元+存储单元(Flash)

②与闪速的区别=控制单元不一样,存储介质类似

③可多次快速擦除重写

④速度快、功耗低、价格高

⑤PC 用 SSD 取代机械硬盘

⑥手机辅存里面的 Flash,比 SSD 的 Flash 集成度高、功耗低、价格贵

注

①很多 ROM 可写,很麻烦

②闪存写入前,要先擦除

③ROM 也有随机存取

④RAM 和 ROM 不是完全对立

cpu,到主存中取指令,再执行指令

内存条,就是主存

BIOS芯片(ROM),存了自举装入程序,负责引导装入OS(开机)

4,多模块存储器

双端口RAM,408统考已删,有的自命题可能考

存取周期,可连续读写的最短时间间隔

多体并行存储器

各模块

①容量、存取速度相同

②有独立的读写控制电路、地址寄存器、数据寄存器

单体多字存储器

①各存储单元存 m 个字

②总线宽度=m

③一次并行读出 m 个字,不能单独取其中某个字

④指令和数据在主存内,必须连续

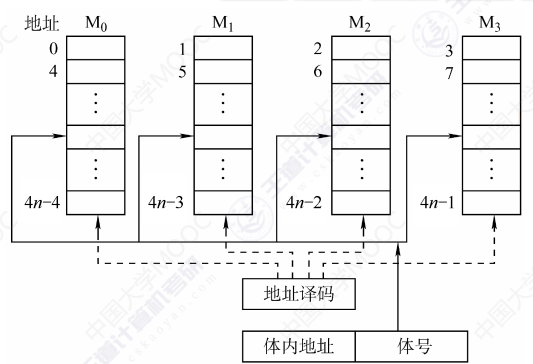

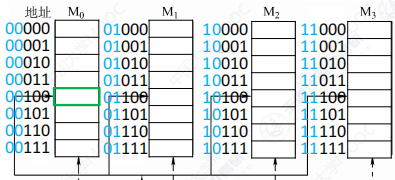

高位交叉编址

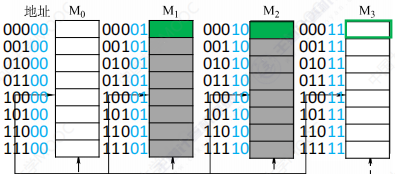

低位交叉编址

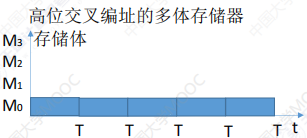

存取周期=T

存取时间(总线传输周期)=r

模块数=m

为了流水线不间断,模块数m≥T/r(m=T/r,性能最好)

流水线的方式并行存取

①宏观上并行

②微观上串行

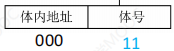

给定地址X,求它属于第几个存储体

①看体号

②x%存储体个数

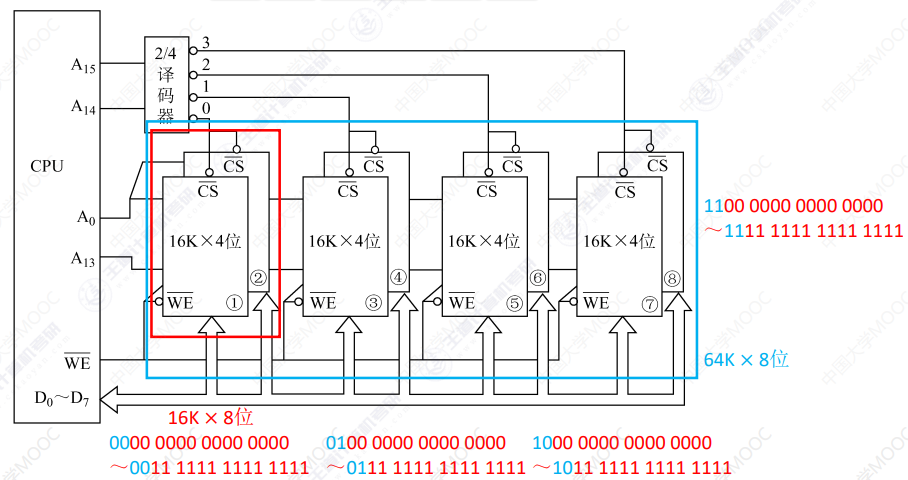

3.3、主存与CPU的连接

现代计算机

存储器芯片——输入输出信号

↑ 主存的存储字长

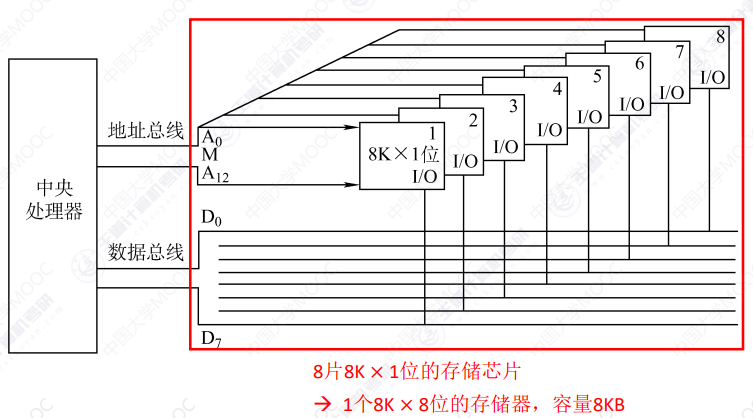

1️⃣位扩展

2️⃣字扩展

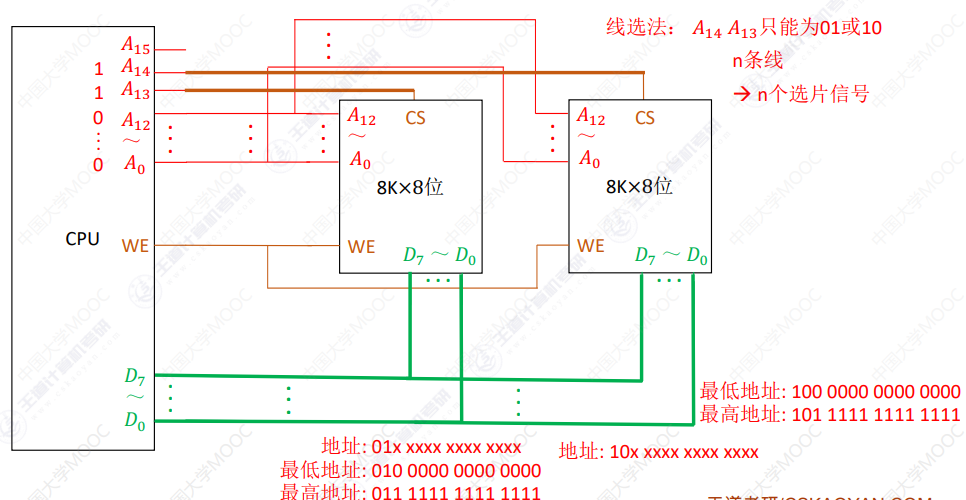

①线选法

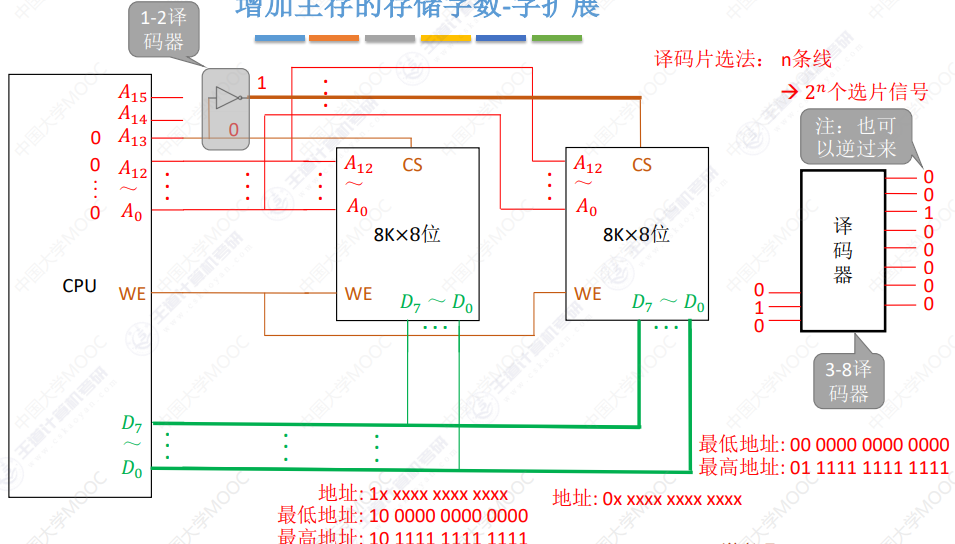

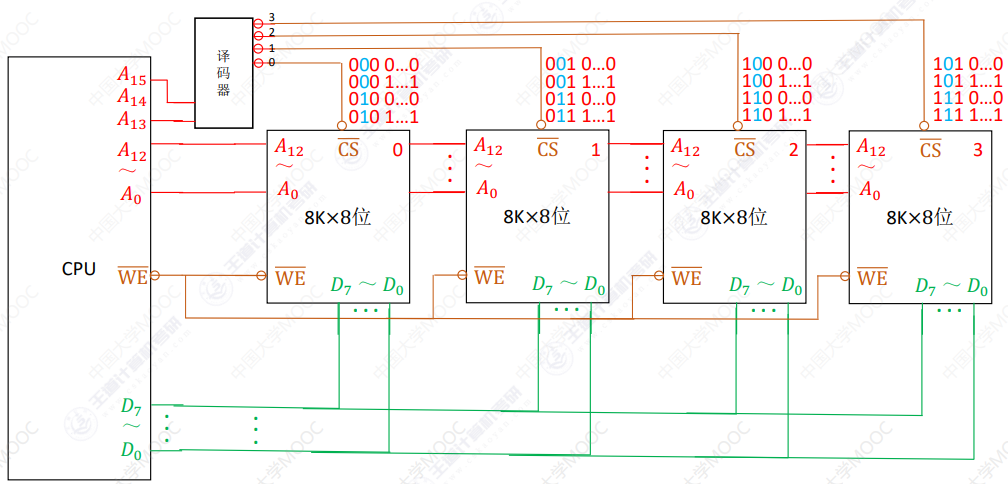

②译码器片选法

3️⃣字位同时扩展

译码器的使能端

CPU,可控制片选信号的生效时间

3.4、外存

1,磁表面存储器

磁表面存储器

优

①容量大,便宜

②记录介质,可重复使用

③信息可长期保存,甚至脱机存档

④非破坏性读出

缺

①存取速度慢

②复杂

③环境要求高

2,磁盘(机械硬盘)

磁盘——组成

1️⃣存储区域

①一硬盘,有多个记录面

②每个记录面,划为多条磁道

③每条磁道,划为多个扇区

④扇区(块),是磁盘读写的最小单位,即磁盘按块存取

磁头数(Heads)(记录面数)

①硬盘,有多少个磁头

②磁头,用于读取/写入记录面的信息

③一面,对应一磁头

柱面数(Cylinders)

①一面上,有几条磁道

②磁道垂直看下去,构成一个圆柱面

扇区数(Sectors)

每一条磁道上,有几个扇区

计算

磁盘的平均等待时间=max(转一圈)+min(不转)=转半圈

2️⃣硬盘存储器

硬盘存储器=磁盘驱动器+磁盘控制器+盘片

磁盘驱动器

①核心=磁头+盘片

②温彻斯特盘,可移动头固定盘片的硬盘存储器

磁盘控制器

①是硬盘存储器和主机的接口

②主流标准=IDE、SCSI、SATA

磁盘——性能指标

1️⃣容量, 一磁盘能存的字节总数

①非格式化容量,all 用了

②格式化容量,保留一部分以备份

(非格式化>格式化)

2️⃣记录密度,指盘片单位面积上记录的二进制的信息量

道密度,沿半径单位长度,有几个磁道

位密度,磁道单位长度上,能记录的位数

面密度=位密度*道密度

(同一扇区的磁道,存的位数一样)

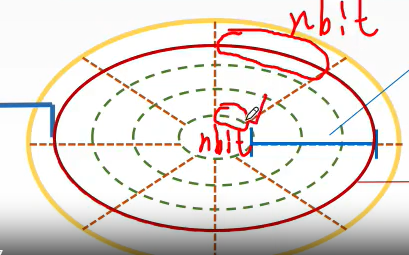

3️⃣平均存取时间

①磁盘控制器延迟

②寻道

③旋转延迟(一般转半圈)

④传输

4️⃣数据传输率

①磁盘,在单位时间内,向主机传送数据的字节数

②设磁盘转数=r(转/秒),每条磁道容量=N 个字节,则数据传输率=rN

磁盘——地址

磁盘——工作过程

①硬盘的主要操作=寻址、读盘、写盘

②每个操作,对应一个控制字

③读写操作,串行

工作过程

①取控制字

②执行控制字

3,磁盘阵列

磁盘阵列——定义

RAID( Redundant Array of Inexpensive Disks,廉价冗余磁盘阵列)

①将多个磁盘,组成一个独立的逻辑盘

②数据,在多个物理盘上分割交叉存储、并行访问

③存储性能好、可靠、安全

磁盘阵列——分类

越往下越安全

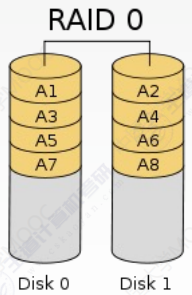

RAID0

逻辑上相邻的两个扇区,在物理上存到两个磁盘

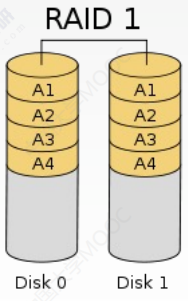

RAID1

很粗暴,存两份数据,浪费一半的空间

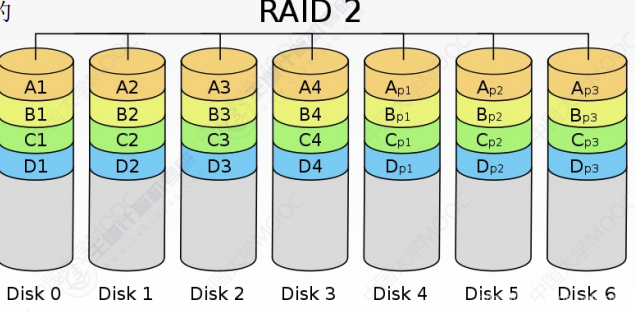

RAID2

①逻辑上连续的几个 bit,物理上分散在各个盘

②4bit 信息位+3bit 海明校验位,可纠正一位错

4,固态硬盘SSD

原理

基于闪存,属于电可擦除ROM(EEPROM)

组成

①闪存翻译层,逻辑块号—>页

②存储介质

闪存内部 ——>

读写特性

①以页为单位读写

②以块为单位擦除,擦干净的块,里面的页可写1次,读∞次

③随机访问,逻—>物,电路迅速定位

④读快,写慢

⑤若一页中有数据,先复制到别的新块,再擦整块,再写

对比机械硬盘

①SSD 读写快,机械硬盘有延迟

②SSD 安静、耐造、能耗低、贵

③SSD 的一块,被擦多了会坏,机械硬盘的扇区不会坏

磨损均衡技术

①擦除平均分布到各个块,提升寿命

②动态磨损均衡,写时,选累计擦除次数少的块

③静态磨损均衡,SSD 监测,让老块读,让新块写

3.5、高速缓冲存储器

1,Cache的原理

局部性原理

空间局部性,周围的,可能下次要用(数组)

时间局部性,现在用的,可能下次要用(循环)

局部性原理——怎么确定周围的

将主存分块,主存与Cache之间,以块为单位,进行数据交换

主存,块=页=页面=页框

Cache,块=行

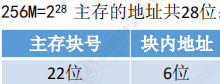

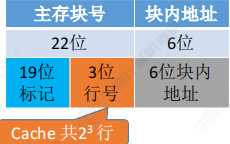

主存——地址

命中率H,CPU欲访问的信息已在Cache中的比率

未命中率(缺失率),M = 1 - H

Cache—主存系统的平均访问时间t

设

tc,访一次Cache的时间

tm,访一次主存的时间

则

①先访 Cache,Cache 未命中再访主存,t=H*tc +(1-H)(tc + tm)

②同时访 Cache 和主存,若 Cache 命中停访主存,t=H*tc +(1-H)tm

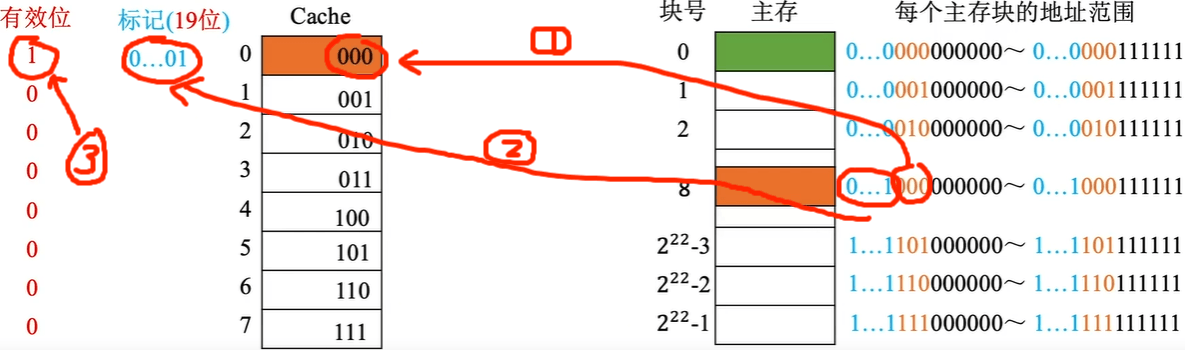

每次被访的主存块,一定被立即调入Cache

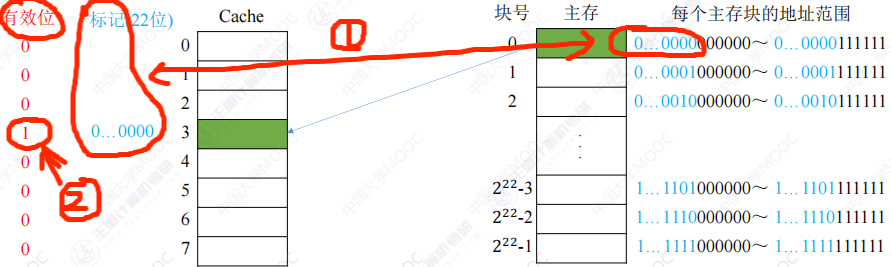

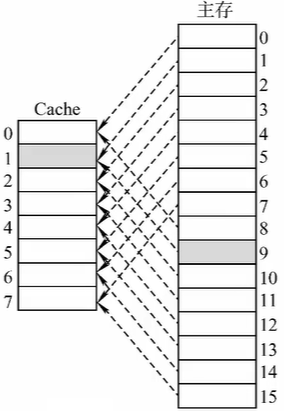

2,Cache和主存的映射方式

设

①主存大小=256MB,按字节编址

②Cache 行=8,行长为 64B

1️⃣全相联映射(随意放)

主存块,可放在Cache的任意位置

优

cache空间利用充分,命中率高缺

找标记慢,可能会对比all行的标记

全相联映射——访存过程

①主存块号,对比Cache的标记

②块号=标记

有效位=1,则Cache命中

③未命中

或有效位=0,则访主存

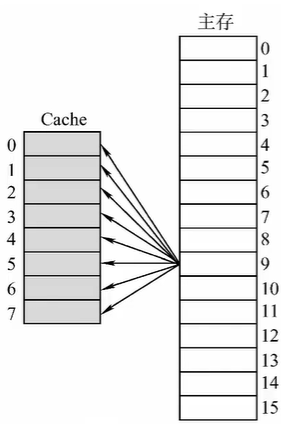

2️⃣直接映射(固定位置)

①每个主存块,只能放到一特定位置

②Cache 块号=主存块号 % Cache 总块数

优

对任一地址,只用对比标记,速度最快缺

cache空间利用不充分,命中率低

直接映射——访存过程

①用块号的后3位,确定Cache行

②块号的前19位=标记

有效位=1, 则Cache命中

③未命中

或有效位=0,则访主存

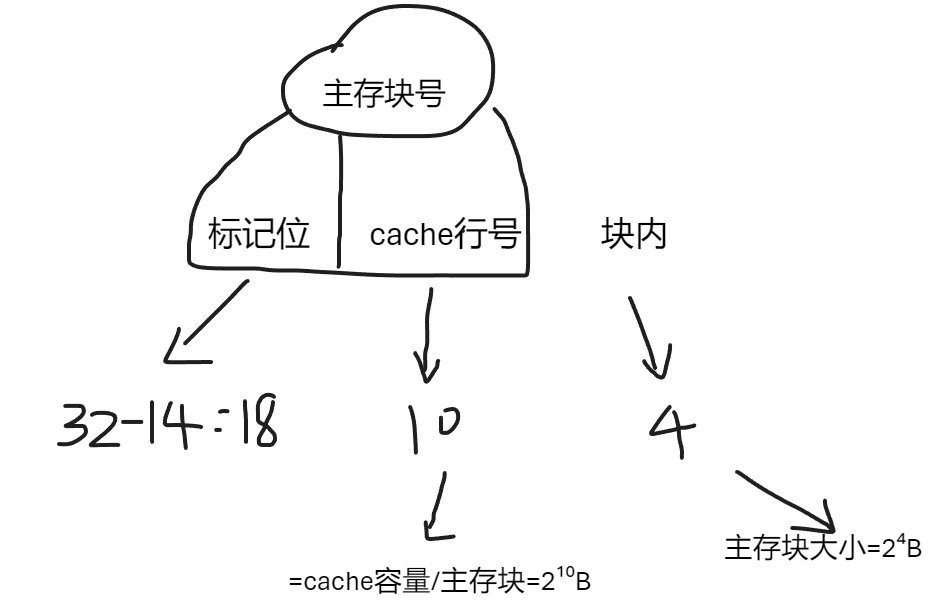

直接映射——例题(王道计组课本p144第17题)

主存地址=32位,按字节编址

主存块=16B,一字=4B,用写回法

则能4K字的cache的总容量的位数≥

cache的总容量,包括存储容量和标记阵列(有效位、标记位、一致性维护位、替换算法位)

(有效位、标记位一定存在)

该题中的标记阵列=有效位1、一致性维护位1

因此每个cahce标记项=18+1+1=20位

标记阵列容量=2¹⁰x20位=20K位

存储容量=4Kx32位=128K位

总容量=128K+20K=148K位

3️⃣n路组相联映射(特定分组)(每n个cache行为一组)

①Cache 块,分为多个组,每个主存块,可放到分组中的任一位置

②组号=主存块号 % 分组数

优

折中,综合效果好

组相联映射——访存过程

①用块号的后2位,确定所属分组号

②块号的前20位=标记

有效位=1, 则Cache命中

③未命中

或有效位=0,则访主存

3,Cache替换算法

抖动

频繁的换入换出,刚被换的块马上又被调入

1️⃣随机算法(RAND, Random)

若Cache已满,随机选一块替换

优

简单

缺

①没考虑局部性原理

②命中率低

③效果不稳定

2️⃣先进先出算法(FIFO, First In First Out)

若Cache已满,换最先被调入Cache的块

优

简单

缺

①没考虑局部性原理

②最先被调入 Cache 的块,可能频繁访

3️⃣近期最少使用算法(LRU, Least Recently Used )

为每个Cache块,设一计数器,记录它多久没访。Cache满后,换计数器max的

手算

机算

①命中时,设命中行的计数器=A,比A小的计数器+1,A=0

②未命中且有空闲行,新装入行的计数器=0,其余非空闲行全+1

③未命中且无空闲行,计数值max的行淘汰,新装行的计数器=0,其余全+1

(Cache块=2ⁿ,则计数器只需n位。且Cache装满后,所有计数器的值一定不重复)

优

①基于局部性原理,淘汰最久没访,合理

②效果优秀,Cache 命中率高

缺

若频繁访的主存块个数 > Cache行,可能抖动

4️⃣最不经常使用算法(LFU, Least Frequently Used )

为每个Cache块,设一计数器,记录它访过几次。Cache满后,换计数器min的

机算

①新块的计数器=0,之后每访问一次,计数器+1

②需替换时,选计数器 min 的

计数器min行,若有多个,选

①按行号递增

②或 FIFO

缺

①曾经常访的主存块,未来不一定用,未很好遵循局部性原理

②效果不如 LRU

4,Cache写策略

写命中

1️⃣写回法(write-back)

写命中时,只改Cache,当此cache块被换出时,才写回主存优

访存次数↓

缺

可能数据不一致

2️⃣全写法(写直通法,write-through)

写命中时,把数据同时写入Cache和主存,用写缓冲实现优

保证数据一致

缺

①访存次数↑

②速度慢

写缓冲(write buffer)

因为CPU写很快

①若写不频繁,效果就好

②若写频繁,写缓冲饱和,会阻塞

写不命中

1️⃣写分配法(write-allocate)

写不命中时,把主存块调入Cache,在Cache中改(搭配写回法)

2️⃣非写分配法(not-write-allocate)

写不命中时,只写入主存(搭配全写法使用)

(读未命中,才调入cache)

多级Cache

离CPU越近,速度快,容量小

远, 慢, 大

3.6、虚存

段页式、页式,和主存交换信息都是以页为单位

段式,更容易编译、改、保护、共享

快表,在cache,因为硬件nb,所以快

慢表,在主存,搜索算法

cache,SRAM,硬件处理,放的主存的一部分副本

快表TLB,SRAM,硬件、软件处理,放的页表page的一部分副本

四、指令系统

4.1、指令系统

1,定义

指令(机器指令)——定义

①机语的一个语句

②一组有意义的二进制代码

指令——地位

①指示计,执行某种操作的命令

②计,运行的 min 功能单位

一台计算机的所有指令的集合,构成该机的指令系统(指令集)

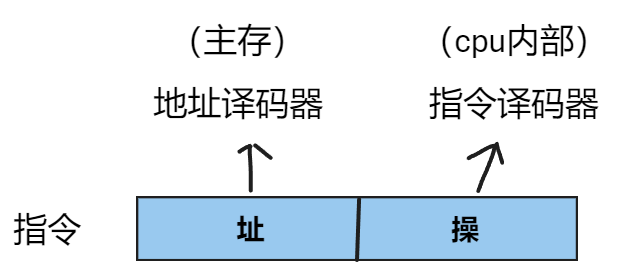

指令=操作码+地址码

2,分类——按地址码数目

指令——按地址码数目分类

单地址指令,只有1个地址码,但可能有1、2个操作数

2个操作数的情况,1个由地址码给出,1个由隐含寻址从ACC里面找

3,分类——按指令长度

指令——按指令长度分类

定长指令字结构:指令系统中,所有指令的长度都相等

变长指令字结构:指令系统中,各种指令的长度不等

指令字长(一般=字节的整数倍)

一条指令的总长度(可变)

机器字长

CPU进行一次整数运算,所能处理的位数(和ALU相关)

4,分类——按操作码长度

指令——按操作码长度分类

定长操作码

①所有指令的操作码,长度相同

②控制器的译码电路,简单

③灵活性低

(操作码=n位—>2ⁿ条指令)

可变长操作码

①各指令的操作码,长度可变

②控制器的译码电路,复杂

③灵活性高

5,分类——按操作类型

指令——按操作类型分类

1️⃣数据传送类

(1)数据传送

①LOAD,数据,主存—>寄存器

②STORE,数据,寄存器—>主存

2️⃣运算类

(2)算术逻辑操作

①算术,+-*/、求补、浮点运算

②逻辑,与、或、非、异或、位操作、位测试、位清除、位求反

(3)移位操作

3️⃣程序控制类

(4)转移操作(改变程序执行流)

①调用和返回,CALL 和 RETURN

②陷阱(Trap)指令例,循环指令、条件转移指令、子程序调用指令

4️⃣输入输出类

(5)输入输出操作

CPU寄存器,与IO端口之间的数据传送

6,扩展操作码

定长指令+可变长操作码——>扩展操作码指令格

(不同地址数的指令,用不同长度的操作码)

注

①不允许短码是长码的前缀

②各指令的操作码,不能重复

一般

①频率高的指令,操作码短

②频率低的指令,操作码长

↓指令译码+分析的时间

设地址长度=n,上一层留出m种状态,下一层可扩展出m×2!种状态

定长操作码

优

①简化硬

②指令译码和识别速度

缺

指令数↑ ,操作码占更多位,地址码位数受限

扩展操作码(不定长操作码)

优

在指令字长有限的前提下,可保持多种指令种类

缺

①指令译码和分析的难度

②控制器的设计,复杂

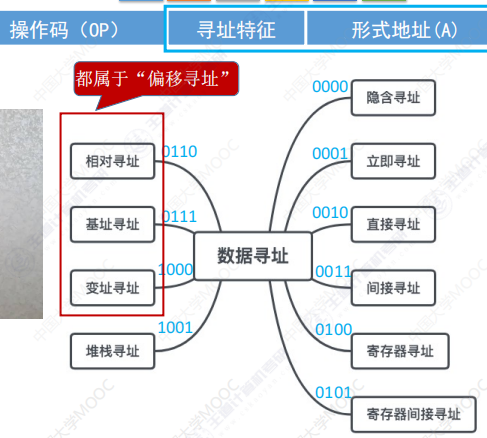

4.2、指令的寻址方式

1,指令寻址

PC的值=下条指令的地址

(PC放指令地址,指令的地址段放操作数地址)

①顺序寻址,PC + “1” —> PC

②跳跃寻址,由转移指令指出

采用不同寻址方式的目的

↓指令字长,扩大寻址空间,↑编程灵活性,但↑了指令译码的复杂度

(程序控制靠转移指令实现)

①直接转移,目标地址在指令中,执行时把地址码送入 PC

②间接转移,目标地址在寄存器、内存中

③相对转移,目标地址=PC 值+偏移量(偏移量一般在指令中)

④绝对转移,目标地址直接由指令、寄存器给出

2,数据寻址一

速度,立即寻址>寄存器寻址>直接寻址>间接寻址

位数

①PC,=存储器的字数(因为 PC 放的地址,即有多少个存储器)

②IR,=指令字长

1️⃣直接寻址

形式地址A=真实地址EA,即EA=A

访存次数

取指令1

执行指令1

优

①简单

②执行指令时,仅访存一次

缺

①A 的位数,决定寻址范围

②地址不易改

2️⃣间接寻址

形式地址≠真正地址

真正地址=操作数地址的地址,即EA=(A)

访存次数

取指令1

执行指令2

优

①扩大寻址范围

②便于编程序

缺

执行指令时,多次访存

3️⃣寄存器寻址

寄存器寻址——地址构成

操作数,寄存器,偏移量

访存次数

取指令1

执行指令0

优

①执行指令时,不访存,只访寄存器

②指令字短、地址位数短、速度快,支持向量/矩阵

缺

①贵

②寄存器个数有限

4️⃣寄存器间接寻址

形式地址=寄存器Ri的地址

真正地址=Ri中的地址

访存次数

取指令1

执行指令1

特点

比间接寻址快

5️⃣隐含寻址

优,利于↓指令字长,简化地址结构

缺,需↑ 存数/隐含地址的硬件

6️⃣立即寻址

形式地址A=操作数/立即数(一般用补码)

#,表示立即寻址

访存次数

取指令1

执行指令0

优

①执行指令时,不访存

②执行指令时间 min

缺

A的位数,限制立即数的范围

3,数据寻址二

起点不同

基址寻址:程序的起始存放地址

变址寻址:人决定

相对寻址:PC所指地址

1️⃣基址寻址

BR基址寄存器——base address register

EA——effective address

BR——类型

①专用(OS/管理程序,写内容)

②通寄来代替(用户选通寄,还是OS/管理程序,写内容)

基址寻址——定义

有效地址=cpu中基址寄存器的内容+指令中的形式地址A

即EA=(BR)+A

优

①扩大寻址范围

②用户不用管程序在主存的位置,便于多道程序并发运行

③浮动程序(程序在内存里动)

OS中的重定位寄存器,就是基址寄存器

2️⃣变址寻址

变址寻址——定义

有效地址=变址寄存器的内容+指令中的形式地址A

即EA= (IX)+A

IX——类型(用户写内容)

①专用

②通寄

优,适于循环、数组

3️⃣相对寻址

相对寻址——定义

有效地址=程序计数器PC的内容+指令中的形式地址A

即EA=(PC)+A

(A是相对于PC所指地址的位移量,可正可负,补码表示)

相对寻址——求偏移量范围

地址位数=n,偏移量范围=补码范围=[-2ⁿ⁻¹,2ⁿ⁻¹-1](注意留一位当符号)

相对寻址——例题

设相对寻址的转移指令占3个字节 第一字节为操作码,第二三字节为相对位移量,低字节地址为字地址的存放方式。每取出1B时候,(pc)+1->pc

①当pc当前值为240,要求——>290,则转移指令的第二、三字节的机器代码=

②当pc当前值为240,要求——>200,则转移指令的第二、三字节的机器代码=

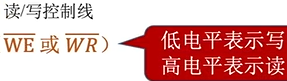

优

①便于程序浮动(代码在程序内部动)

②转移指令

无条件转移指令 jmp 2,不管PSW的各种标志位

条件转移指令bgt(无符号数A>B,则转移),转移条件=

因为A>B,故

①A-B 无进位、无借位,即 CF=0

②A-B≠0,即 ZF=0

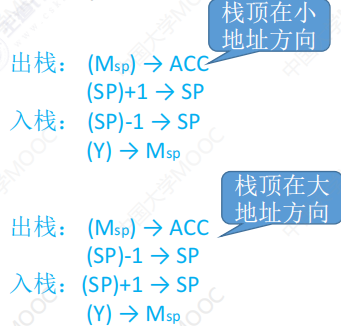

4,数据寻址三

堆栈寻址——定义

操作数放在堆栈中,隐含使用堆栈指针(SP)作为操作数地址

硬堆栈,寄存器,无需访存,贵

软堆栈,主存,访存一次,便宜

堆栈,可用于函数调用时,保存当前函数的相关信息

寻址——总结

EA操作数的真实地址

A操作数的形式地址

1,直接寻址,EA=A

2,间接寻址,EA=(A)

3,寄存器寻址,EA=寄存器A

4,寄存器间接寻址,EA=寄存器A——>寄存器B

5,隐含寻址,EA=隐含在操作码中

6,立即寻址,EA=操作数/立即数

1,基址寻址,EA=(基址)+A

2,变址寻址,EA= (IX)+A

3,相对寻址,EA=(PC)+A

4,堆栈寻址,堆栈指针实现

4.3、程序的机器代码表示

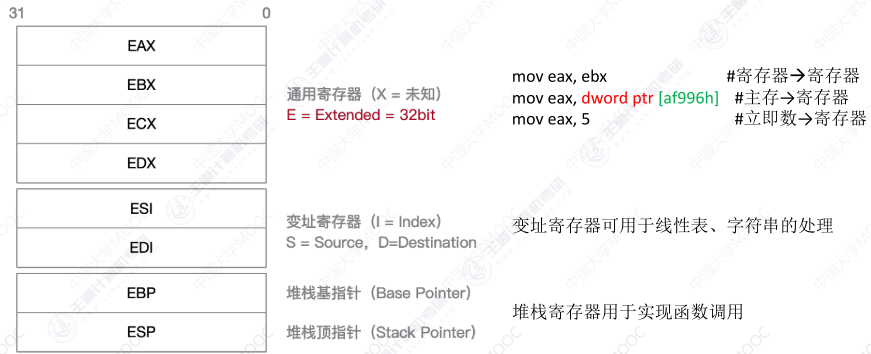

1,x86汇语指令概念

指令——作用

①改变程序执行流

②处理数据

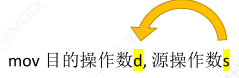

mov指令

将s,复制到d所指的位置destination不能=常数

source

内存的读写长度——表示

dword ptr——双字,32bit

word ptr——单字,16bit

byte ptr——字节,8bit

未指明,默认32bit

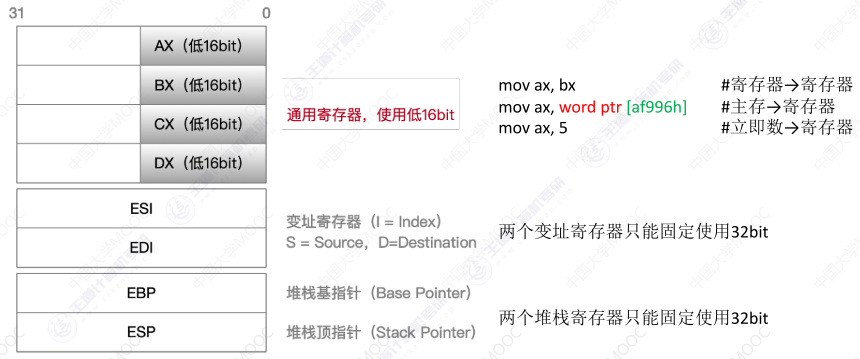

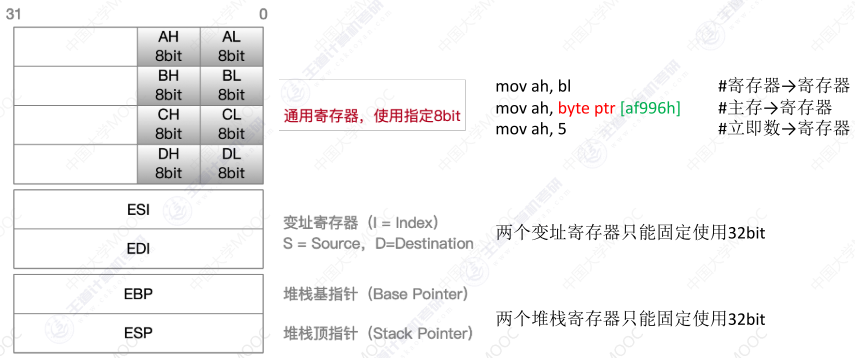

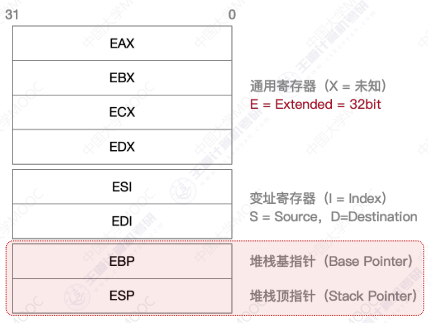

x86架构cpu——寄存器类型

2,常用x86汇编指令

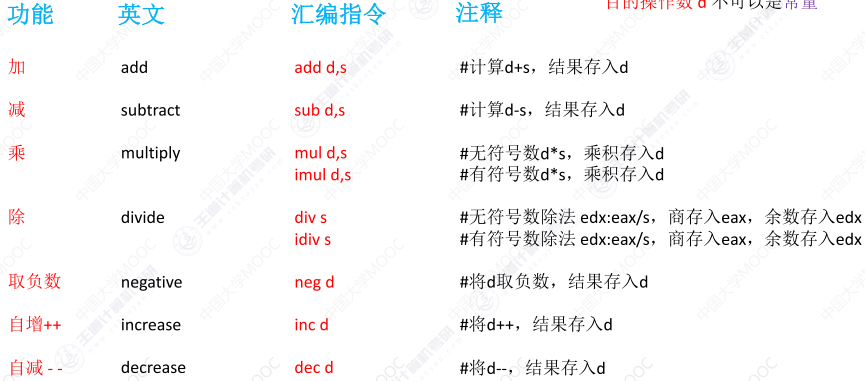

算数运算——指令

逻辑运算——指令

3,AT&T和Intel格式

AT&T,Unix、Linux的常用格式

Intel,Windows 的常用格式

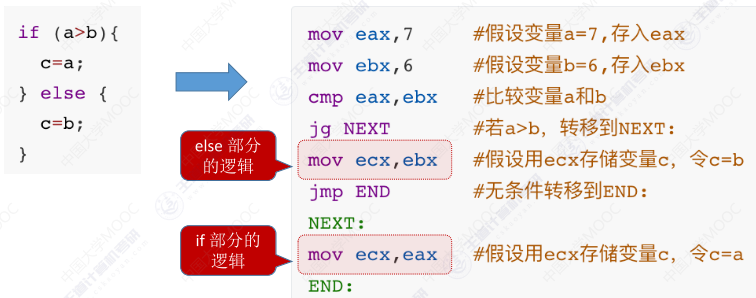

4,if语句

Intel x86 处理器中,程序计数器PC,被称为IP(Instruction Pointer)

无条件转移指令,jmp <地址>,让PC无条件转移至 <地址>

<地址>——类型

①常数

②来自于寄存器

③来自于主存

④用“标号”锚定(≈goto语句)

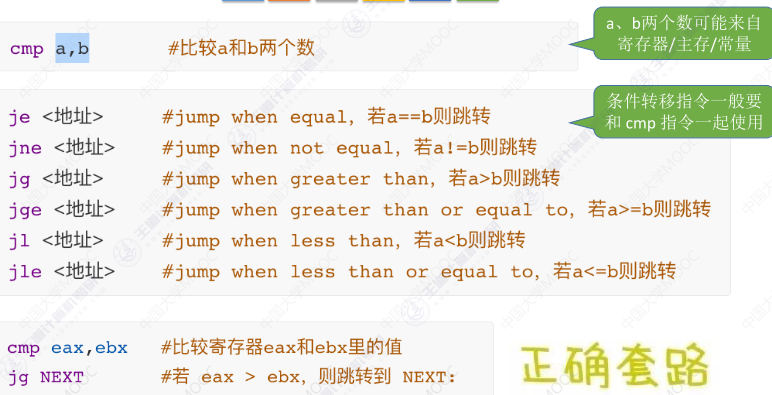

各种指令——作用

例子

汇语,函数名=“标号”,标注该函数指令的起始地址

cmp a,b

本质上是a-b,并生成标志位OF、ZF、CF、SF

ALU每次运算的标志位,都自动存入PSW程序状态字寄存器(Intel叫,标志寄存器)

OF,溢出置1,否则置0

SF,结果=负,置1,否则置0

ZF,结果=0,置1,否则置0

CF,进位/借位时置1,否则置0

OF(Overflow Flag)(溢出)

SF(Sign Flag)(符号)

ZF(Zero Flag)(零)

CF(Carry Flag)(进位/借位)

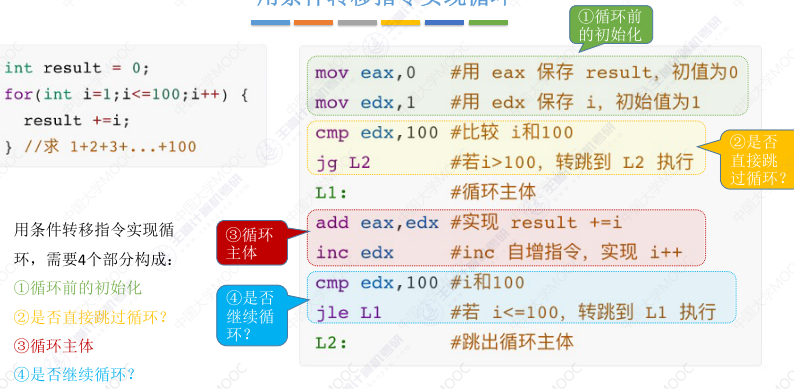

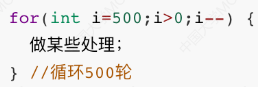

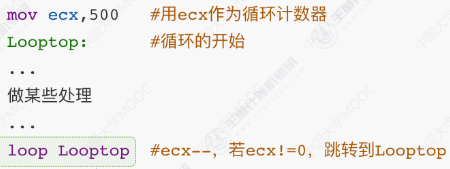

条件转移指令,实现循环

loop指令,实现循环

①loop 更简洁

②loop能做的,条件转移指令也能做

loopx 指令

loopnz——当 ecx!=0 && ZF==0 时,继续循环

loopz——当 ecx!=0 && ZF==1 时,继续循环

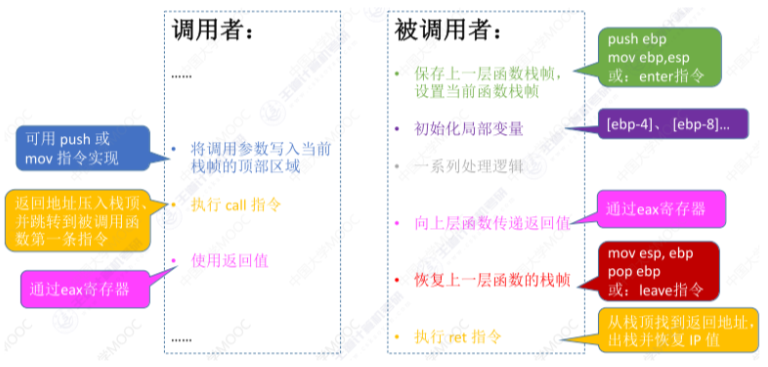

5,高语的函数调用

函数调用指令: call <函数名>

函数返回指令: ret

call——作用

①把IP旧值,压栈到栈顶(=push IP)

②设IP新值,无条件转移至被调用函数的第一条指令(=jmp add)

ret指令——作用

从栈顶,找到 IP旧值,出栈,并恢复IP寄存器

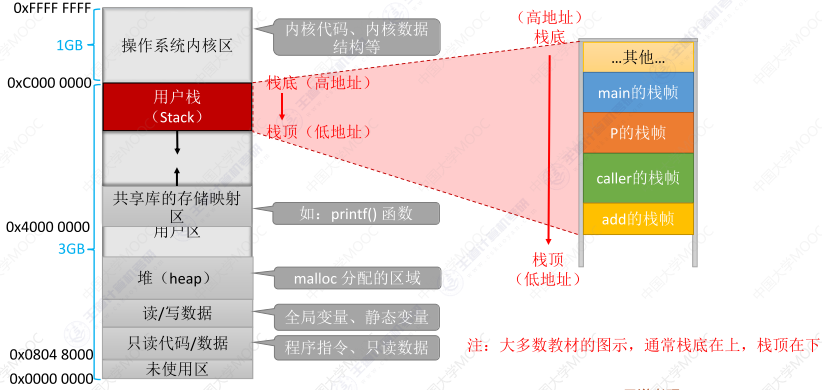

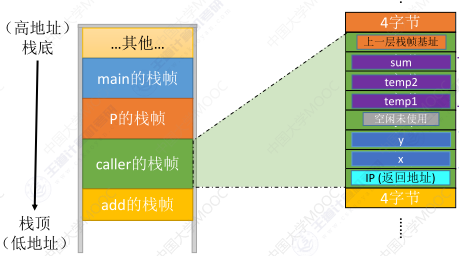

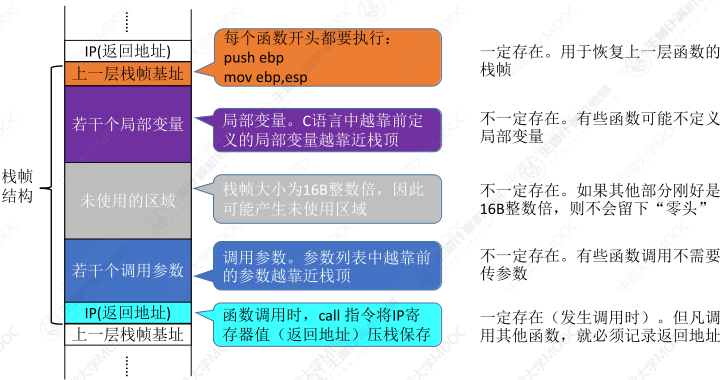

函数调用栈——内存中的位置

ebp,指向当前栈帧的底部

esp,指向当前栈帧的顶部

(cpu内部只有1个ebp和1个esp)

x86系统中,默认以4字节为栈的操作单位

访问栈帧——方法

1️⃣push+pop指令

push A

pop B

A=立即数、寄存器、主存地址

B=寄存器、主存地址

2️⃣mov指令,,结合 esp、ebp 指针访问栈帧数据

用加、减指令,即 add、sub 改栈顶指针 esp 的值

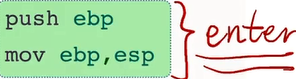

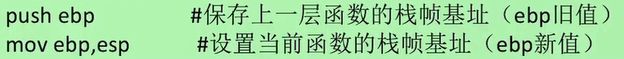

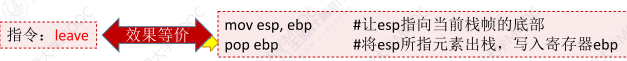

6,函数调用的机器级表示

每个函数开头的例行处理

函数调用时——如何切换栈帧

函数返回时——如何切换栈帧

除了main函数,all函数的汇编代码结构都一样

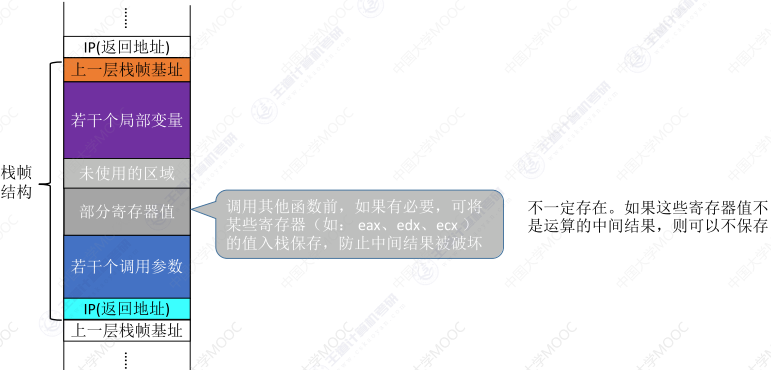

栈帧——内容

①空闲区,gcc编译器,将栈帧大小设=整数*16B

②局部变量,在栈帧底部

③调用参数,在栈帧顶部

④栈帧最底部,=上一层栈帧基址(ebp 旧值)

⑤栈帧最顶部,=返回地址(当前函数的栈帧除外)

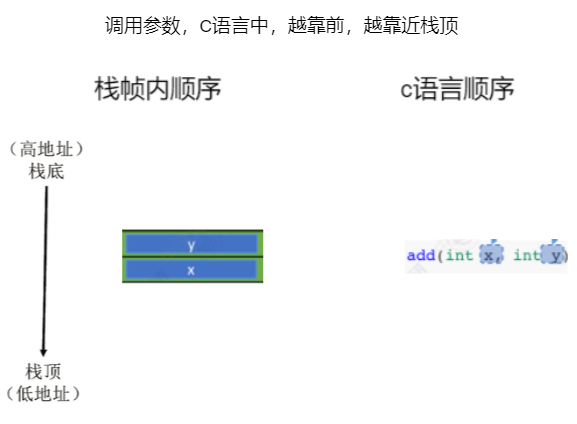

栈帧——内容顺序

技巧

esp-数,局部变量

ebp+数,调用参数

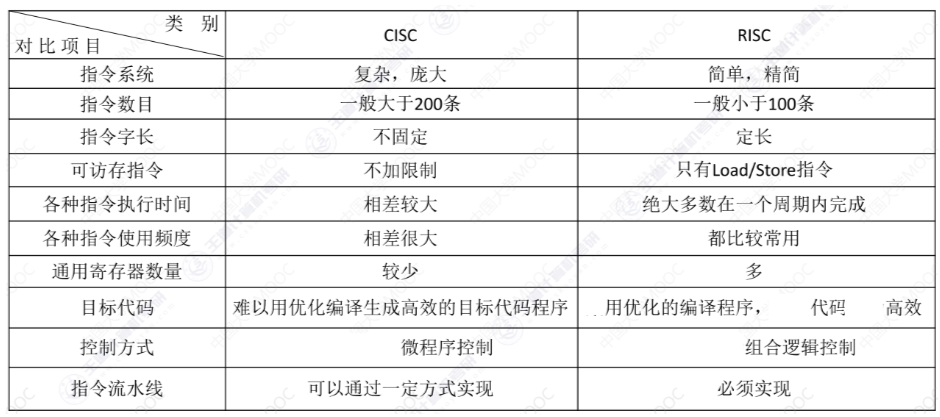

4.4、CISC和RISC

指令——设计方向

1️⃣CISC(Complex Instruction Set Computer)

①类比:有很多库函数的 C 语言

②思路:一指令,完成一复杂的基本功能

③x86 架构,用于笔记本、台式机

2️⃣RISC(Reduced Instruction Set Computer)

①类比:没有库函数的 C 语言

②思路:一指令完成一基本动作,多指令组合完成一复杂的基本功能

③ARM 架构,用于手机、平板

80-20规律

典型程序中80%的语句,仅使用cpu中20%的指令

对比图

五、中央处理器

5.0、课后题总结

0,其他

1,cpu内部

运算器——组成

(1)通寄组(AX、BX、CX、DX、SP)

①放操

②编号

(2)ACC(属于通寄,通寄是可编程指定多种功能的寄存器)

放ALU的结果

(3)移位寄存器SR

①放操

②data 移位

(4)暂存寄存器(对应用程序员透明)

放数据总线、通寄的操

(5)PSW

控制器——组成

①PC,指令总是根据PC从主存中读出

②IR

③指令译码器

④微操作信号发生器

⑤时序系统

⑥MAR

⑦MDR

2,PC

PC的值,在cpu执行时(取值T)修改

PC+1——怎么实现

①自增

②转移指令

(+1,指+1个指令长度)

完成一个无条件跳转指令,PC修改的次数

①取值 T 结束,PC+1

②执行 T 中,PC=跳转地址

机器指令中,不能显式使用PC,因为是硬件实现

3,透明

程序员看得见

①PSW

②PC③基址寄存器

④通寄组

程序员看不见(因为都在cpu内部)

①IR

②MAR

③MDR

4,位数

PC——怎么表示指令地址

①字节地址,PC 位数=存储器地址位数=存储器容量

②字地址,按边界对齐,PC 位数=存储器地址位数 - log₂(指令字长的字节数)

①MAR,位数=PC 位数

②MDR,位数=存储字长

③通寄,位数=机器字长

④n 位 cpu,n=数据总线位数=cpu 位数=cpu 一次能处理 data 的位数

5,PSW

PSW,不需编号

PSW——放的标志的种类

(1)ZF、OF、SF、CF

(2)中断标志、陷阱标志

执行条件转移指令,先看PSW,判转移条件✔ or X

6,周期

机器T——定义

①由存取 T 确定

②完成一个基本操作,所需的时间

③通过一次总线事务访问,访存一次/IO 一次,所需的时间

存取T,存储器一次读/写,所需的时间

DMA方式,每传一个data,需一个存取T

7,字长

指令字长——定义

①和机器字长无关系

②=整数倍*存储字长

③或=整数倍*B

④若指令字长=存储字长,则机器T=取指T

5.1、cpu的功能与基本结构

1,cpu功能

①指令控制。取、分析、执行指令,即程序的顺序控制

②操作控制。一指令的功能=多个操作信号的组合来实现。cpu 管理并产生由内存取出的每条指令的操作信号,把各种操作信号送往相应的部件

③时间控制。为每条指令按时间顺序,提供应有的控制信号

④数据加工。算、逻运算

⑤中断处理。处理异常情况、特殊请求

cpu每执行完一条指令,就会检查一次中断处理

cpu——基本结构

2,运算器——基本结构

①算逻单元:算、逻运算

②通寄组:AX、BX、CX、DX、SP(指向栈顶的指针),放操作数、各种地址信息

③暂存寄存器:暂存主存读来的数据,该数据不能放在通寄,它会破坏原有内容

④累加寄存器:通寄,暂存 ALU 的结果,实现加法

⑤程序状态字寄存器:保留各种状态信息,PSW 中的这些位参与并决定微操作的形成

⑥移位器:对运算结果移位

⑦计数器:控制乘除的操作步数

专用数据通路方式

按指令执行时,数据和地址的流动方向,连线

优,性能高,基本无数据冲突

缺,结构复杂,硬件量大,不易实现

专用数据通路方式——问题

1️⃣线数量多,会复杂

2️⃣直接连线,相当于多个寄存器同时输入①多路选择器

②三态门1通,0不通

cpu内部单总线方式

把all寄存器的输入端和输出端,都连到一条公共通路上

优,结构简单,易实现

缺,数据传输,多冲突,性能低

3,控制器——基本功能

①程序计数器:cpu 按 PC 的内容,去主存中取指。因程序中指令顺序执行,所以 PC 自增

②指令寄存器:存当前执行的指令

③指令译码器:对操作码字段进行译码,向控制器提供操作信号

④微操作信号发生器(有组合逻辑型、存储逻辑型):根据 IR 的内容(指令)、PSW、时序信号,产生控制整个计系所需的控制信号

⑤时序系统:产生时序信号,由统一时钟(CLOCK)分频得到

⑥存储器地址寄存器:放访存地址

⑦存储器数据寄存器:放往主存写入、从主存读出的信息

5.2、指令执行过程

1,指令周期

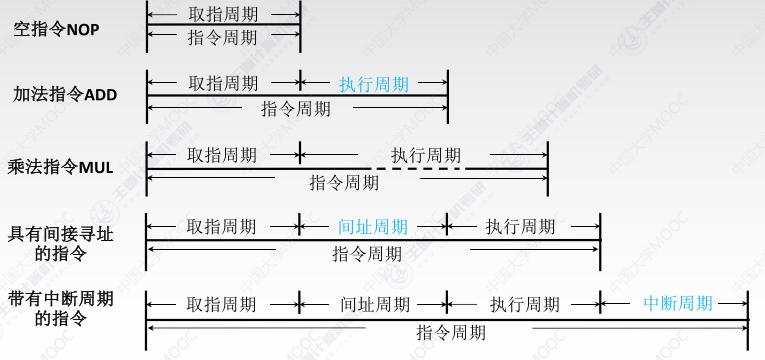

指令周期

CPU从主存中,每取出并执行一条指令所需的全部时间

(即指令T=取指T+执行T)

指令T=多个机器T

机器T(CPU周期)=多个时钟T(节拍、T周期、CPU时钟T,是CPU操作的最基本单位)

每个指令T内,机器T数可不同

每个机器T内,节拍数也可不同

2,指令周期——数据流

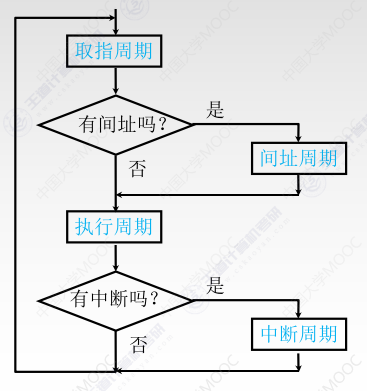

指令周期——流程

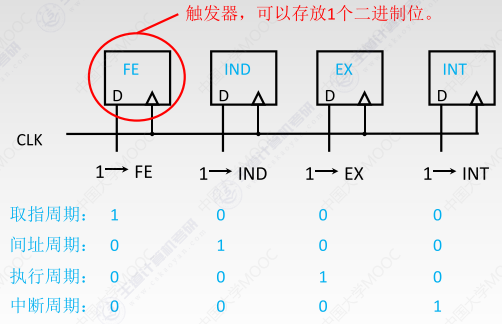

cpu——区分工作周期

都访存,但目的不同

①取指周期,取指令(控制器自动进行,访存一次)

②间址周期,取操的有效地址EA(根据寻址方式的不同,不是必需的步骤)*这中间有一个过程,指令译码器,把操作码——>控制信号

③执行周期,取操作数

④中断周期,保存程序断点

1️⃣取指T——步骤

①当前指令地址,送至地址寄存器,记=(PC) →MAR

②CU发出控制信号,经控制总线传到主存,记=1 → R(读)

③将MAR所指主存中的内容,经数据总线送入MDR,记=M(MAR) →MDR

④将MDR中的内容(此时是指令)送入IR,记=(MDR) → IR

⑤CU发出控制信号,形成下一条指令地址,记=(PC)+1 → PC

2️⃣间址T——步骤

①将指令地址码,送入MAR,记=Ad(IR) →MAR 或 Ad(MDR) →MAR

②CU发出控制信号,让主存读,记=1 → R

③将MAR所指主存中的内容,经数据总线送入MDR,记=M(MAR) →MDR

④将有效地址,送至指令的地址码字段,记=(MDR)→ Ad(IR)

3️⃣执行T——步骤

无统一的的数据流向

4️⃣中断T——步骤

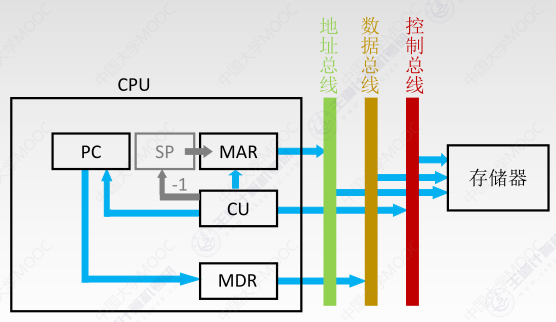

①CU控制,使SP-1,改后的地址送入MAR,记= (SP)-1 → SP,(SP) →MAR

本质,将断点存入某单元,其地址为a,故可记=a →MAR

②CU发出控制信号,让主存写,记=1 →W

③将断点(PC内容) 送入MDR,记=(PC) →MDR

④CU,将中断服务程序的入口地址(由向量地址形成部件产生)送入PC,记=向量地址→ PC

CU的输入信号来源

①指令译码器(主要)

②时钟(主要)

③执行单元的反馈信息,即标志

中断:暂停当前任务,去完成其他任务

为了能恢复当前任务,用堆栈保存断点。SP-栈顶地址,进栈=先改指针,后存数据

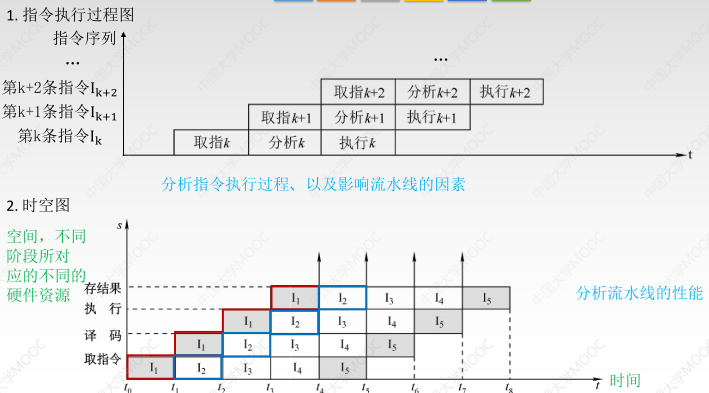

3,指令执行方案

指令执行方案

一个指令周期,包括多个时间段(执行步骤),每个步骤完成一部分功能,几个依次执行的步骤,完成这条指令的全部功能

1️⃣单指令周期

all指令,用相同的执行时间完成

特点

①串行执行

②指令 T 取决于执行时间 max 的指令

③短时间即可完成的指令,要用最长的周期来完成,↓速度

2️⃣多指令周期

不同指令,用不同的执行步骤完成

特点

①串行执行

②用不同个数的时钟周期,完成不同指令的执行过程

③硬件设计复杂

3️⃣流水线方案

每一个时钟周期启动一条指令,尽量让多条指令同时运行,但各自处在不同的执行步骤中

特点

并行执行

5.3、数据通路的功能和基本结构

1,数据通路-单总线结构

数据通路——基本结构

1. CPU内部单总线方式

2. CPU内部多总线方式

3. 专用数据通路方式

单总线

寄存器的输入、输出端都在一条公共路上,而且一时钟T内,只能对一个寄存器操作

内部总线,同一部件,CPU内部连接各寄存器及运算部件之间的总线

系统总线,同一台计系的各部件,如CPU、内存、通道和各类I/O接口间互相连接的总线

用cpu内部总线——特点

①结构简单

②性能低

③冲突多

不用cpu内部总线——特点

①结构复杂

②硬件量大

③性能高

④基本无冲突

1.寄存器之间数据传送

把PC内容送至MAR,实现传送操作

(PC)→Bus PCout有效,PC内容送总线

Bus→MAR MARin有效,总线内容送MAR

2.主存与CPU之间的数据传送

CPU从主存读指令,实现传送操作

(PC)→Bus→MAR PCout和MARin有效,现行指令地址→MAR

1→R CU发读命令(通过控制总线发出)

MEM(MAR)→MDR MDRin有效

MDR→Bus→IR MDRout和IRin有效,现行指令→IR

3.执行算术或逻辑运算

加法指令

Ad(IR)→Bus→MAR MDRout(或AdIRout)和MARin有效

(因为取值先取到MDR,再复制到IR)

1→R CU发读命令

MEM(MAR)→数据线→MDR MDRin有效

MDR→Bus→Y MDRout和Yin有效,操作数→Y

ALU的两个输入信号必须同时有效

2,数据通路-专用通路结构

通过例题学习

组合逻辑元件(操作元件),不含存储信号,输出只取决于当前输入

①加法器

②ALU

③译码器

④多路选择题

⑤三态门

时序逻辑元件(状态元件),含存储信号

①通寄组

②PC

③psw

5.4、控制器的功能和工作原理

1,硬布线控制器

注

①一个节拍内,可并行完成多个微操作

②同一微操作,可能在不同指令的不同阶段被用

③不同指令的执行周期,所需节拍数不同

硬布线控制器——设计步骤

1. 分析每个阶段的微操作序列(取值、间址、执行、中断四个阶段)

据指令操作码、目前的机器周期、节拍信号、机器状态条件,确定该节拍下发出哪些微命令

2. 选择CPU的控制方式

3. 安排微操作时序

原则一,微操作的先后顺序不能改

原则二 ,被控对象不同的微操作,尽量安排在一个节拍内完成

原则三 ,t短的微操作,尽量安排在一个节拍内完成并允许有先后顺序

4. 电路设计

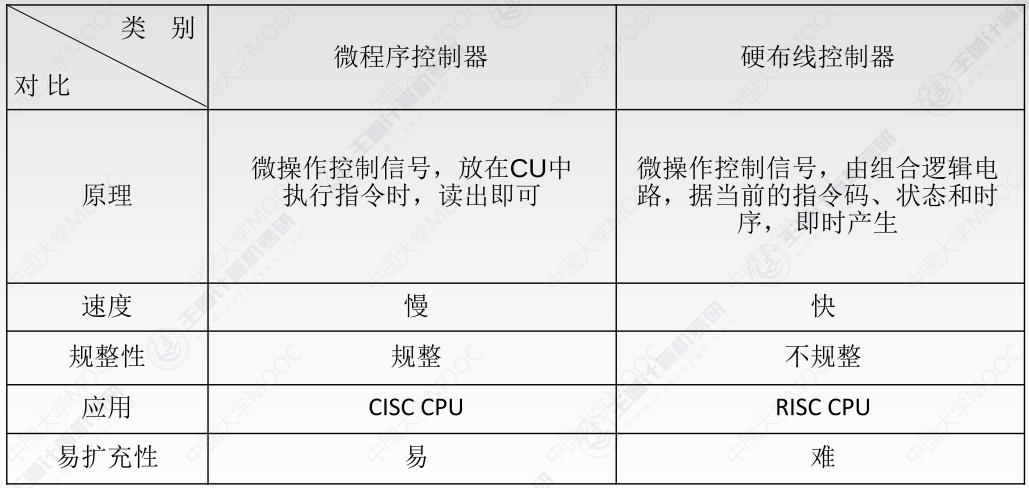

硬布线控制器——特点

①指令越多,越复杂,一般用于 RISC(精简指令集系统)

②扩充新指令,设计要大改,故扩充指令较困难

③用纯硬件实现控制,执行速度很快

④微操作控制信号由组合逻辑电路即时产生

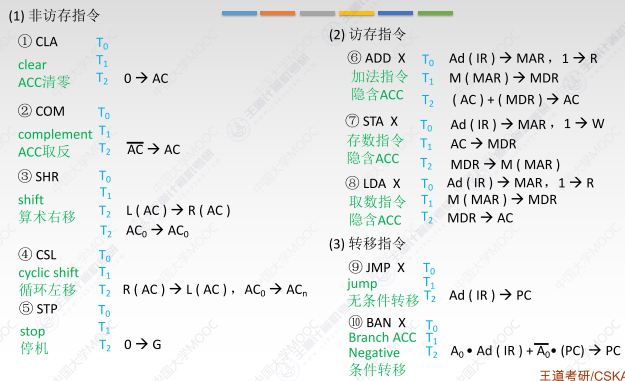

各种指令

2,微程序控制器

硬布线控制器VS微程序控制器

①速度,硬>微,因为微要从 CM 中读微指令

②时序复杂度,硬>微,因为微只需按时钟 T 顺序执行指令

③灵活性,硬<微,微修改更方便

易混淆概念——复杂

程序:由指令序列组成

微程序:由微指令序列组成,每一种指令对应一个微程序

指令,对程序执行步骤的描述

指令,对微指令功能的封装

微指令,对指令执行步骤的描述

易混淆概念——简单

程序,一堆机器指令

微程序,一堆微指令

指令,对应≥1个微指令,=1个微程序

微指令,对应≥1个微操作(又称微命令)

主存,放机器指令

控制存储器CM,放微指令(微程序控制器的核心,是cpu的一部分,由ROM组成)(按地址寻访,厂家写好all微程序)

指令T,从主存中,取出、执行一机器指令的t

微指令T,从控制器存储器中,取出一微指令,并执行微操作的t

all指令的取指T、间址T、中断T所对应的微指令序列都一样

取指T的微程序段是公用的,故机器指令=n,则CM中微程序段≥n+1

(若逻辑上把取指T、执行T当作整体,则CM中微程序≥n)

早期、物联网设备的CPU,可无间接寻址和中断功能,故不含间址T、中断T的微程序

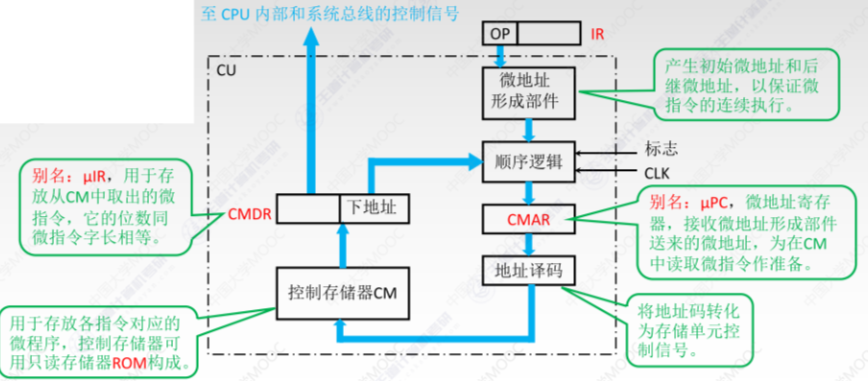

微程序控制器——基本结构

upc不能代替pc,upc在微程序中指出下一条微指令的寄存器

3,微指令的格式

相容性微命令:可并行完成的微命令

互斥性微命令:不允许并行完成的微命令

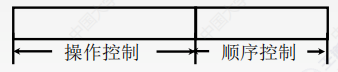

微指令——基本格式

微指令——格式类型

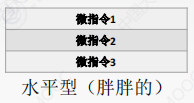

1. 水平型微指令

一水平型微指令,执行多个可并行的微操作

优,微程序短,速度快

缺,微指令长,编程麻烦特,控制信号经编码产生

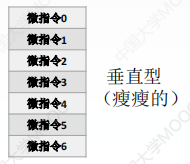

2. 垂直型微指令

一垂直型微指令,执行一个微操作,由微操作码规定其功能

优,微指令短,易编程

缺,微程序长,速度慢特,微指令中有微操作码,≈机器指令格式

3. 混合型微指令

用垂直型,加一些简单的并行操作

优

微指令较短,易编程

微程序不长,速度快

4,微指令的编码方式

(1) 直接编码(直接控制)

在微指令的操作控制字段中,每一位代表一个微操作,1-有效

优,简单、直观,速度快,并行性好

缺,微指令长,n个微操作,需微指令=n位,使CM大

(2) 字段直接编码

微指令,分段,每段经译码后发出控制信号

微命令字段分段——原则

①互斥性微命令,在同一段;相容性微命令,在不同段内

②每段的位要少,否则译码复杂

③每段留出一个状态,表示本段不微操作

优,缩短微指令字长

缺,译码后,再微操作,比(1)慢

字段直接编码——做题

字段直接编码需要多留一串,以表示不输出

即,微指令种类=2²个,那么位数应=2³

(3) 字段间接编码(隐式编码)

一字段的某些微命令,需另一字段的微命令来解释

优,进一步缩短微指令字长

缺,并行弱,速度更慢

5,微指令的地址形成

1. 微指令的下地址字段指出

断定方式

微指令格式中,设一下地址字段,由微指令的下地址字段直接指出后继微指令的地址

2. 由机器指令的操作码形成

当机器指令取至IR后,微指令的地址,由操作码经微地址形成部件形成

3. 增量计数器法

( CMAR ) + 1——>CMAR

4. 分支转移

转移方式:指明判别条件转移地址:指明转移成功后的去向

5. 通过测试网络

6. 由硬件产生微程序入口地址

机器指令的操作码,形成微程序入口地址

6,微程序控制单元的设计

微程序控制单元——设计步骤

1. 分析各阶段的微操作序列

2. 写出微操作、节拍安排

(1) 各T所需的微操作

(2) 微程序控制器特有的微操作

①取指周期

Ad (CMDR) —>CMAR (每条微指令结束之后都需要进行)

OP (IR) —>微地址形成部件—>CMAR(取指周期的最后一条微指令完成后,根=据操作码,确定执行周期的微程序首地址)

②执行周期

Ad(CMDR) —>CMAR (每条微指令结束之后都需要进行)

3. 确定微指令格式

①微操作个数决定编码方式,从而确定操作控制字段的位数

②CM 中微指令总数决定下地址的位数

③操作控制字段与下地址的位数之和为微指令字长的位数

4. 编写微指令码点

据操作控制字段的微操作,编各条微指令的码点

微程序设计——分类

1. 静、动态微程序设计

静,微程序不变,用ROM

动,改微指令、微程序—>改机器指令(利于仿真,用EPROM)

2. 毫微程序设计

毫微程序,解释微程序

硬布线VS微程序

5.6、指令流水线

1,概念

指令流水

一指令的执行过程,可分成多阶段。计不同,分法也不同

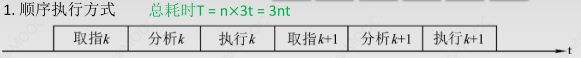

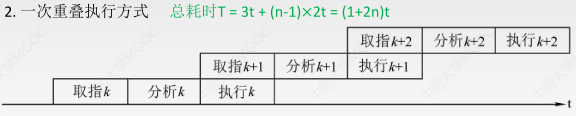

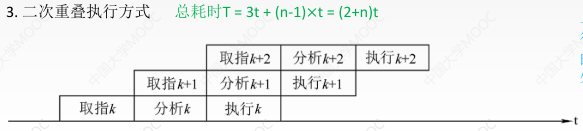

指令流水——方式(设取指=分析=执行=t)

传统冯·诺依曼机,用串行执行方式

优,控制简单,硬件代价小

缺,速度慢,whenever,cpu中只有一指令在执行,利用率低

优,t比顺缩短了1/3,利用率↑

缺,硬件开销大,更复杂

t比顺缩短了2/3

各指令的执行过程,也可分成4/5个阶段,5常见

流水线——表示方法

2,性能指标

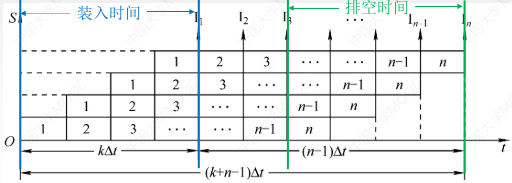

以下都是理想情况

①各阶段t相同

②各阶段结束可立即进入下一阶段

一指令的执行,分为k个阶段,每个阶段耗时Δt ,Δt =一个时钟T

1. 吞吐率TP

定义:单位时间内,流水线所完成的任务数,或输出量

①设任务数=n,处理n个任务耗时=Tk,则吞吐率

②,则实际吞吐率

③n→∞时,最大吞吐率

2. 加速比S

(设T0=不用流水线的t(即顺序执行),Tk=用流水线的t)

定义:完成同样一批任务,T0 / Tk①

②1个任务耗时=kΔt,n个任务耗时

,

则实际加速比

③n→∞时,最大加速比Smax=k

3. 效率E

定义:流水线的设备利用率①时空图上,

②n→∞时,最高效率Emax=1

3,影响因素

各阶段耗时一样

流水线每一段,都有一缓冲寄存器(锁存器),保存本流水段的执行结果,提供给下一流水段用

影响因素

1. 结构相关(资源冲突)

多指令,在同一时刻,争用同一资源

解决

①后一指令暂停一 T

②资源重复配置:包括数据存储器和指令存储器

2. 数据相关(数据冲突)

一程序中,前一指令执行完,才能执行后一条指令

解决

①硬件阻塞(stall)、软件插入“NOP”

②数据旁路技术(又称转发机制)

③编译优化,用编译器,调顺序

3. 控制相关(控制冲突)

转移指令、其他改变PC值的指令,造成断流

解决

①转移指令分支预测=简单预测、动态预测

②预取转移成功、不成功,两个控制流方向上的目标指令

③加快和提前形成条件码

④↑ 转移方向的猜准率

4,流水线——分类

1.部件功能级、处理机级、处理机间级流水线

①部件功能级,再细分

②处理机级,把一指令解释过程分成多个子过程

③处理机间,一种宏流水,每一 cpu 完成某一专门任务

2.单功能流水线、多功能流水线

①单功能,只实现一种专门功能

②多功能,可同时或不同时,实现多种功能

3.动态流水线、静态流水线

①静,各段,只能 A 运算

②动,同一时间内,某段 A 运算时,另一段 B 运算

4.线性流水线、非线性流水线

①线,每段只允许经过一次,无反馈回路

②非线,某些段将多次通过流水线,用于线性递归运算

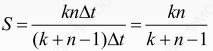

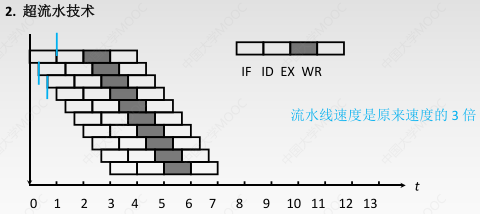

5,流水线——多发技术

①每个时钟 T,可并发多条独立指令

②不能调顺序

③要多个功能部件

④用编译优化搭配指令

①在一个时钟 T 内,再分段

②不能调顺序

③在一个时钟 T 内,一功能部件用多次

④靠编译程序解决优化问题

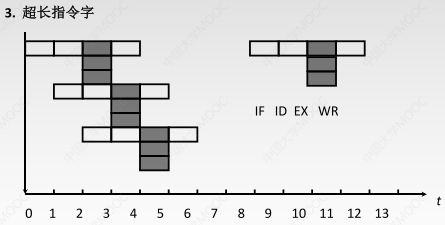

①编译程序挖出指令的并行性,把可并行的指令组合

②有多个操作码字段的超长指令字

③用多个处理部件

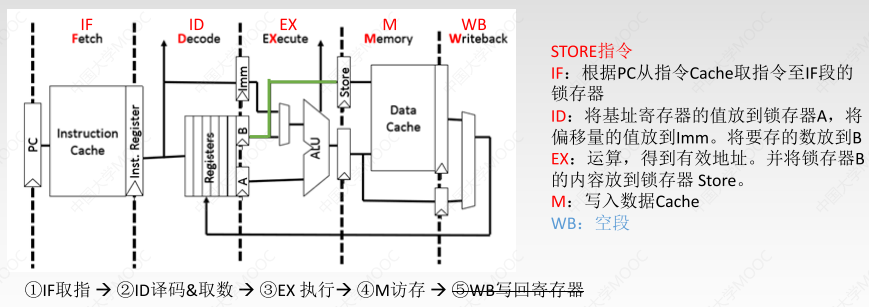

6,五段式指令流水线

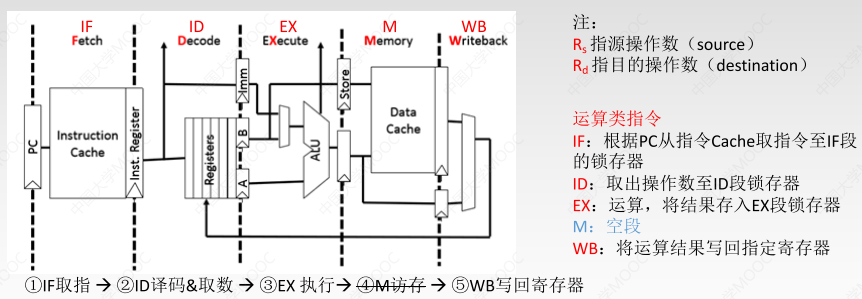

1. 运算类指令

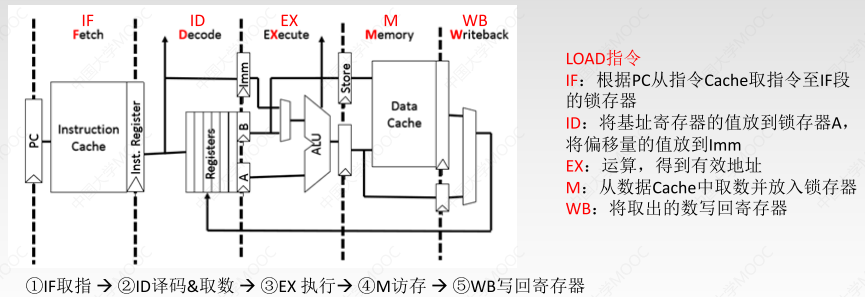

2. LOAD指令

RISC处理器,取数LOAD、存数STORE指令,才能访存

3. STORE指令

4. 条件转移指令

5. 无条件转移指令

WrPC段,耗时比EX段短,可放在在EX段完成

WrPC段,越早完成,就越能避免控制冲突

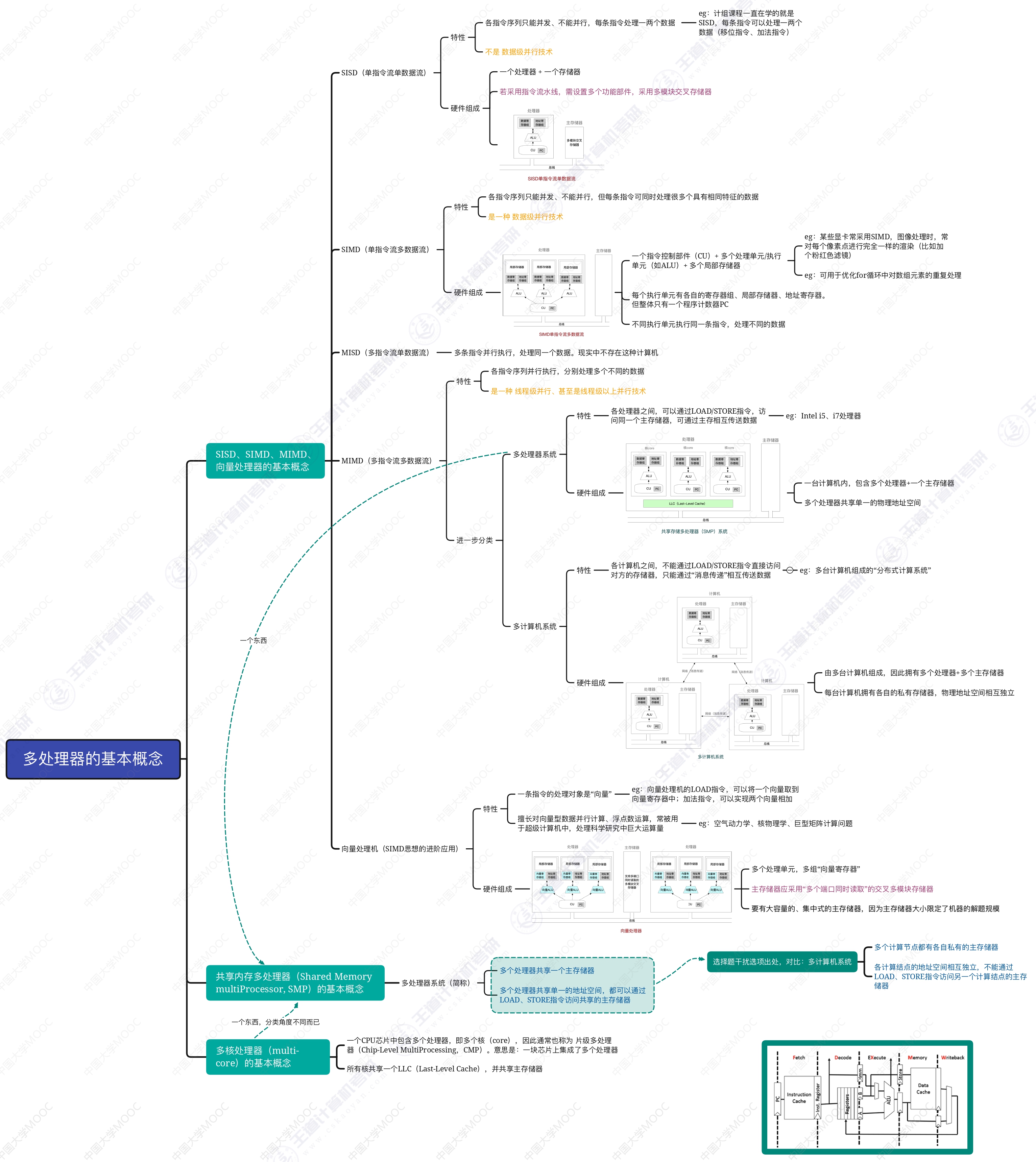

5.7、多处理器

1,概念

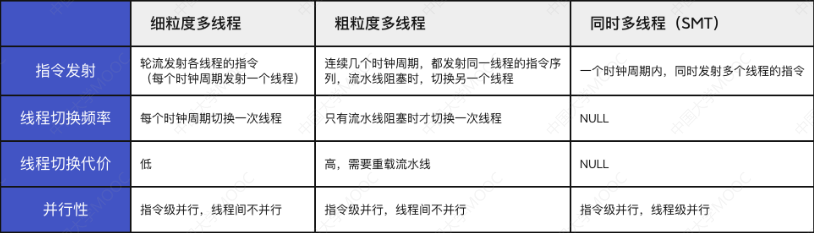

2,硬件多线程

六、总线

6.1、总线概述

1,基本概念

总线的物理实现

同一时刻,只能一个部件发数据,可有多个部件接数据

总线

一组能为多个部件,分时共享的公共信息传送线路

早期计算机,因为外设少,大多用分散连接方式,不易实现随时增减外设

总线——特性

①机械特性:尺寸、形状、管脚数、排列顺序

②电气特性:传输方向和有效电平范围

③功能特性:每根传输线的功能(地址、数据、控制)

④时间特性:信号的时序关系

2,总线——分类

1️⃣按数据传输格式

优

①只要一条传输线,便宜,用于长距离传输

②用于计内部时,可省空间

缺

①因为数据每次只传 1bit,要进行拆卸和装配

②要考虑串行-并行转换

优

逻辑时序简单,电路易实现

缺

①信号线多,占空间多

②远距离传输贵

③工作频率较高时,并行的线会互相干扰

注

①工作频率一样时,速度并>串

②由于并的工作频率不能太高,故串的速度可>并

2️⃣按总线功能

1. 片内总线

cpu内部,寄存器与寄存器、寄存器与ALU之间的线

2. 系统总线

计系内各部件(CPU、主存、I/O接口)之间互连的线按系统总线的传输信息

1)数据总线DB

①传各部件之间的信息=指令、操作数

②双向

③位数与机器字长、存储字长有关

2)地址总线AB

①指出数据总线上的数据所在地址

②单向(cpu 发出)

③位数与主存地址空间的大小有关

3)控制总线CB

①一根控制线,传一个信号

②双向(cpu 发出、主存和外设发给 cpu)

3. 通信总线(外部总线)

计系与计系

3️⃣按时序控制方式

同步、异步

3,系统总线——结构

1️⃣单总线结构

结构:CPU、主存、I/O设备,连在一组总线上,允许它们直接交换信息

优

①结构简单

②成本低

③易于接入新设备

缺

①带宽低、负载重

②多个部件争唯一的总线

③不支持并行传送

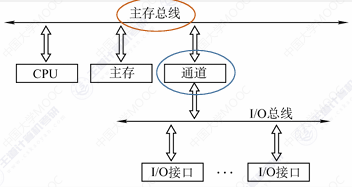

2️⃣双总线结构

结构:一条主存总线,CPU、主存、通道;一条I/O总线,外设与通道

主存总线,支持突发(猝发)传送:送出一个地址,收到多个地址连续的数据

通道=小cpu,管理I/O设备,通道程序放在主存

优

将较低速的I/O设备,从单总线上分离出来,实现存储器总线和I/O总线分离。

缺

需通道等硬件设备

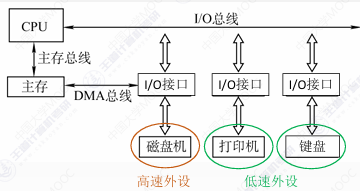

3️⃣三总线结构

结构:主存总线、I/O总线、直接内存访问DMA总线

优

①↑ I/O 设备的性能,更快响应命令

②↑ 吞吐量

缺

效率低,因为三线同时只能工作一个

磁带的读写单位=块

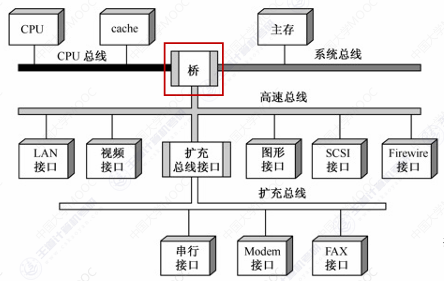

4️⃣四总线结构

①桥接器:连不同的总线,数据缓冲、转换、控制

②越靠近 CPU,速度越快

③每级都遵循总线标准

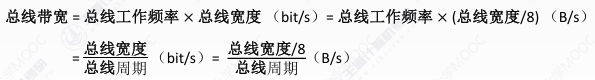

4,总线的性能指标

1. 总线的传输周期(总线周期)

一次总线操作所需的时间

(包括申请、寻址、传输、结束阶段),由多个总线时钟周期构成

2. 总线时钟周期

即机器的时钟周期(有些计算机,可能由桥接器提供)

总线周期与总线时钟周期的关系,很乱

3. 总线的工作频率

总线上各种操作的频率,=1/总线周期

若总线周期=n个时钟周期,则总线的工作频率=时钟频率/n,指一秒内传送几次数据

4. 总线的时钟频率

即机器的时钟频率,=1/时钟周期

若时钟周期为t,则时钟频率=1/t,指一秒内有多少个时钟周期

5. 总线宽度(总线位宽)

是总线上同时能够传输的数据位数(一般是指数据总线的根数)

6. 总线带宽

是总线的数据传输率,即单位时间内,总线上可传输数据的位数

用每秒钟传的字节数来衡量,单位=字节/秒(B/s)

注

总线带宽,是max传输速率

有效数据传输率=实际传输的数据量/耗时

7. 总线复用

指一种信号线,在不同的时间,传不同的信息。用较少的线传更多的信息,省空间、成本

8. 信号线数

地址、数据、控制总线,3种总线数的总和

6.2、总线事物和定时

0,总线仲裁

408大纲已删

1,总线周期——阶段

1)申请分配

需要使用总线的主模块/主设备A,提出申请,经总线仲裁机构决定,将下一传输周期的总线使用权,授予A(可细分为传输请求、总线仲裁)

2)寻址

A通过总线,发出访问从模块的地址B、相关命令,启动B

3)传输

A和B数据交换,可单向或双向

4)结束

A的信息,从系统总线上撤除,让出总线使用权

2,总线定时

总线定时——定义

指总线在双方交换数据的过程中,需要时间上配合关系的控制(实质是一种协议或规则)

总线定时——方案

①同步通信(同步定时方式)

系统统一规定

优,速度快、逻辑简单

缺,主从设备强制性同步、不能及时检验通信、可靠性差

适于,总线长度短、总线所接部件的存取时间差不多

②异步通信(异步定时方式)

主从设备商讨(为方便记忆,主A,从B)

优,总线T长度可变,速度相差大的设备,能可靠交换信息

缺,比同步复杂、速度比同步慢

1)不互锁方式(速度最快、最不可靠)

A,发出请求a,a过一会自动删

B,收到a后,发出回答b,b过一会自动删

2)半互锁方式

A,发出请求a,必须收到b,a才删

B,收到a后,发出回答b,b过一会自动删

3)全互锁方式(速度最慢、最可靠)

A,发出请求a,必须收到b,a才删

B,收到a后,发出回答b,必须等到a删后,b过才删

③半同步通信

统一时钟的基础上,加一个等待响应信号

④分离式通信

原理

①A 发地址、命令

②B 准备数据 ——>这时候不占总线,把这个时间让给别人

③B 向 A 发数据

特点

①各模块,均有权申请占用总线

②同步方式通信,不等对方回答

③各模块,准备数据时,不占总线

④总线利用率↑

6.3、总线标准

408大纲已删

七、输入输出系统

7.1、IO系统

1,概述

I/O 设备(可统称为外设)

可实现data,从I/O 设备——>计,或计——>I/O 设备的外设

常见的I/O设备

①输入设备,鼠标、键盘

②输出设备,显示器、打印机

③可输入、又可输出的设备(外存),硬盘、光盘

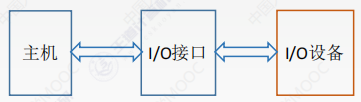

I/O接口(又称I/O控制、I/O Controller、设备控制器)

(是一块芯片,常被集成在主板上,或者集成在南桥芯片内部)

协调主机与外设之间的数据传输

I/O系统——组成

(1)I/O 硬件(包括外设、I/O接口 、I/O总线)

(2)I/O 软件(包括驱动程序、用户程序、管理程序、升级补丁)

用I/O指令和通道指令,实现主机<—>I/O设备的信息交换

①I/O 指令(cpu执行)

操作码,识别是不是IO指令

命令码,对IO设备干什么

设备码,哪个IO设备

②通道指令(通道执行)

通道程序提前编好放在主存

2,IO控制方式

I/O控制——方式

(1)程序查询方式

cpu检查psw

若IO=已完成,再从data寄存器取输入data

若IO=未完成,一直等,不能做其他事

(2)程序中断方式

等IO时,cpu可做其他事

若IO完成后,IO控制器——>cpu发中断请求,cpu响应中断请求,然后取输入data

(3)DMA控制方式

主存与高速I/O设备之间,有一条直接数据通路(DMA总线)

(4)通道控制方式

通道是具有特殊功能的处理器(弱鸡版cpu),对I/O设备统一管理

3,外设

8万+

8万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?