学习verilog一些基本知识,有两个概念:

1.模块调用;2.模块实例化

想知道他俩有什么区别,也有说就是同一个东西的,有木有大神告诉告诉我

查到比较有用的内容如下:

Verilog是一种硬件描述语言,用于描述数字电路和系统。在Verilog中,模块是基本的构造单元,可以通过实例化来使用。模块的调用方式主要有三种:直接实例化、使用模块名和端口映射

1. 直接实例化:

直接实例化是指在模块的声明部分直接使用模块名和参数来创建模块的实例

2. 使用模块名:

另一种方式是使用模块名来调用模块,这种方式不需要在声明部分创建实例,而是在需要使用模块的地方直接使用模块名

3. 端口映射:

第三种方式是使用端口映射来调用模块。这种方式需要在声明部分创建实例,并指定端口连接关系。这种方式可以方便地修改端口连接关系,同时也可以避免因端口连接错误而导致的问题

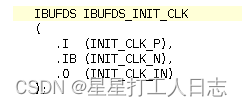

我看的代码中使用的应该是第二种:调用模块

但是这样看来模块调用就是模块实例化3种方式中的一种?是这样吗

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?