1、数字系统:对数字信号进行加工、传递和存储的实体。

2、数字信号:在时间上和数字上都不连续变化的信号。

3、模拟信号:在时间上和数字上都是均匀变化的信号。

记:加工、传递、存储 || 模拟变化丝滑、数字变化生硬

4、数制的变换:主要是16转2进制:一位变成四位,可以忽略的零忽略掉

如:(6D.4)进制16 = 01101101.0100 = 1101101.01

5、BCD码:使用四位二进制码表示一位十进制数码。

6、根据码中的每一位是否有权来区分有权码与无权码。

7、BCD码是以二进制的形式呈现,但实际上是十进制

8、有权BCD码:每一位都有权值,例如:8421码、5421码、2421码。

9、8421码与十进制码的转换:因为8421码的表现是二进制码,所以这里与二进制十进制的转换大体相同,只是需要注意,在十进制码转换为8421码时,直接4位并1,不能删掉多余的0。

10、5421码、2421码与8421码类似,8421码是模拟2进制码本来的权值规则,5421与2421则是有所改变。

例:5421码:1111=1×5+1×4+1×2+1×1.

11、无权BCD码:每位数码没有确定的位权,如余三码。

12、余三码是在8421码的基础上加上0011,余三码是对9的自补码。

13、自补码是什么?

例:2转换成8421码是0010,转化为余三码需要加上0011,=0101 || 然后,0101按位取反,得1010,正好是7的余三码,2+7=9,这叫做对9的补码。

14、奇偶校验码:具有检错能力的代码

组成:校验位(1位)+信息位。

编写方式:奇校验码:信息位中1的个数为奇数

偶校验码:信息位中0的个数为奇数

特点:编码简单,编码电路与检测电路简单

缺点:只能发现单错,不能发现双错。

15、为什么奇偶校验码只能发现单错,不能发现双错呢?

在只发生1位码的错误时,我们可以通过奇偶位数的改变调整校验位,从而让验收方发现有这个错误,但是如果有两位错误,那么无论发生错误的两位上是什么,最后的奇偶位数都不会发生改变。

16、与门、或门、非门、与非门、或非门、异或门、同或门 都自行查书再看一遍怎么画的。

17、利用余三码进行加法运算时,如果有进位,结果加三,如果没有进位,结果减三。

这里写了半天,还是没有搞懂一位数余三码加法的规则,但是我明白了二位数余三码的加法规则,一位数也可以通用:

6+7=13 ,06 +07 = (0011 1001)+(0011 1010)=(0100 0110),其中在第一个四位相加中存在进位即1010+0110有进位,所以,结果中的0110加0011,0100-0011 => (0100 0110)正好是13的余三码

18、无权BCD码不能直接进行算术运算

19、任意两位有符号的十进制需要8位二进制数

任意两位无符号的十进制需要7位二进制数

20、逻辑函数的定律其实只需要关注反演律,其他的只需要将“或”换成“+”,“且”换成“×”。

21、对偶规则:将式子中,或变成非,非变成或,0变成1,1变成0,注意常量不变

例:A(B+C) => A+BC

注意:运算的优先顺序不变,长非号不变

22、常用的公式有吸收律和包含律,自己翻书看看,或者百度

23、异或(同或)逻辑运算公式:当异或的个数为偶数,变成同或时要整体取反。

为偶数时,则不需要取反。

24、最小项与最大项:最小项的原变量是1,m,最大项的原变量是0,M 。

25、标准与或式:要求标准与或式就是求最小项

26、4位二进制奇检验位需要4个两输入异或门

4位二进制偶检验位需要3个两输入异或门

27、组合逻辑电路的分析方法:1、根据逻辑电路图,写出输出函数表达式

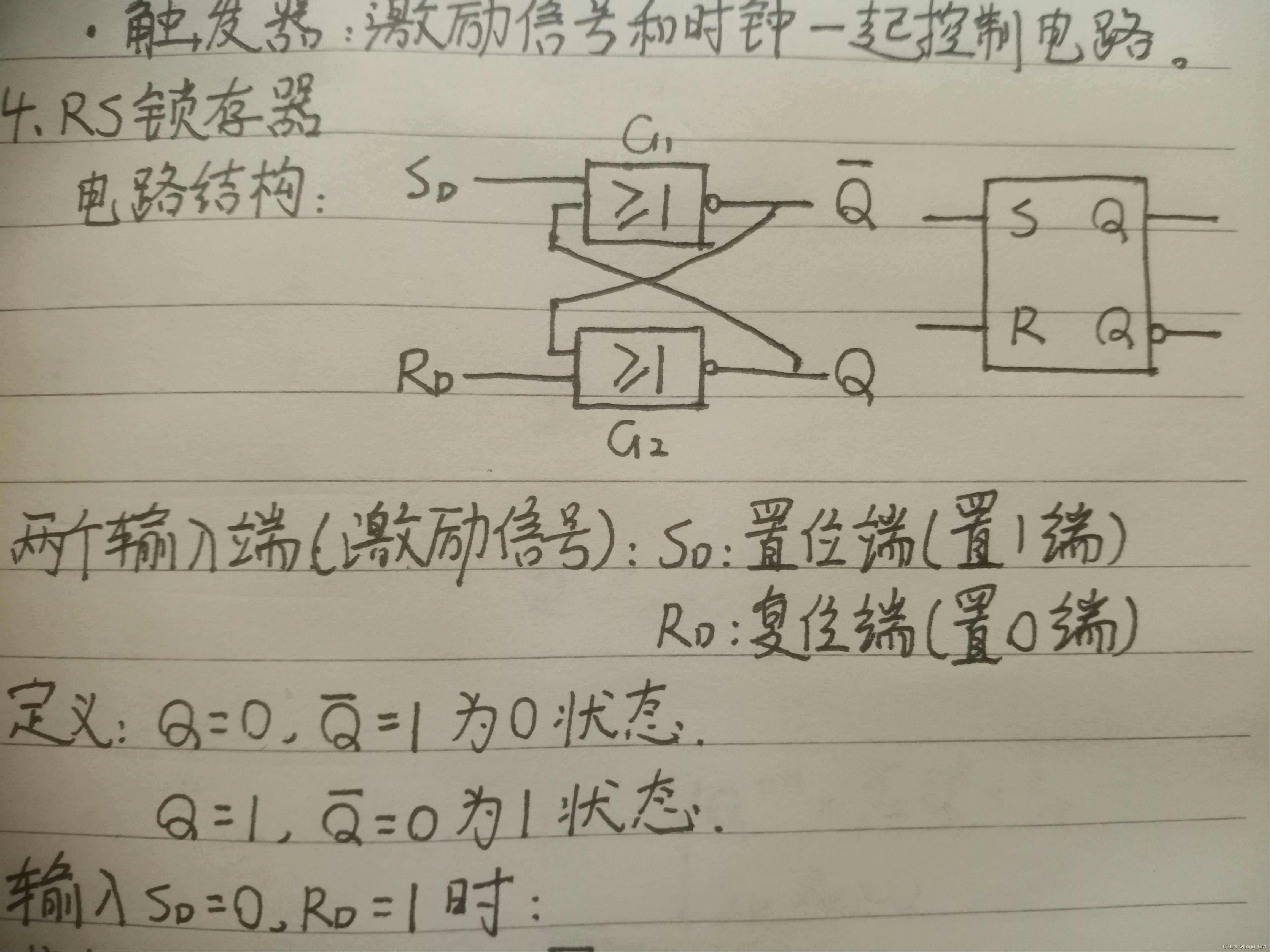

2、列出真值表,分析电路功能

28、半加器:S是A、B相加的和,C是产生的进位

29、全加器:输入端有C,继承了上一个全加器的进位。

30、竞争现象:输入信号经过不同路径到达输出端的时间有先有后,称为竞争现象

31、冒险现象:由于竞争导致的错误输出信号

32、编码器:将信息转换成符合一定规则的二进制代码。

33、二进制编码器:用n位二进制代码,对2的n次方个特定信息进行编码的逻辑电路

34、二-十进制编码器:用BCD码对十个输入信号进行编码,输出BCD码,也称为10线-4线编码器

35、译码器:二进制代码=>信息

信息时多的一方,编码是简化了存储形式

36、74138译码器是带使能端的3-8译码器。

37、数据选择器:从多路数据输入中选择其中一条路到输出端

38、串行进位加法器:由全加器构成的加法器

特点:结构简单,运算速度慢

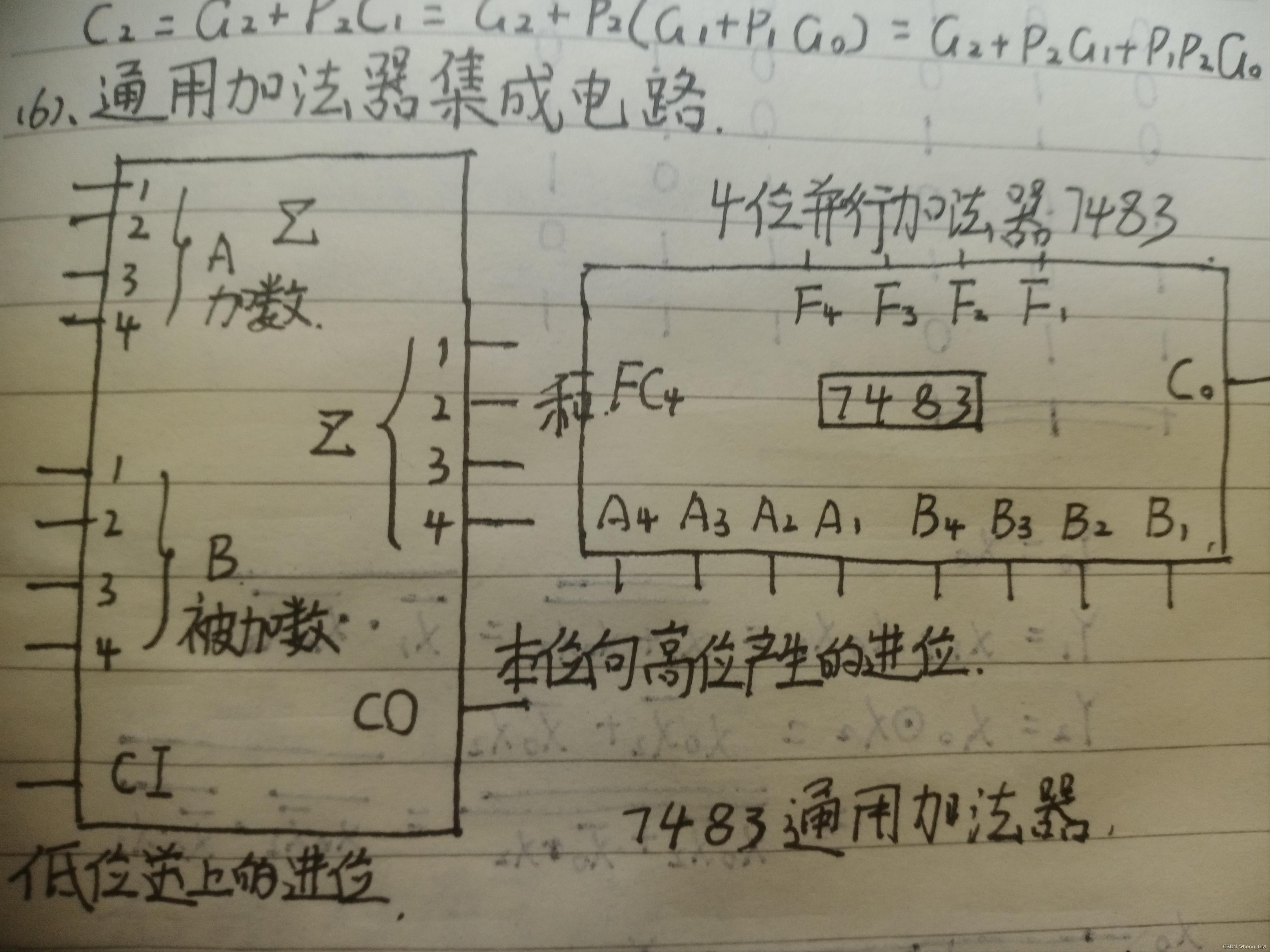

39、全并行加法器:速度最快、结果复杂

40、超前进位加法器:由两个加数,首先求得各位的进位

41、电路在任何时刻的输出稳定值,不仅与该时刻的输入信号有关,而且与该时刻以前的电路状态有关。

42、对于时序逻辑电路,我们需要关注四个点:输出方程、驱动方程、状态方程、状态图

43、存储单元电路:存储一位二进制信号的器件,存储单元大多是双稳态电路。

44、两类存储单元电路:锁存器、触发器

45、RS锁存器:以输出Q的值来确定状态,Q为1,就为1状态,Q为0,就为0状态。

RS锁存器,是以S的值来确定发挥出什么功能的:

S=1,R=0,置1功能;

S=0,R=1,置0功能;

S=0,R=0,保持功能;

S=1,R=1,禁止;

46、门控RS锁存器:在RS的基础上,加上控制信号,控制锁存器状态转换的时间:

当C=1时,可以影响状态;

当C=0时,不能影响状态;

47、门控JK锁存器,在门控RS的基础上,C=0时,SR=0恒成立。

48、门控D锁存器中,当C=1时,锁存器状态会随着信号D变化而变化,若D变化剧烈,会发生空翻现象。

49、触发器:激励信号和时钟一起控制状态

时钟脉冲确定状态转换的时刻,由输入信号确定状态转换的方向

缺点:当CLK即时钟为1时,如果信号发生剧烈的变化,也会有发生空翻的可能

50、边沿触发器:在时钟稳定时,输入信号无法进入触发器,触发器的状态不发生改变

51、按照电路的工作方式,时序逻辑电路可以分为:同步时序电路和异步时序电路。

按照逻辑功能可以分为:计数器、寄存器、移位寄存器。

52、仅由逻辑门构成的电路是组合逻辑电路。

53、异步时序逻辑电路中各触发器状态变化不是发生在同一时刻,但必须要有时钟脉冲

54、时序逻辑电路的分析步骤是:

1、写出输出方程与驱动方程

2、将驱动方程带入特性方程,导出状态方程

3、画出状态表

这里具体看我另外一篇关于数字逻辑的文章

本文深入探讨了数字系统的基础概念,包括数字信号与模拟信号的区别、数制转换、BCD码(8421码、5421码与无权码)的应用,以及奇偶校验码的作用。重点讲解了加法运算中的余三码和不同类型的逻辑门。还介绍了编码器、译码器和时序逻辑电路的关键要素,如同步与异步、触发器和状态机。

本文深入探讨了数字系统的基础概念,包括数字信号与模拟信号的区别、数制转换、BCD码(8421码、5421码与无权码)的应用,以及奇偶校验码的作用。重点讲解了加法运算中的余三码和不同类型的逻辑门。还介绍了编码器、译码器和时序逻辑电路的关键要素,如同步与异步、触发器和状态机。

620

620

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?