1.FPGA由哪些资源组成?

LABs(逻辑阵列块):有多个逻辑单元(LEs)组成,每个逻辑单元由一个查找表(LUT)和一个触发器组成。EP4CE6F17C8逻辑阵列块有16个LE。

IOB(可编程逻辑IO口):有输入(in)、输出(out)、输入输出(in_out)三种。(可编程体现在它可以调节电阻来适配不同的电压)

时钟资源:锁相环(PLL)——(1、使输出时钟走全局时钟网络;2、分频,倍频,相位偏移、调整占空比)。

嵌入式存储块——M9K。

嵌入式乘法模块:DSP——高性能乘法、除法、累加运算。

FPGA的基本构成方式:可编程输入输出块(IOB)、可编程逻辑单元(CLB)和可编程内部互连线(PIA)。

补充:丰富的布线资源。

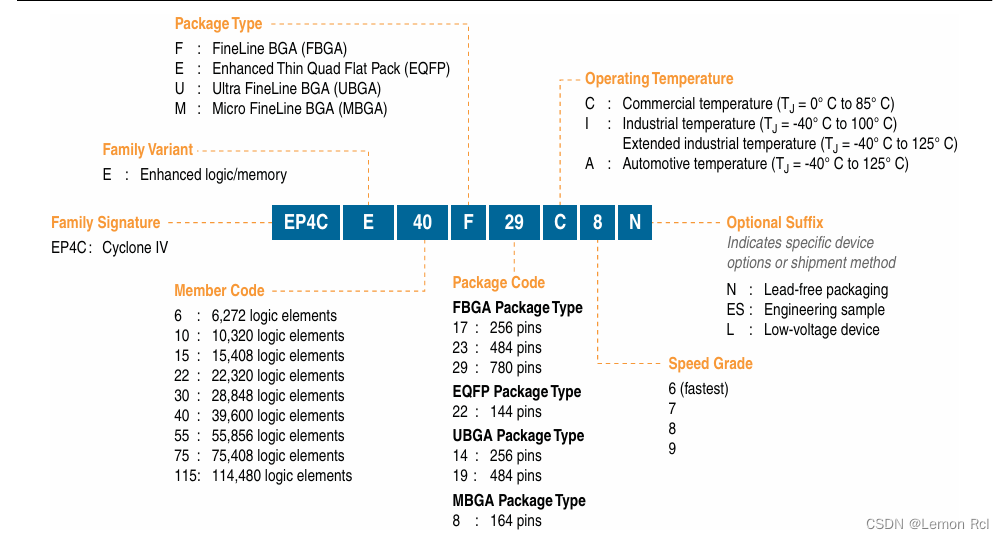

EP4CE6F17C8这款FPGA的各部分含义如下:

- EP4C:Cyclone IV系列

- E :Cyclone IV E系列

- 6:6267个逻辑单元,

- F:FineLine BGA封装

- 17:256个引脚

- C:商用温度范围(0°C到85°C)

- 8:速度等级(数值越大,速度越慢)

2. 用VHDL/Verilog HDL语言开发可编程逻辑电路的完整流程?

2. 用VHDL/Verilog HDL语言开发可编程逻辑电路的完整流程?

一般设计流程可以大致归纳为:设计文件输入、功能仿真、逻辑综合、 布局布线、时序仿真、硬件测试。

1) 设计文件输入:使用HDL语言、调用IP核或者网表文件等方式进行源文件 设计;

2) 功能仿真:在测试文件中产生测试向量对设计进行功能仿真,或者说叫行为 防止,以验证设计的逻辑功能是否满足需求;

3) 逻辑综合:根据设计功能和实现该设计的约束条件(如面积、速度、功耗和 成本等),将设计输入转换成满足要求的电路设计方案,该方案必须同时满 足其功能和约束条件。综合的过程也是设计优化目标的过程,其目的是将多 个模块设计文件合并为一个网表文件,供布局布线使用,网表文件中包含了 目标器件中的逻辑单元和互连的信息;

4) 布局布线:根据设计者指定的约束(SDC文件)条件(如面积、延时、时钟 频率等)、目标器件的结构资源和工艺特性,以最优的方式对逻辑元件布局, 并准确地实现元件间的互连,完成网表文件到实际目标器件的转换;

5) 时序仿真:在布局布线完成后,EDA工具会提供一个时序仿真模型,其中包 括了器件的一些延时参数,如门电路延时、走线延时等,通过时序仿真可以 英特尔FPGA中国创新中心 检查在特定的时钟频率下设计是否正常能工作,也就说可以检查出设计中存 在的时序违例的路径;但是通常我们会使用静态时序分析(STA)的方式来 代替时序仿真,因此一般可以省略这一步;

6) 硬件测试:使用工具生成的bit流文件对FPGA芯片进行配置,测试运行结 果;既可以使用专用的逻辑分析仪通过FPGA的IO口对内部信号进行抓取, 也可以使用EDA工具内嵌的在线逻辑分析工具(如Signaltap、ILA等)进行 在线调试。

3.Quartus 编译器编译FPGA⼯程最终产生哪两种不同用途的文件?

分别为.sof和.pof⽂件。

sof 为 SRAMObject File,下载到FPGA中,断电丢失;

pof 为Programming Object File,下载到配置芯⽚中,上电重新配置FPGA。

4. 功能仿真与时序仿真的区别?

功能仿真是在设计输入完成之后,选择具体器件进行综合、适配之前 进行的逻辑功能验证,因此又称为前仿真/行为仿真。仿真过程不涉及任何具体 器件的硬件特性,此时的仿真没有延时信息或者有由系统添加的微小标准延时, 这对于初步的功能检测非常方便(主要检查代码中是否有逻辑错误)。

时序仿真是在选择了具体器件并完成布局、布线之后进行的时序关系仿真, 因此又称为后仿真或延时仿真。仿真文件包含了器件的硬件特性参数,对系统和 各模块进行时序仿真,可分析其时序关系,估计设计的性能以及检查和消除竞争 冒险等。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?