学习日记

引用“特权同学”在其书中的文字,以激励自己:

理论很重要,实践更重要;理论与实践结合过程中更是需要多思考、多分析、多总结。

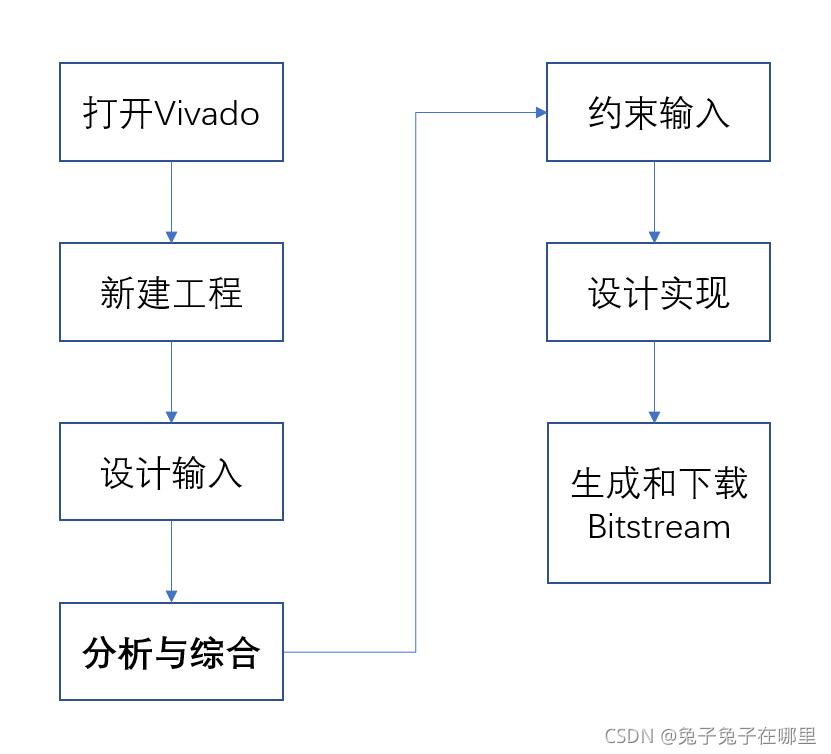

一个完整的项目大致应经过以下几步:

分析与综合:综合(synthesis)将RTL设计转变为由FPGA器件中的查找表LUT、触发器FF等各种由底层电路单元组成的网表;在此过程中,综合器会对设计进行优化

约束输入:需要较多的经验累积,表达了设计者期望满足的时序需求

led_flash项目过程:

这里使用的板子是Z7-Lite7010

新建工程完成后…

step1:设计Verilog项目-led_flash.v

module led_flash2(

input wire clk,

input wire rst_n,

output reg [1:0] led

);

//============================

//inter

本文是作者的FPGA学习日记,详细记录了从新建工程到完成led_flash项目的步骤,包括Verilog代码编写、综合分析、管脚约束等。在项目中遇到Vivado版本不匹配导致的管脚约束问题和下载验证时的"Not Programmed"错误,通过查阅资料和修改代码,最终成功解决问题。这是一个FPGA新手的成长历程,适合入门者参考。

本文是作者的FPGA学习日记,详细记录了从新建工程到完成led_flash项目的步骤,包括Verilog代码编写、综合分析、管脚约束等。在项目中遇到Vivado版本不匹配导致的管脚约束问题和下载验证时的"Not Programmed"错误,通过查阅资料和修改代码,最终成功解决问题。这是一个FPGA新手的成长历程,适合入门者参考。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?