1. 首先看看在时钟驱动下的非阻塞赋值和阻塞赋值

非阻塞赋值:

module TEST(

input clk,

input wire [3:0] a,

output reg [3:0] b

);

reg [3:0] c;

always @(posedge clk)

begin

c<=a+2;

b<=c+4;

end

endmodule

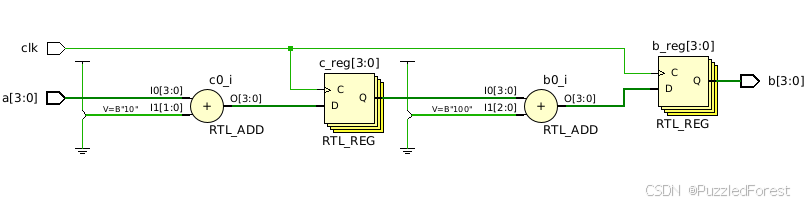

由电路图可以看出是标准的时序电路

阻塞赋值:

module TEST(

input clk,

input wire [3:0] a,

output reg [3:0] b

);

reg [3:0] c;

always @(posedge clk)

begin

c=a+2;

b=c+4;

end

endmodule

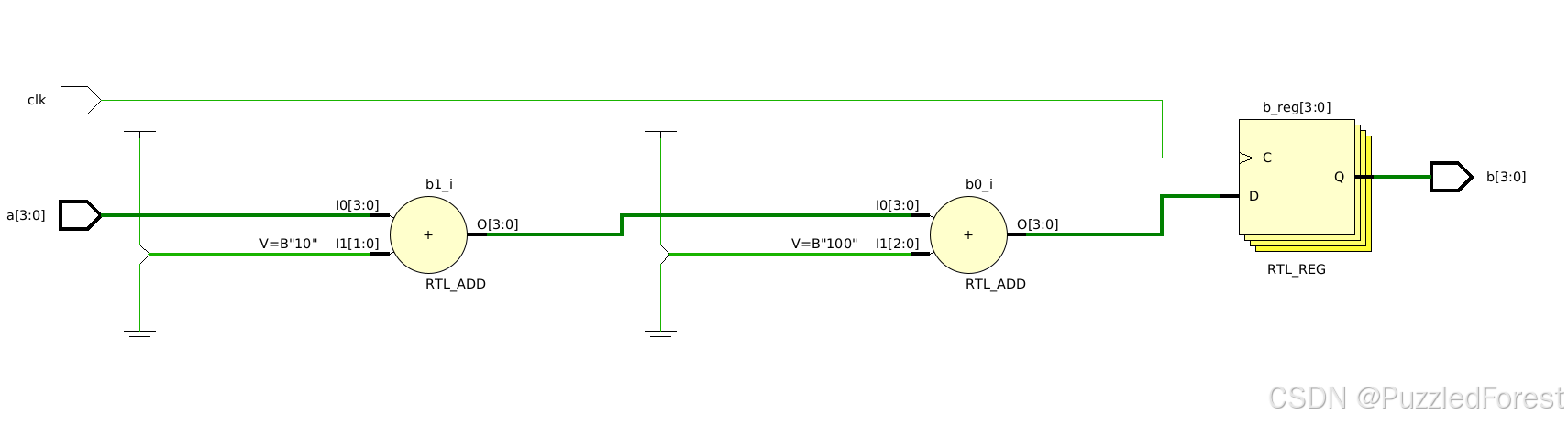

只有最后的输出b被综合成了触发器,前面的都是组合逻辑电路,符合阻塞赋值 “ 顺序执行语句 ” 的含义

2. 再来看看电平敏感下的非阻塞赋值和阻塞赋值

非阻塞赋值

module TEST(

input clk,

input wire [3:0] a,

output reg [3:0] b

);

reg [3:0] c;

always @(*)

begin

c<=a+2;

b<=c+4;

end

endmodule

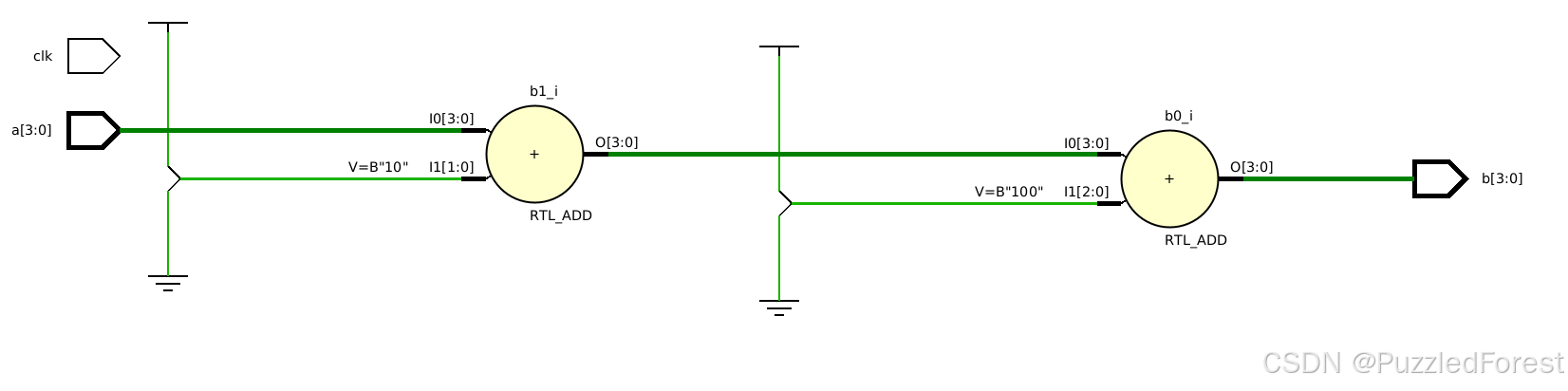

综合成了纯组合逻辑电路

阻塞赋值

module TEST(

input clk,

input wire [3:0] a,

output reg [3:0] b

);

reg [3:0] c;

always @(*)

begin

c=a+2;

b=c+4;

end

endmodule

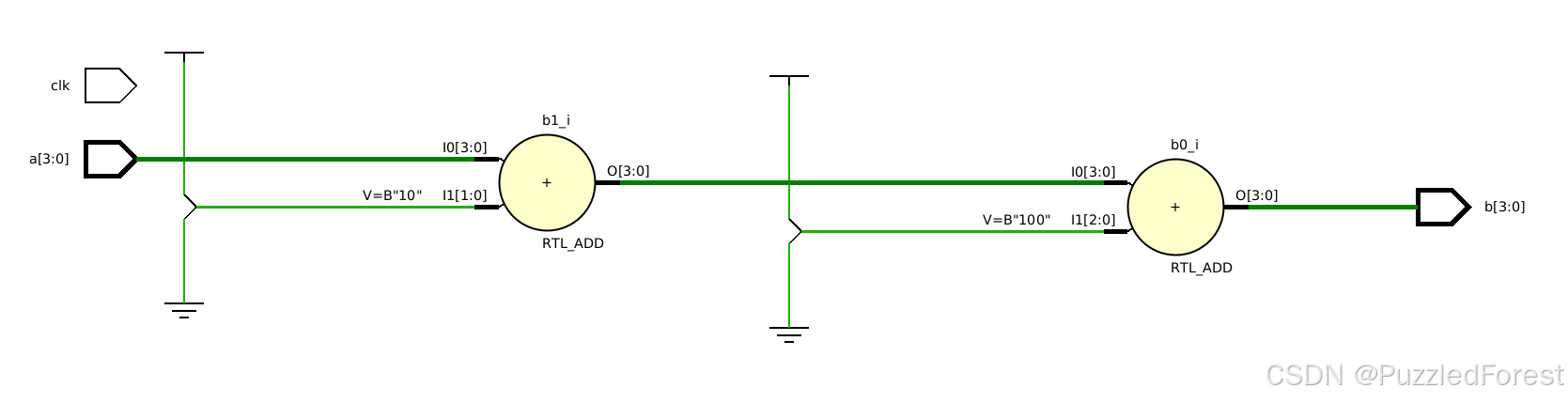

也综合成了纯组合逻辑电路

电平敏感时,全部综合成组合逻辑电路

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?