对于 DDR3 SDRAM 控制器 IP 核,app 端的命令总线是读写复用的,因此可能会存在读写冲突的时刻,为了解决掉这种问题,我们将会控制 app 命令端分时的给读,或者写使用,也就是我们所说的仲裁,具体是完成读还是完成写,我们交由仲裁来决定。

读、写仲裁控制模块实现

在我们实现了 DDR3 控制器 IP 核的读、写之后会发现读和写是共用一组命令线的,因此读、写需要分时的使用 IP 核中的命令总线,具体的解决方法如图 6 所示。

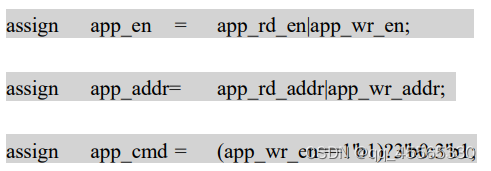

如上图 6 所示,我们可以对分时的将 A7_wr_ctrl 和 A7_rd_ctrl 模块的 app_cmd 信号传输给 IP 核的 app_cmd 信号。对于 A7_wr_ctrl 和 A7_rd_ctrl 模块的 app_addr 信号,我们可以在不使用时将其置为 0,这样我们将 A7_wr_ctrl 和 A7_rd_ctrl 模块的 app_addr 进行按位或,结果即为 IP 核的 app_addr。同理,IP 核的 app_en 也 可以通过 A7_wr_ctrl 和 A7_rd_ctrl 模块的 app_en 按位或得到。具体的示例代码如下所示。

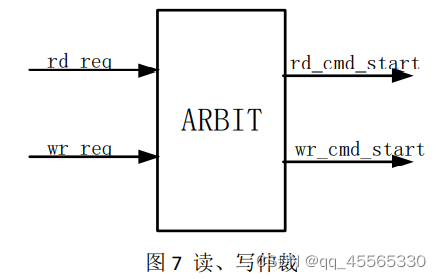

如上所述,我们完成了读、写模块与IP核的交互,但是假如读、写的启动信号同时产生,将会造成 app_addr 和 app_en 同时有效,上述的按位或的方式将会失效,因此我们不能让读、写启动信号同时产生,为了解决这个问题,我们可以 加一个仲裁器来控制产生读、写的启动信号,具体框图如 7 所示。

为了完成上图所示的仲裁器,我们可以设定一个状态机,具体如图 8 所示。 当复位结束后,可以直接进入到仲裁状态(ARBIT),在 ARBIT状态等待读、写请求,当某一个请求到来,即进入到对应的状态执行相应的操作,执行完回到 ARBIT 状态等待下一次的请求,并且只有在 ARBIT 状态时读、写的请求才会有效,这样就可

本文详细介绍了DDR3 SDRAM控制器中如何解决读写冲突问题,通过设计一个仲裁模块来确保读写操作分时使用命令总线。仲裁器采用状态机实现,避免了读写启动信号同时产生的冲突,确保了读写操作的正确进行。

本文详细介绍了DDR3 SDRAM控制器中如何解决读写冲突问题,通过设计一个仲裁模块来确保读写操作分时使用命令总线。仲裁器采用状态机实现,避免了读写启动信号同时产生的冲突,确保了读写操作的正确进行。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

4063

4063

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?