一、概念

在实际电路中,必须考虑传输延迟的影响。比如D锁存器,在时钟信号从1变成0时,它把当前输出的值储存在锁存器中。如果输入D稳定,则电路可以稳定工作,如果在时钟跳变时候D的内容也正好发生变化,则可能产生不可预知的结果。所以电路设计者必须保证时钟信号跳变时后,输入信号是稳定的。

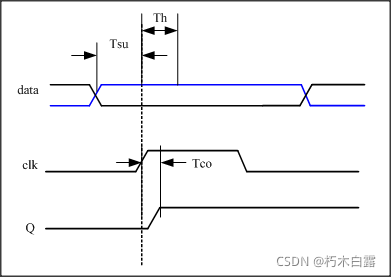

下图中标示了一些关键时间区间,这些区间和工艺有关。集成电路制造厂家都会提供这个参数。

建立时间(Tsu:set up time):是指在触发器的时钟信号上升沿到来以前,数据稳定不变的时间,如果建立时间不够,数据将不能在这个时钟上升沿被稳定的打入触发器,Tsu就是指这个最小的稳定时间。

保持时间(Th:hold time):是指在触发器的时钟信号上升沿到来以后,数据稳定不变的时间,如果保持时间不够,数据同样不能被稳定的打入触发器,Th就是指这个最小的保持时间。

如果电路中使用的触发器没有没有遵循建立和保持要求,则电路会进入“亚稳态”的不稳定状态。

输出响应时间(Tco或者TcQ)

触发器输出的响应时间,也就是触发器的输出在clk时钟上升沿到来之后多长的时间内发生变化,也即触发器的输出延时。一般的,Q值从1到0和从0到1的延时并不完全一样,但为了简化,通常假定他们是相等的。对于商业芯片,通常会给出两个Tco/TcQ的值,分别代表实际上可能产生的最大延时和最小延时。指定一个范围是评估一个芯片延时的常见做法,因为芯片制造过程中存在许多延迟变化的来源。

转自:https://blog.youkuaiyun.com/v13910/article/details/95245170

二、为什么会有建立时间和保持时间

何为建立时间(Setup Time)和保持时间(HoldTime)?以D触发器为例,在作为接收端时;由于工艺、寄生参数、触发器结构等原因决定,被采样数据必需有一个稳定区 间,保证数据可以正确的被触发器采样。通常我们把这个要求的稳定区间称为 Setup-Hold window。我们把 Setup-Hold window 和时钟沿对应起来,把Setup-Hold window 分解为两部分,建立时间(Setup Time)和保持时间(Hold Time)。

https://www.cnblogs.com/chip/p/5203790.html

本文介绍了FPGA设计中的建立时间(Tsu)和保持时间(Th)概念,强调了它们在保证电路稳定工作中的重要性。通过时序分析,探讨了建立时间裕量和保持时间裕量的计算,同时讲解了时钟偏移(Skew)、时钟抖动(Jitter)和亚稳态。文章还提供了Vivado时序约束的详细指导,包括输入、输出延迟、寄存器到寄存器的路径约束等。

本文介绍了FPGA设计中的建立时间(Tsu)和保持时间(Th)概念,强调了它们在保证电路稳定工作中的重要性。通过时序分析,探讨了建立时间裕量和保持时间裕量的计算,同时讲解了时钟偏移(Skew)、时钟抖动(Jitter)和亚稳态。文章还提供了Vivado时序约束的详细指导,包括输入、输出延迟、寄存器到寄存器的路径约束等。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?