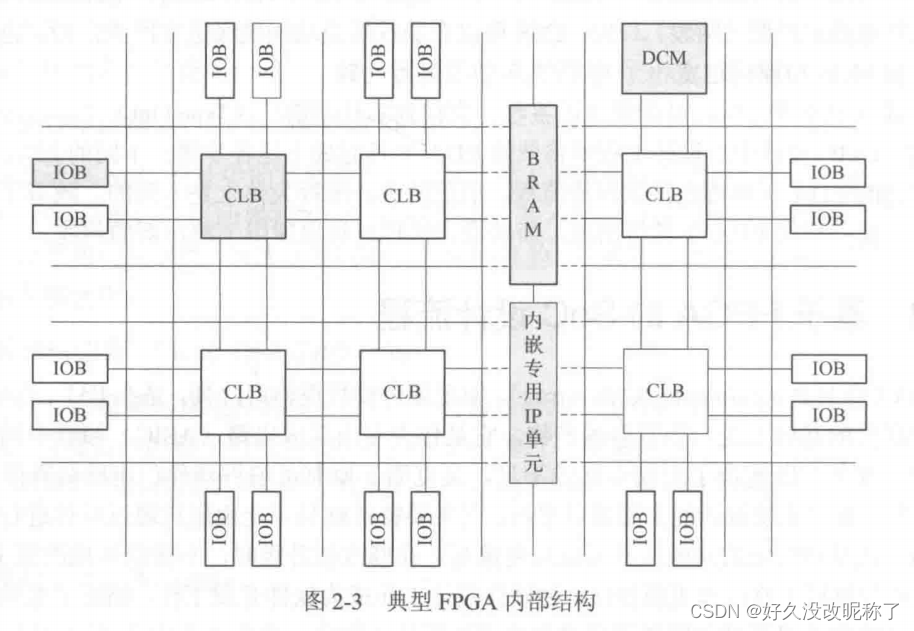

【FPGA的结构】

一般包括:

(1)可编程逻辑块(CLB)

(2)可编程输入/输出单元(IOB)

(3)时钟管理模块(DCM)

(4)嵌入式块RAM(BRAM)

(5)内嵌专用IP单元

(1)可编程逻辑块

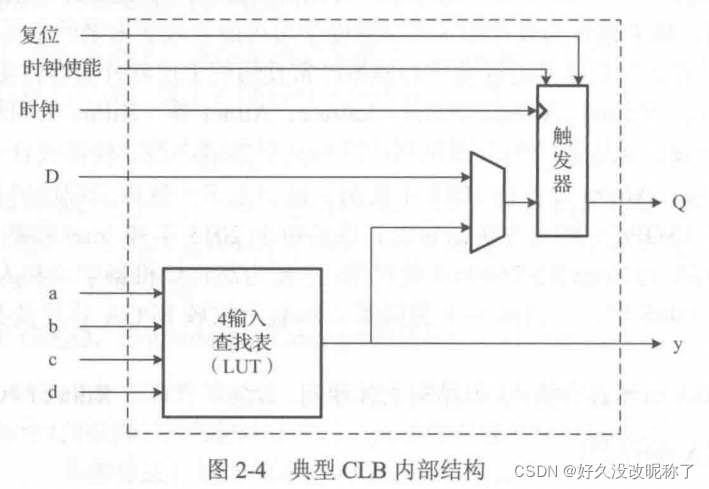

CLB是FPGA内部的基本逻辑单元,其数量和特性会依据器件的不同而不同。大体上每个CLB由若干查找表及附加逻辑(如多路选择器、触发器、进位逻辑、算术逻辑等)组成,可用于实现组合逻辑和时序逻辑,还可以被配置为分布式RAM和分布式ROM。图2-4-给出了一个典型CLB的结构,包含一个4输入LUT、一个多路选择器和一个触发器。其中,触发器可以被配置(编程)为寄存器或锁存器,多路选择器可以被配置为选择一个到逻辑块的输入或LUT的输出,LUT则可以被配置以实现任何的逻辑功能。

FPGA采用查找表LUT实现基本的电路逻辑功能,目前大部分FPGA采用SRAM工艺实现查找表,一个4输入的查找表如图2-5所示。A、B、C、D由FPGA芯片的引脚输入或内部新信号给出,然后

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?