在FPGA内部的时序路径主要有4大类型,通常所说的FPGA的时序约束的对象也都在这四大类型当中,所以要进行确定时序约束首先心中要有这四大类型的时序路径的概念,清楚约束的路径对象属于哪个类型当中,在进行时序分析和时序约束操作。

一、FPGA内部时序路径类型介绍

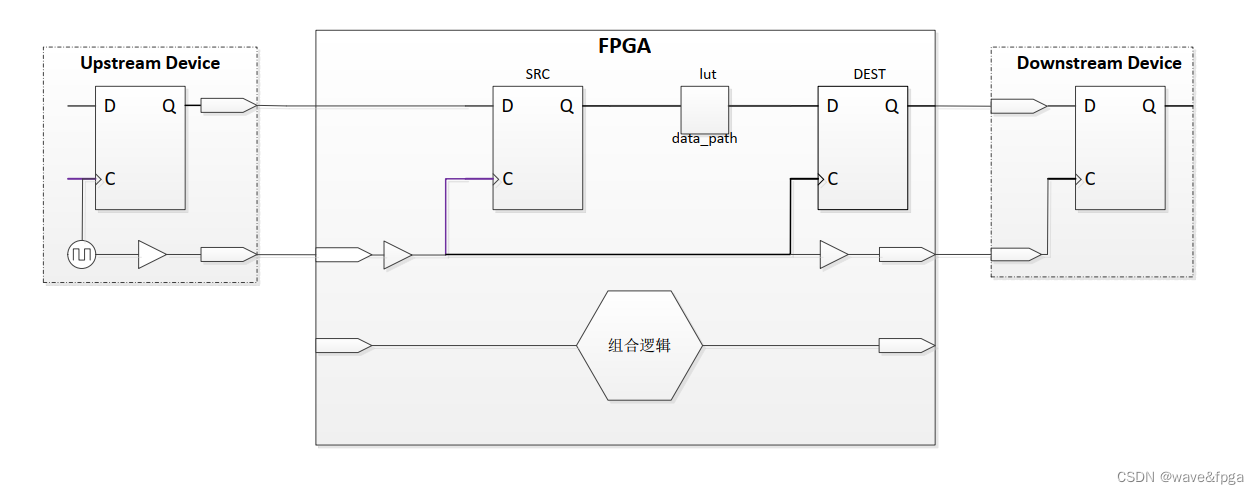

FPGA内部时序路径的四大类型主要包括:寄存器到寄存器路径、外部引脚输入到内部寄存器路径、内部寄存器到外部输出引脚路径、内部引脚输入到外部引脚输出路径。如下图所示:

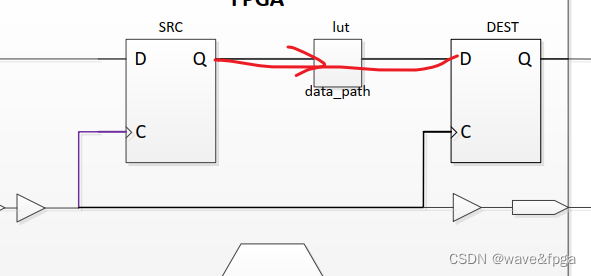

1、寄存器到寄存器类型路径

寄存器到寄存器路径可以简称reg2reg,从第一级寄存器的输出到下一级寄存器的输入,路径。图中SRC寄存器我们一般称为源寄存器,DEST寄存器一般称为目的寄存器,data_path是组合逻辑,在该路径中信号的传输需要一定的延时,分析该路径的原因是因为要确保在时钟在时钟的发送沿信号要从源寄存器发出,在时钟的锁存沿能够确保目的寄存器正确寄存该信号,如下图所示。

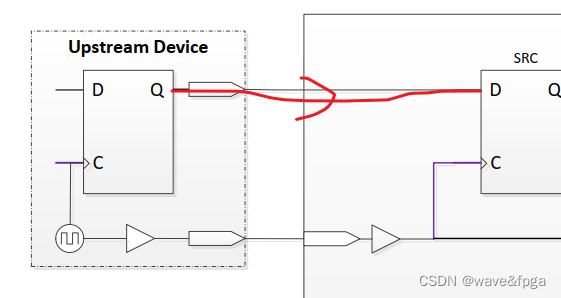

2、引脚输入到内部寄存器路径

引脚输入到内部寄存器路径可以简称为input2reg,外部引脚输入的信号一般来自于外部器件的信号输出。这时候外部器件可以理解为源寄存器,FPGA内部的寄存器输入可以理解为目的寄存器。分析该路径的目的主要是要保证外部器件的信号输出能够被FPGA内部寄存器正确寄存。

3、内部寄存器到外部输出引脚路径

内部寄存器到外部输出引脚路径可以简称为reg2output,FPGA的内部寄存器输出经过FPGA引脚到达外部器件。这时候FPGA内部的输出寄存器可以理解为源寄存器,外部器件可以理解为目的寄存器。分析这个路径的主要原因是在于FPGA的输出信号能够被外部器件正确寄存。如下图所示。

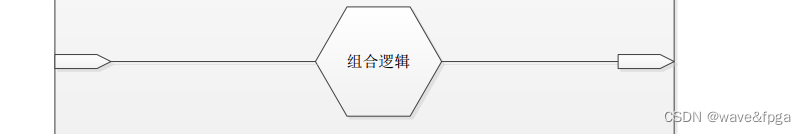

4、内部引脚输入到外部引脚输出路径

内部引脚输入到外部引脚输出路径可以简称为input2output,一般这种应用相当于信号的透传,经过FPGA内部具有一定的走线延时。设计者需要保证在一定的时间内,信号从输入引脚到达输出引脚,如下图所示。

二、总结

该小节主要分别详细介绍FPGA内部时序路径的四大类型。下一节主要介绍FPGA时序建立裕量分析。

本文详细介绍了FPGA内部的四种主要时序路径类型,包括寄存器到寄存器、外部输入到内部寄存器、内部寄存器到外部输出以及内部引脚输入到外部引脚输出,强调了理解这些路径对于有效设置时序约束的重要性。后续将探讨时序裕量分析的相关内容。

本文详细介绍了FPGA内部的四种主要时序路径类型,包括寄存器到寄存器、外部输入到内部寄存器、内部寄存器到外部输出以及内部引脚输入到外部引脚输出,强调了理解这些路径对于有效设置时序约束的重要性。后续将探讨时序裕量分析的相关内容。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?