文章目录

基础控制位

基础控制位是用于控制内存分页行为,主要为以下寄存器

- CR0寄存器: CR0寄存器的

WP(第16位)和PG位(第31位) - CR4寄存器: CR0寄存器的

PSE(第4位),PAE(第5位),PGE(第7位),PCIDE(第17位),SMEP(第20位),SMAP(第21位),PKE(第22位),CET(第23位)标志位 - MSR寄存器: IA32_EFER MSR寄存器

LME(第8位)和NXE(第11位)标志位 - EFLAGS寄存器:EFLAGS寄存器的

AC(第18位)标志位

程序可以通过设置CR0的PG位(以后表示为CR0.PG)来开启分页,在开启分页之前程序应该保证CR3寄存器所包含有效的物理地址

分页模式

如果CR0.PG=0则表示未启用分页模式,逻辑处理器将线性地址当做物理地址对待,CR4.PAE,IA32_EFER.LME,CR0.WP,CR4.PSE,CR4.PGE,CR4.SMEP

CR4.SMAP,IA32_EFER.NXE等标志位将会被忽视

如果CR0.PE=1(开启保护模式)并且CR0.PG=1时则表示启用分页模式,如果分页已经启用,可以使用3种分页模式,其中CR4.PAE和IA32_EFER.LME两个标志位

将决定启用的分页模式

- 如果CR0.PG=1并且CR4.PAE=0,则表示启用32位分页模式

- 如果CR0.PG=1,CR4.PAE=1,并且IA32_EFER.LME=0则启用PAE分页模式

- 如果CR0.PG=1,CR4.PAE=1,并且IA32_EFER.LME=1则启用4级分页模式,4级分页模式只能用于支持64位架构的处理器

3种分页模式的不同之处体现在:

- 线性地址宽度,可被用于转换的线性地址大小

- 物理地址宽度,可以被用于分页的物理地址大小

- 页大小,线性地址被映射的粒度,将同一页面上的线性地址转化为同一页面上对应的物理地址

- 提供禁用执行权限功能,有些分页模式可以防止程序从其他只读页面中获取执行指令

- 支持

PCID(进程上下文标识符,4级分页), 该功能可以使逻辑处理器可以缓存多个线性地址空间的信息,当程序在不同的线性地址之前切换时处理器可以保留缓存信息 - 支持保护锁(protection keys,4级分页),该功能可以为每个线性地址相关联的保护锁,程序可以使用新的控制寄存器来确定如何访问与保护锁关联的线性地址

以下是不同分页模式属性

| 分页模式 | CR0.PG | CR4.PAE | IA32_EFER.LME | 线性地址宽度 | 物理地址宽度 | 页大小 | 关闭执行权限 | PCID和保护锁 |

|---|---|---|---|---|---|---|---|---|

| 未分页 | 0 | N/A | N/A | 32 | 32 | N/A | NO | NO |

| 32位分页模式 | 1 | 0 | 0 | 32 | 上限为40位(2^40B) | 4KB,4MB | NO | NO |

| PAE分页模式 | 1 | 1 | 0 | 32 | 上限为52位(2^52B) | 4KB,2MB | Yes | NO |

| 4级分页 | 1 | 1 | 1 | 48 | 上限为52位(2^52B) | 4KB,2MB,1GB | Yes | Yes |

注意:

MAXPHYADDR获取物理地址宽度

4级分页功能只能用于IA-32模式

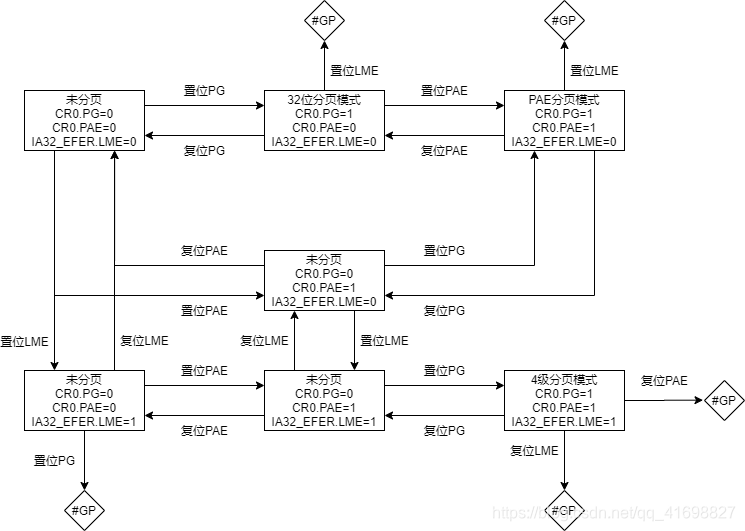

分页模式转换图

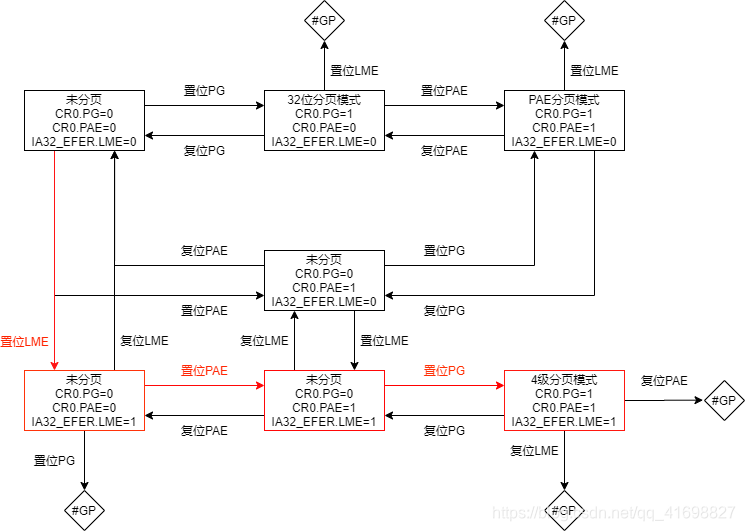

所以如果我们从未分页模式转为4级分页模式顺序如下

注意:

- 在64位模式下使用

canonical会产生一般保护异常(#GP);处理器不会尝试使用4级分页来转换non-canonical地址。- 当CR4.PAE=0且IA32_EFER.LME=1时,无法启用分页(通过将CR0.PG设置为1),如果将MOV指令修改CR0会导致一般保护异常(#GP)。

- 当启用4级分页(CR0.PG=1和IA32_EFER.LME=1)时,无法复位CR4.PAE,如果将MOV指令修改CR4会导致一般保护异常(#GP)。

- 无论当前使用哪种分页模式,都可以通过MOV指令复位CR0.1的CR0.PG来禁用分页

- 程序可以使用MOV指令置位/复位CR4.PAE在32位分页个PAE分页模式切换

- 4级分页模式不能直接转换到其他2种分页模式,必须复位CR0.PG位后清除CR4.PAE位和IA32_EFER.LME位之后重新置位CR0.PG位重新开启分页

分页内存的转化过程

每个分页结构大小为4096字节,并且包含单独的项,在32位分页中每一个项为32位(4字节)因此总共包含1024个项,在PAE分页模式和4级分页模式中每一个项为4位(8字节)因此总共包含512个项,PAE分页有一个特例是一个为32字节的分页结构,其中包含4个64位项处理器会使用线性地址的高位来标识分页结构的项,这些项的最后一个标识符用于将线性地址转换为物理地址所在的区域称为页帧,线性地址的低位用于标识线性地址转换后的特定地址称为页偏移

每个项包含一个物理地址,该地址可以是另一个分页结构的地址或者是页帧地址,如果一个项包含另一个分页结构的地址那么我们称为该项引用其他分页结构,如果一个项包含的是页帧,那么我们称为该项映射到页面

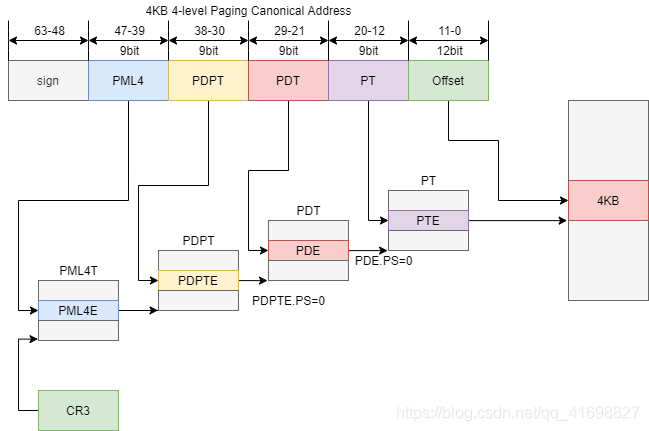

我们以IA-32e中的4级分页模式(4kb)来说明转换过程

通过CR3寄存器获取到第一个分页结构的地址,该分页结构包含512个项,然后将线性地址的[47:39]位(共9位)作为分页结构的索引来获取分页结构中的其中一个项,通过该项找到所引用的第二个分页结构,将线性地址的[38:30]位(共9位)作为第二个分页结构的索引在获取第二个分页结构中的其中一项,以此类推[29:21]作为第三个分页结构的项索引,然后[20:12]作为第4个页表结构的索引,该索引出的项为物理页面的起始地址,最后的[11:0]作为页偏移来定位物理地址,以上过程表示如下

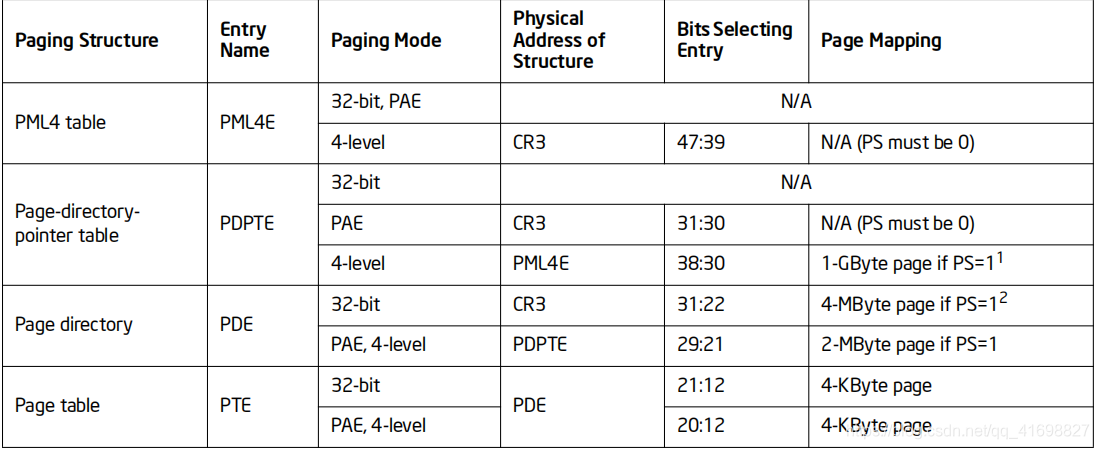

下表为不同分页模式的分页结构(PML4表示Page Map Level 4,4级页表)

因此如果我们要搞清楚分页内存,需要掌握这个东西(以PML4T为例)

可以将页表当做一个数组,那么每一项就是这个数组的每一个元素

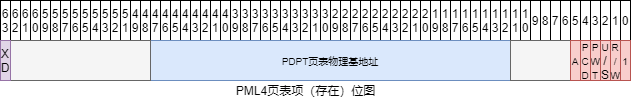

- 4级页表: 页表对应上表中的

PML4T(Page Map Level 4 Table),基地址由CR3提供,线性地址的47-39位用于索引 - 页表项: 对应上表中的

PML4E(Page Map Level Entry),每一项为提供了下一级页表的基地址 - 页表目录指针: 对应上表中的

PDPT(Page Directory Pointer Table) 基地址由PML4E提供,如果开启1GB分页,则线性地址的38-30位作为物理页的基地址,线性地址的29-0位作为物理页内偏移,如果开启2MB或4kb分页则线性地址的38-30位作为索引 - 页表目录项: 对应上表中的

PDPTE(Page Directory Pointer Table Entry) 如果开启1GB分页,该项会映射到对应的1GB物理页面,如果开启2MB或4KB提供了下一级页表的基地址 - 页目录: 对应上表中的

PD(Page Directory) 基地址由PDPTE提供,如果开启了2MB分页,则线性地址的29-21位作为物理页的基地址,线性地址的20-0位作为物理页内偏移,如果开启4KB分页,则线性地址的29-21位作为索引 - 页目录项: 对应上表中的

PDE(Page Directory Entry),如果开启2MB分页,该项会映射到对应的2MB物理页的基地址,如果开启4KB分页则提供了下一级页表基地址 - 页表: 对应上表中的

PT(Page Table) 基地址由PDE提供,线性地址的第20-12位提供了4KB物理页面的基地址 - 页表项: 对应上表中的

PTE(Page Table Entry) 该项会映射到4KB物理页面的基地址,线性地址的第11-0项作为物理页内偏移

4级分页(PML4T)

当同时置位CR0.PG,CR4.PAE,IA32_EFER.LME便可开启4页分页模式,在4级分页中可以将Canonical型地址映射到52位物理地址空间(由处理器的最高物理可寻址位宽MAXPHYADDR决定),可以在IA-32e模式下可寻址4PB的物理地址空间,以及256TB的线性地址空间

4级分页模式下各级页表项位功能

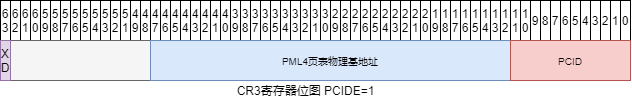

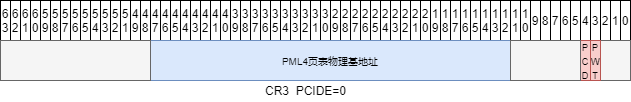

CR3寄存器:

- PTW: 页级直写模式(Page-level Write-through)

- PCD: 页级缓存禁用(Page-level Cache Disable)

PML4TE

<

<

本文详细介绍了Rust在开发操作系统中4级分页内存的原理,包括CR0和CR4寄存器、4级分页模式下的页表结构和转换过程,以及不同规格的物理页寻址。通过理解分页内存转化过程,建立页表索引,并抽象出页表项结构,为后续的页面映射奠定了基础。

本文详细介绍了Rust在开发操作系统中4级分页内存的原理,包括CR0和CR4寄存器、4级分页模式下的页表结构和转换过程,以及不同规格的物理页寻址。通过理解分页内存转化过程,建立页表索引,并抽象出页表项结构,为后续的页面映射奠定了基础。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2660

2660

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?