stm32 单片机时钟学习以及分析

1 引言:

单片机(Microcontrollers),采用超大规模集成电路技术把具有数据处理能力的中央处理器CPU、随机存储器RAM、只读存储器ROM、多种I/O口和中断系统、定时器/计数器等功能(可能还包括显示驱动电路、脉宽调制电路、模拟多路转换器、A/D转换器等电路)集成到一块硅片上构成的一个小而完善的微型计算机系统,在工业控制领域广泛应用。

单片机时钟可以说如同人的心脏那样重要,我们在心脏的搏动下进行自己的生命活动,同样的单片机在时钟下进行自己的控制活动。

2 时钟的分类:

单片机的时钟分为内部时钟与外部时钟:一般而言,内部时钟集成在芯片内部(RC振荡电路),其精度比较低;外部时钟,顾名思义,存在于芯片外部(晶体或陶瓷谐振器),可以为系统提供精确的时钟。

晶振是给单片机提供工作信号脉冲的,如图所示的为外部晶振,频率为4MHz,我们常用的晶振频率为12MHz,单片机工作时,是一条一条地从RoM中取指令,然后一步一步地执行。单片机访问一次存储器的时间,称之为一个机器周期,这是一个时间基准。—个机器周期包括12个时钟周期。如果一个单片机选择了12MHz晶振,它的时钟周期是1/12us,它的一个机器周期是12×(1/12)us,也就是1us。

有些晶振的频率并数是整数,如:11.0592MHz的晶振。单片机在进行串行通信时,常用的波特率为1200,2400,4800,9600,115200等,为了适应单片机的串口通讯波特率的计算而来的。用11.0592MHz晶振经过相应的分频或者倍频后刚好能够得出一个整数的波特率,这样在上位机和下位机的同步方面比较方便。

3 stm32的时钟来源

这里以stm32f1系列的芯片为例。

由上面可知,系统的时钟来源有内部时钟与外部时钟,详细的来说stm32f1有五个时钟源:

HSI(高速内部时钟)

HSE(高速外部时钟)

LSI(低速内部时钟)

LSE(低速外部时钟)

PLL(锁相环倍频输出)

每一个时钟都可以独立的开启与关闭。stm32的时钟来源众多,而且时钟配置相对复杂,为什么它要做的这么复杂呢?必然有其道理。我们知道,stm32功能强大,有着丰富的内置外设,而这些外设如果都使用一个时钟,也不是不可以,正如使用宰牛刀去杀鸡的道理一样,有些外设,并不需要很高的时钟,例如看门狗,对于同一个电路来说,时钟频率越高,功耗越大,而且易于受到外部电磁环境的干扰,因此,stm32才有这众多的时钟来源与复杂的时钟系统。

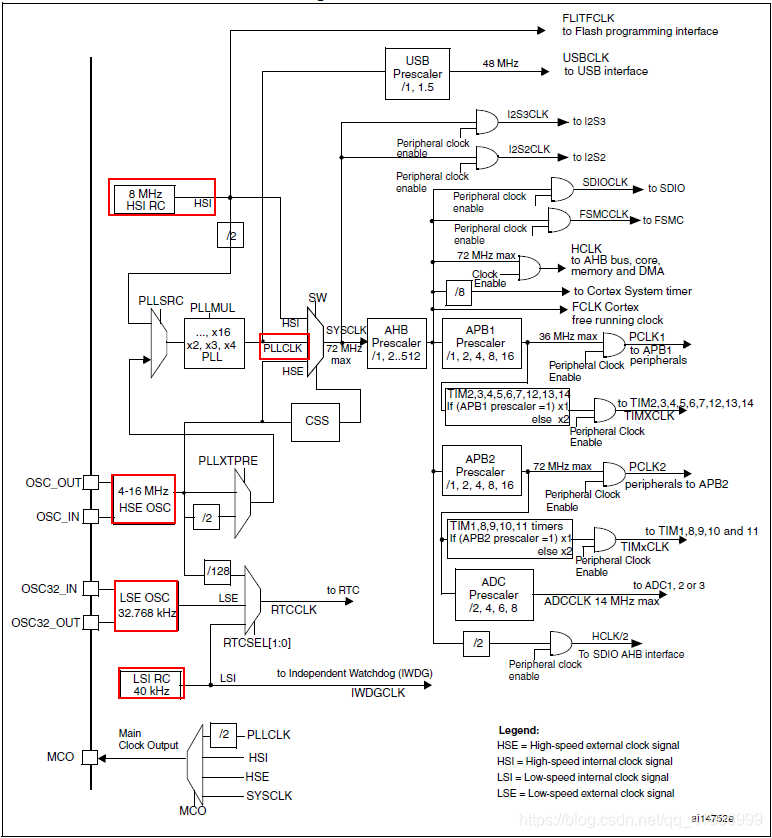

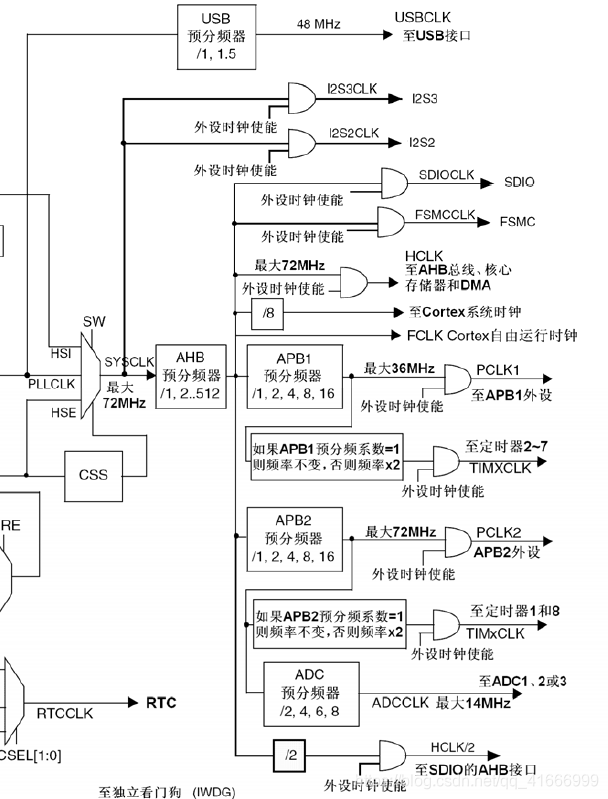

以下,我们结合stm32的时钟树来对stm32的时钟系统进行分析:

图中标红的部分为stm32f1的五个时钟来源

3.1 HSI(高速内部时钟):

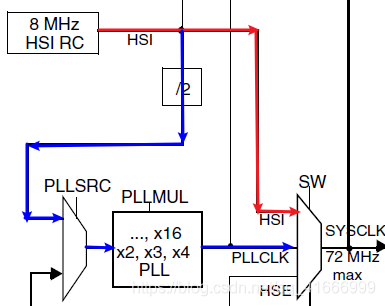

首先来看第一个8 MHz的HSI高速内部时钟

HSI的两条路径都到达了SW这个是系统时钟切换器,其中红色路径直接到达了SW;蓝色路径线到达了PLLSRC,而后经过PLL锁相环倍频后输出,形成PLLCLK,达到SW。时钟切换器选SYSCLK(系统时钟的来源)。

3.2 HSE(高速外部时钟)

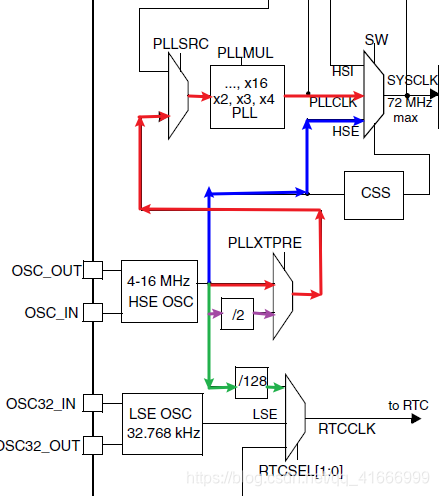

高速外部时钟,可接石英/陶瓷谐振器,或者接外部时钟源(例如另一单片机输出的时钟),频率范围为4MHz~16MHz。

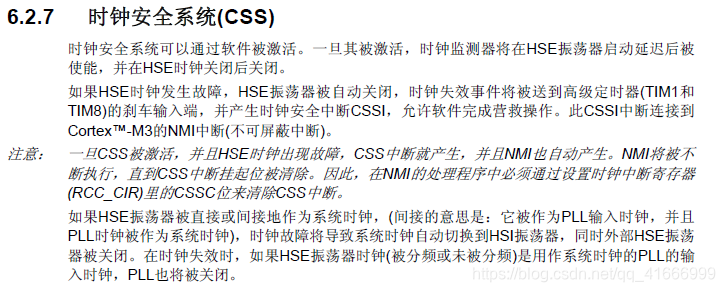

主要有三条路径:蓝色路径直接到达SW切换器;红色路径通过PLL,形成PLLCLK到达SW切换器;紫色路径同红色路径,只不过在经过PLL前先进行了二分频;绿色路径,经过128分频以后送到了RTCSCL(实时时钟选择器)进行时钟选择。其中CSS为时钟安全系统,详细的解释可以从STM32参考手册中查找到:

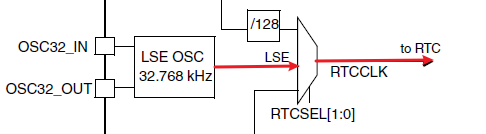

3.3 LSE(低速外部时钟)

LSE晶体是一个32.768kHz的低速外部晶体或陶瓷谐振器。它为实时时钟或者其他定时功能提供一个低功耗且精确的时钟源。至于这里外什么又使用不是整数的频率。从百度上找到如下解释:32.768KHZ的时钟晶振产生的振荡信号经过石英钟内部分频器进行15次分频后得到1HZ秒信号,即秒针每秒钟走一下,石英钟内部分频器只能进行15次分频要是换成别的频率的晶振,15次分频后就不是1HZ的秒信号,时钟就不准了。32.768K=32768=2的15次方,数据转换比较方便、精确。

可以看到LSE专用于为RTC提供精确的时钟。

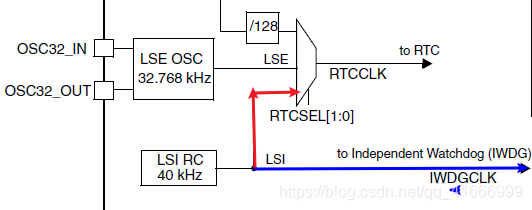

3.4 LSI(低速内部时钟)

通过红色路径,LSI给RTC提供时钟源,当然,这个时钟源并不准确;一般而言LSI为独立看门狗和自动唤醒单元提供时钟。

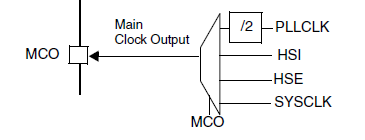

3.5 MCO(主时钟输出)

一个单片机可以输出相应的时钟可以通过引脚作为另一个单片机的输入时钟。

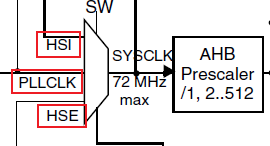

4 stm32的系统时钟

可以清楚地看到系统时钟的来源有三个:HSI、PLLCLK、HSE,并且系统时钟的频率最大为72MHz。例如:一个8MHz的晶振,经过PLLMUL进行9倍频,后输出72MHz的系统时钟频率。该系数由软件确定,只有在PLL关闭条件下才可以被写入。

5 stm32外设时钟

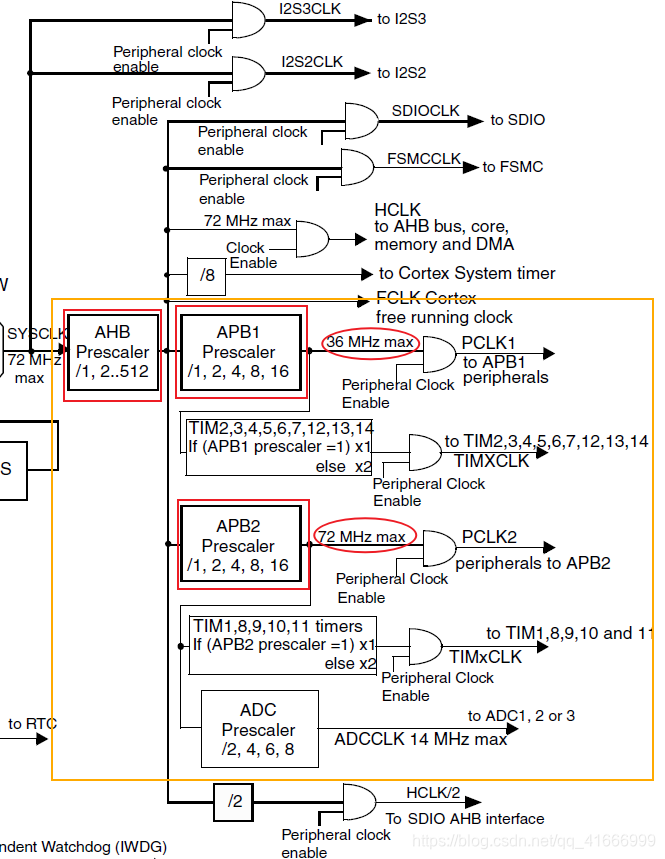

从上面图片可以看到stm32有着丰富的外设我们注意到在每一个外设初都有Peripheral clock enable 这个选项。我们知道这么多的外设,我们再一次任务中也不会全部都要使用,如果没有这个使能控制,那么当系统时钟开启后,全部的外设时钟将开始工作,但这是没有必要的,而且为了尽可能的减小功耗,所以才使用了这样的一个配置。

5.1 USB

其中USB比较特殊,这里将其单列出来。USB没有挂在SYSCLK,挂在了PLLCLK,这是由于USB在通信时对时钟要求比较高,而SYSCLK当其时钟来源是HSI时,时钟并没有很精确,因此才将USB挂在了PLLCLK上。

5.2 其它外设

这里重点想谈一下橘黄色方框里的内容。

其中AHB(Advanced High Performance Bus)为高级高性能总线,其进行相应的分频(1、2···512)后将时钟提供给外设。APB(Advanced Peripheral Bus)外围总线,分出来了两个APB1、APB2,我们可以看到APB2的最高频率要高于APB1,这是由于不同外设的需求来决定的,很好理解。

7354

7354

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?