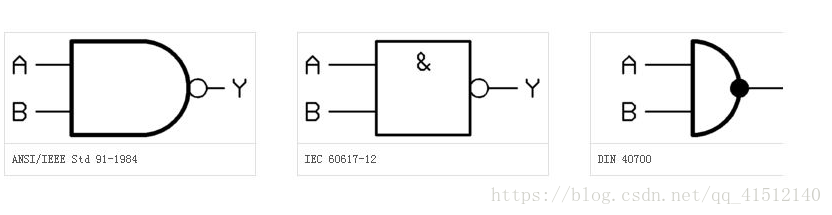

与非门(英语:NAND gate)是数字电路的一种基本逻辑电路。若当输入均为高电平(1),则输出为低电平(0);若输入中至少有一个为低电平(0),则输出为高电平(1)。与非门可以看作是与门和非门的叠加。

与非门是与门和非门的结合,先进行与运算,再进行非运算。与非运算输入要求有两个,如果输入都用0和1表示的话,那么与运算的结果就是这两个数的乘积。如1和1(两端都有信号),则输出为0;1和0,则输出为1;0和0,则输出为1。与非门的结果就是对两个输入信号先进行与运算,再对此与运算结果进行非运算的结果。简单说,与非与非,就是先与后非。电工学里一种基本逻辑电路,是与门和非门的叠加,有两个输入和一个输出。CMOS电路中的逻辑门有非门、与门、与非门、或非门、或门、异或门、异或非门,施密特触发门、缓冲器、驱动器等与非门则是当输入端中有1个或1个以上是低电平时,输出为高电平;只有所有输入是高电平时,输出才是低电平与非门芯片:74ls系列:74ls00、74LS20,CMOS系列:CD4011

当两个输入端都为低电平时,对应的发光二极管亮;当两个输入端输入不同电

平时,对应的二极管亮;当两输入端为高电平时,对应的发光二极管不亮。 4.与非门传输延迟特性。

实现与非门的非门功能并将两输出端串联进另一芯片的两输入端依此实现与非门传输延迟特性。

与非门的用法和特点

与非门:数字电路基本逻辑电路

与非门:数字电路基本逻辑电路

4115

4115

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?