文章目录

- 运放的基本参数

- 1.失调电压(OFFSET VOLTAGE)<center>

- 2. 输入偏置电流(INPUT BIAS CURRENT)<center>

- 3. 噪声(NOISE)<center>

- 4. 输入电压范围(INPUT VOLTAGE RANGE) <center>

- 5. 输入阻抗(INPUT IMPEDANCE)

- 6. 开环电压增益(Open-loop voltage gain)<center>

- 7. 频率响应(FREQUENCY RESPONSE)<center>

- 8. 输出(OUTPUT)

- 9. 电源(POWER SUPPLY)

- 10. 关断(SHUTDOWN)

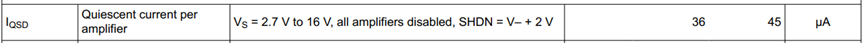

- 10.1 每个放大器的静态电流(Quiescent current per amplifier) I Q S D {{I}_{QSD}} IQSD

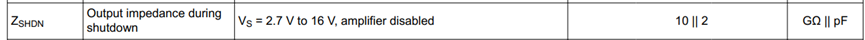

- 10.2 关断时的输出阻抗(Output impedance during shutdown) Z S H D N {{Z}_{SHDN}} ZSHDN

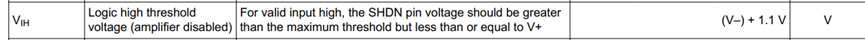

- 10.3 逻辑高电平阈值电压(放大器被禁用)(Logic high threshold voltage (amplifier disabled)) V I H {{V}_{IH}} VIH

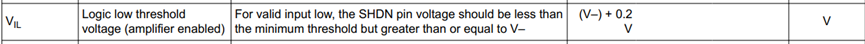

- 10.4 逻辑低电平阈值电压(放大器被启用)(Logic low threshold voltage (amplifier enabled)) V I L {{V}_{IL}} VIL

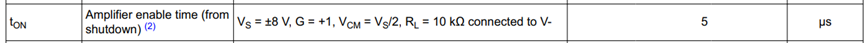

- 10.5 放大器启用时间(从关断开始)(Amplifier enable time (from shutdown)) t O N {{t}_{ON}} tON

- 10.6 放大器禁用时间(Amplifier disable time) t O F F {{t}_{OFF}} tOFF

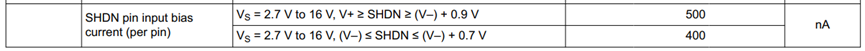

- 10.7 SHDN 引脚输入偏置电流(每个引脚)(SHDN pin input bias current (per pin))

运放涉及的知识点太多了,文章里仅做了简要的分析,后续对重要参数单独解释。

运放的基本参数

在 VS = (V+) – (V– ) = 2.7V 至 16V( ±1.35V 至 ±8V) 、 TA = 25°C、 RL = 10kΩ( 连接至 VS/2) 、 VCM = VS/2 且 VOUT = VS/2 条件下测得( 除非另有说明) 。

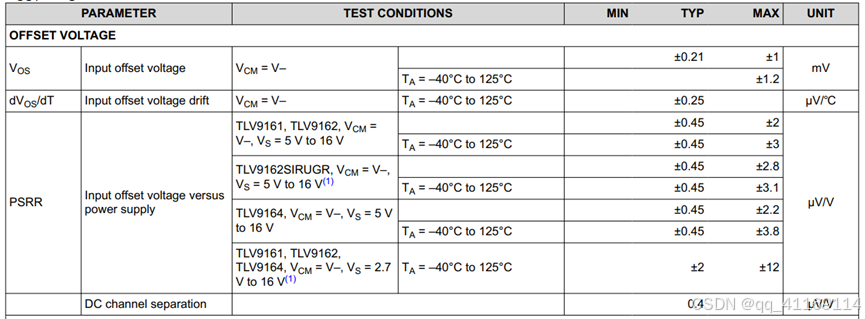

1.1 输入失调电压(Input offset voltage) V o s {{V}_{os}} Vos

\hspace{2em}

理想状态下,如果运算放大器的两个输入端电压完全相同,输出应为0 V。实际上,运放的输出不为零,必须在输入端施加小差分电压,强制输出达到0。该电压称为输入失调电压

V

o

s

{V_{os}}

Vos。如图1所示运放TLV916x输入失调电压

V

o

s

{V_{os}}

Vos典型值为±0.21mv。

\hspace{2em}

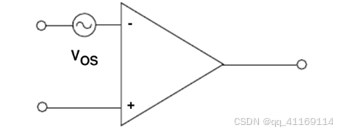

输入失调电OS压可以看成是电压源

V

o

s

{V_{os}}

Vos,与运算放大器的反相输入端串联,如下图所示。这个电压算是一个零补偿电压。

1.2输入失调电压温漂(Input offset voltage drift) d V o s / d T {d{{V}_{os}}/dT} dVos/dT

\hspace{2em} V o s {V_{os}} Vos随温度变化的变化量,通常单位为 μV/°C 或 nV/°C。如图1所示运放TLV916x输入失调电压温漂[d{{V}_{os}}/dT]典型值为±μV/°C。比如:25°C 时 V o s {V_{os}} Vos=1mV,但温度升到 50°C 时可能变成 V o s {V_{os}} Vos=1.2mV,这个变化就是“温漂”。

1.3输入失调电压与电源间的关系(Input offset voltage versus power supply)PSRR

\hspace{2em}

PSRR也叫电源抑制比,描述了电路抑制任何电源变化传递到其输出信号的能力,通常以dB为单位进行测量,用来描述输出信号受电源影响。理想运算放大器的PSRR为零。但是,实际运算放大器的PSRR与频率有关。信号频率越高,PSRR越低。PSRR通常根据输入来衡量,但没有行业标准。

\hspace{2em}

如图所示运放TLV9161的PSSR为±0.45μV/V。电源电压每变化 1V,输入失调电压最多变化 ±0.45 μV。转换为 dB为

PSRR ( dB ) = 20 log 10 ( ) = 20 log 10 ( 1 V 0.45 × 10 − 6 V ) ≈ 126 dB \text{PSRR}(\text{dB})=20{{\log }_{10}}\left( \frac{}{} \right)=20{{\log }_{10}}\left( \frac{1\text{V}}{0.45\times {{10}^{-6}}\text{V}} \right)\approx 126\text{dB} PSRR(dB)=20log10()=20log10(0.45×10−6V1V)≈126dB

\hspace{2em} 例如:电源从 5.0V 变到 4.9V(变化 0.1V),输入失调电压变化0.45μV/V×0.1V=0.045μV. 若电路增益为 100 倍,输出误差:0.045 μV × 100 = 4.5 μV

1.4直流通道隔离(DC channel separation)

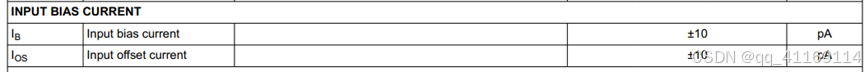

2. 输入偏置电流(INPUT BIAS CURRENT)

\hspace{2em}

输入偏置电流和失调电流在我另一篇博客里有讲到运算放大器失调电流和平衡电阻的计算。

2.1输入偏置电流(Input bias current) I B {{I_B}} IB

2.2输入失调电流(Input offset current) I O S {{I}_{OS}} IOS

3. 噪声(NOISE)

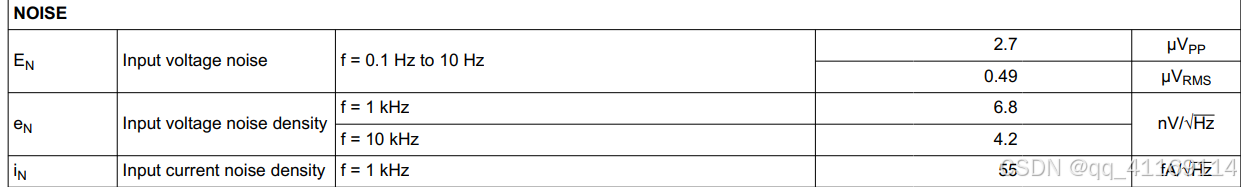

3.1 输入电压噪声(Input voltage noise) E N {{E}_{N}} EN

\hspace{2em}

输入电压噪声定义为,屏蔽良好、无信号输入的的运放,在其输出端产生的任何交流无规则的干扰电压。这个噪声电压折算到运放输入端时,就称为运放输入噪声电压(有时也用噪声电流表示)

\hspace{2em}

输入电压噪声,表示在指定频率范围内,运算放大器输入端的电压噪声。数据手册的值解释如下:

\hspace{4em}

• 频率范围:

f

=

0.1

Hz

f = 0.1 \, \text{Hz}

f=0.1Hz 到

10

Hz

10 \, \text{Hz}

10Hz

\hspace{4em}

• 单位:

μ

V

pp

\mu V_{\text{pp}}

μVpp(峰峰值)

\hspace{4em}

• 值:

2.7

μ

V

pp

2.7 \, \mu V_{\text{pp}}

2.7μVpp

这意味着在

0.1

Hz

0.1 \, \text{Hz}

0.1Hz 到

10

Hz

10 \, \text{Hz}

10Hz 频率范围内,输入电压噪声的峰峰值最大为 2.7 微伏。

3.2 输入电压噪声密度(Input voltage noise density) e N {{e}_{N}} eN

\hspace{2em}

电压噪声密度是指运放在单位频率带宽内产生的电压噪声的有效值。它描述了运放噪声随频率变化的特性。在数据手册中,电压噪声密度通常以图形的方式给出,即电压噪声密度曲线(也称为噪声频谱密度曲线)。这条曲线展示了运放在不同频率下的噪声水平,从而帮助设计者评估运放在不同应用场景下的噪声性能。噪声密度表示器件在1 Hz带宽内产生的噪声电压或电流,反映噪声的频谱分布特性。

\hspace{2em}

电压噪声密度曲线通常分为白噪声区域和1/f噪声区域。白噪声区域的噪声密度与频率无关,表现为一条水平线;而1/f噪声区域的噪声密度则随频率的降低而增加,表现为一条斜线。在数据手册中,通常会给出白噪声和1/f噪声的电压噪声密度值,以及他们对应的频率范围。

\hspace{2em}

•

e

N

{{e}_{N}}

eN: 输入电压噪声密度,表示单位频宽内的电压噪声。这个值用来描述在特定频率下每单位频率带宽所贡献的噪声量。

\hspace{2em}

• 频率:

f

=

1

kHz

f = 1 \text{kHz}

f=1kHz 和

f

=

10

kHz

f = 10 \text{kHz}

f=10kHz

\hspace{2em}

• 单位:

nV

/

Hz

\text{nV} / \sqrt{\text{Hz}}

nV/Hz(纳伏每根号赫兹)

\hspace{2em}

• 值: 在

1

,

kHz

1 , \text{kHz}

1,kHz 时为

0.49

0.49

0.49 微伏 RMS(均方根值)

\hspace{4.5em}

在

10

,

kHz

10 , \text{kHz}

10,kHz 时为

6.8

,

nV

/

Hz

6.8 , \text{nV} / \sqrt{\text{Hz}}

6.8,nV/Hz

这意味着在

1

kHz

1\text{kHz}

1kHz 频率下,输入电压噪声密度为

0.49

0.49

0.49 微伏 RMS,而在

10

,

kHz

10 , \text{kHz}

10,kHz 时,噪声密度为

6.8

,

nV

/

Hz

6.8 , \text{nV} / \sqrt{\text{Hz}}

6.8,nV/Hz。

3.3 输入电流噪声密度(Input current noise density) i N {{i}_{N}} iN

\hspace{2em}

是一个表示运算放大器或其他电子设备在输入端所产生的电流噪声的参数。它通常用单位频率带宽(每根号赫兹,fA/Hz\text{fA}/\sqrt{\text{Hz}}fA/Hz)来表示,即每根号赫兹的电流噪声大小。

输入电流噪声密度描述了设备输入端的电流噪声量,通常与频率相关。换句话说,表示在一定频率下,单位频带内由输入端电流噪声所引起的噪声大小。例如,表格中给出的输入电流噪声密度为 55 fA/Hz\sqrt{\text{Hz}}Hz,表示在 1 kHz 频率下,输入电流噪声为 55 微安每根号赫兹。

4. 输入电压范围(INPUT VOLTAGE RANGE)

4.1 共模电压范围(Common-mode voltage range) V C M {{V}_{CM}} VCM

\hspace{2em} 共模输入电压是指运放的两个输入引脚电压的平均值;从数据手册可知运放TLV916x是一个“轨到轨输入运算放大器”,可以涵盖整个电源范围。许多轨到轨输入运算放大器的确涵盖了整个电源范围(例如:TLV916x),但有一些则没有全覆盖(例如TI的轨到轨运放OPA4197),而其描述对人具有一定的误导性,它并不是0~VCC。所以,检查产品说明书中的规定输入范围至关重要。

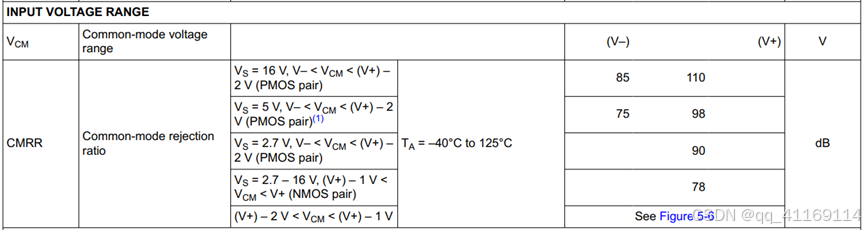

4.2 共模抑制比(Common-mode rejection ratio) CMRR

\hspace{2em}

共模抑制比是模拟电路中差分放大器(或者其他电子器件)的一个用于衡量其抑制两端输入信号共模部分的一个参数。共模信号是指同时存在于两个输入端并具有相同大小和相位的信号,例如电源噪声、接地干扰或其他外部干扰。共模抑制比是通过测量输入共模信号与输出共模信号之间的差异来确定设备抑制干扰信号的能力。共模抑制比不仅会对运放电路的精度产生影响,而且对电路的EMI性能也有着重要意义,因此搞懂运放的CMRR很重要。

\hspace{2em}

数学描述为:

CMRR

=

20

log

10

(

A

d

A

cm

)

(:dB)

\text{CMRR}=20{{\log }_{10}}\left( \frac{{{A}_{\text{d}}}}{{{A}_{\text{cm}}}} \right)\quad \text{(}\text{:dB)}

CMRR=20log10(AcmAd)(:dB)

\hspace{8em}

Ad:差模增益(对有用信号的放大倍数)。

\hspace{8em}

Acm:共模增益(对共模干扰的放大倍数)。

从公式可知,CMRR越大抗抗干扰能力越强,精度越高。

5. 输入阻抗(INPUT IMPEDANCE)

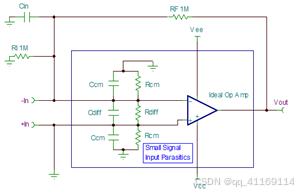

\hspace{2em} 下图形象的说明了运放的输入端阻抗的特性。主要有两个参数,输入阻抗和输入电容。对于电压反馈型运放,输入阻抗主要由输入级的决定,一般BJT输入级的运放。的共模输入阻抗会大于40MΩ。差模输入阻抗大于200GΩ。对于JFET和CMOS输入级的运放,输入阻抗要大的多。这个阻抗通常表现为电阻性。作为常识被我们所熟知。

\hspace{2em} 更值得我们多加关注的是运放的输入电容。这个参数通常在datasheet的表格中所列出,但常被忽视。运放的输入电容,通常分为共模输入电容Ccm和差模输入电容Cdiff。

\hspace{2em} 运放的输入共模电容Ccm 和差模电容 Cdiff会形成运放的输入电容 Cin。在许多应用中,运算放大器的输入电容都不会造成问题。但在某些应用中会引起放大电路的不稳定。尤其是反向输入端的电容,是放大电路不稳定的几大罪魁祸首之一。

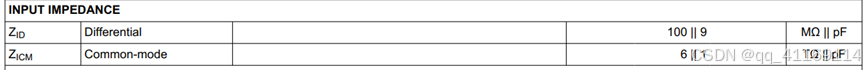

5.1 差分(Differential) Z I D {{Z}_{ID}} ZID

\hspace{2em} 在datasheet中可知,TLV916x的差分阻抗为100MΩ,差分电容为9pf。

5.2 共模(Common-mode) Z I C M {{Z}_{ICM}} ZICM

\hspace{2em} 在datasheet中可知,TLV916x的共模阻抗为100TΩ,差分电容为1pf。

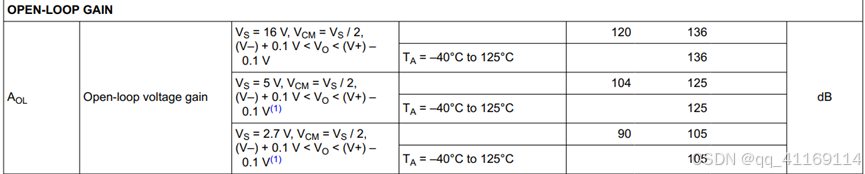

6. 开环电压增益(Open-loop voltage gain)

\hspace{2em}

开环增益的简单理解就是没有反馈回路时放大器的增益,此增益是放大器独有的属性,与外围电路无关。而闭环增益是存在反馈回路时的增益。这意味着;当你给运放输入一个微小的电压变化时;它能够将这个变化放大成一个相对较大的输出信号。如果输入电压仅为1mV,运放的开环增益为10万倍时,输出电压就可以达到100V!这样的增益数值虽然令人震惊,但也是运放在没有反馈的情况下的典型表现。开环电压增益并非是无限制的。

\hspace{2em}

频率升高,运放的增益通常会发生下降。这是因为运放的内部电路受限于其设计特性,频率增高时增益的稳定性会下降表现为增益带宽的限制。受电源轨的限制,开环输出不可能无限制增大。

\hspace{2em}

虽然开环增益很高,但在实际应用中运放大多是工作在闭环条件下即通过反馈网络来控制增益。在这种情况下。开环增益就不再直接影响信号的放大倍数。我们通常会通过外部的反馈元件(如电阻、电容等)来设定所需的增益值。使其更加精确以及稳定。这也是为什么运放的开环增益越大,系统的闭环增益控制就越有优势的原因。需要注意得是开环增益并非越高越好。过高得增益虽然能带来更强得信号放大能力,但也可能增加系统的噪声水平。过强的增益容易让信号中的微弱噪声被放大,甚至引发系统的不稳定性,尤其是在高增益应用中。

\hspace{2em}

开环增益对运放对其他性能指标也有着直接影响。比如运放得输入偏置电流、输入失调电压等都受到开环增益得制约。如果增益过大,输入端的微小变化就可能被过度放大,导致电路的误差增加。减少这些误差,现代运放设计中常采用多级增益结构;通过对增益的合理分配以及控制;致使系统在高增益的尽量避免误差的扩大。

7. 频率响应(FREQUENCY RESPONSE)

7.1 增益带宽积(Gain-bandwidth product) GBW

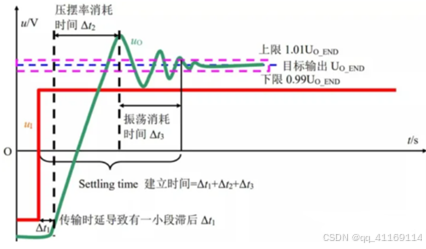

7.2 压摆率(Slew rate) SR

\hspace{2em}

压摆率(Slew Rate, SR) 是运算放大器(运放)输出电压的最大变化速率,表示运放对快速输入信号的响应能力。这个参数不仅仅出现在运放中,在其他电子元件中也有。假设运放输出一个阶跃信号,理想的输出是直接垂直上升的直线(瞬时完成),但由于实际运放的压摆率限制,输出信号会以一定的最大斜率上升,形成斜坡状的波形。

\hspace{2em}

受限于压摆率(SR),运放的输出电压无法无限快速地变化,其变化速率存在最大值。因此,输出信号的上升过程会表现为一个固定斜率的斜坡,斜率大小由SR决定:

实际输出斜率

=

Δ

t

Δ

V

≤

S

R

\text{实际输出斜率}= {{\Delta t} \over {\Delta V}} \le SR

实际输出斜率=ΔVΔt≤SR

其中

Δ

V

{}\Delta {}V

ΔV为电压变化量,

Δ

t

{}\Delta {}t

Δt为上升时间。

关键影响:

- 信号失真:高频或大幅值信号中,SR不足会导致波形畸变(如正弦波变三角波、方波边沿变缓)。

- 动态性能限制:SR直接决定运放处理快速变化信号的能力,尤其在脉冲、音频、视频等应用中至关重要。

压摆率是运放动态性能的核心参数,它量化了输出电压的最大变化速率。实际设计中,需通过计算信号斜率需求来匹配运放的SR,避免高速信号因SR不足而失真。

理论计算:

\hspace{2em} 若输出正弦波 V out = A sin ( 2 π f t ) V_{\text{out}} = A \sin(2 \pi f t) Vout=Asin(2πft),则最大斜率(SR需求)为:

SR required = 2 π f A \text{SR}_{\text{required}} = 2 \pi f A SRrequired=2πfA

示例:

\hspace{2em} 输出 10 MHz、1 Vpp 正弦波,所需 SR:

SR = 2 π × 10 MHz × 1 V ≈ 63 μ V/s \text{SR}=2\pi \times 10\text{MHz}\times 1\text{V}\approx 63\mu \text{V/s} SR=2π×10MHz×1V≈63μV/s

\hspace{2em} 若运放 SR = 20 V/µs,信号会严重失真。

实测方法:

\hspace{2em}

输入方波,测量输出波形的上升时间

t

r

{ t_r }

tr:

SR = Δ V Δ t \text{SR} = \frac{\Delta V}{\Delta t} SR=ΔtΔV

\hspace{2em} 如 0 V → 5 V 耗时 0.1 µs,则 SR = 50 V/µs

\hspace{2em} 压摆率这里还有一个转换率的概念。

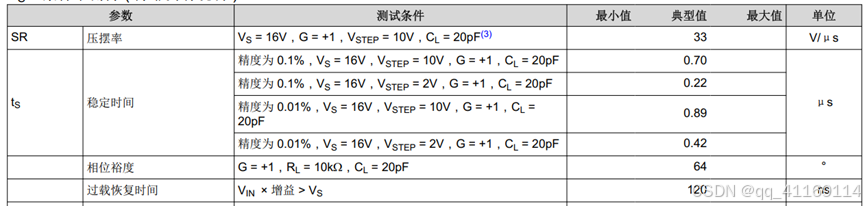

7.3 稳定时间(Settling time) t S {{t}_{S}} tS

\hspace{2em}

稳定时间(Settling Time) 是指运算放大器(运放)的输出电压从阶跃响应开始,到最终稳定在目标值附近一个指定误差带(如±0.1%、±1%)内所需的时间。

稳定时间通常分为两个阶段:

\hspace{2em}

大信号响应阶段(Slew-Limited Phase):

\hspace{2em}

\hspace{2em}

输出电压以最大压摆率(SR)快速变化,斜率受SR限制。

\hspace{2em}

小信号稳定阶段(Linear Settling Phase):

\hspace{2em}

\hspace{2em}

输出接近目标值时,进入线性区,由运放的带宽和阻尼特性决定收敛速度。

\hspace{2em}

稳定时间的概念可以由下图直观地展示:

7.4 相位裕度(Phase margin)

\hspace{2em}

相位裕度(Phase Margin, PM)本质上是描述闭环系统稳定性的参数,但它的分析需要结合运放的开环频率响应。

相位裕度的核心逻辑

(1)开环分析,闭环应用

- 开环频率响应:

\hspace{2em} 相位裕度是通过运放的开环增益-相位曲线(波特图)计算得出的,即在开环状态下测量增益和相位随频率的变化。 - 闭环稳定性:

\hspace{2em} 但这一开环特性的目的是为了预测闭环后的稳定性(如单位增益缓冲器 G = 1 G = 1 G=1 时的表现)。

(2)为什么需要开环数据?

\hspace{2em}

闭环系统的稳定性由开环传递函数的幅值裕度和相位裕度决定(源自控制理论的奈奎斯特稳定性判据)。

- 单位增益频率(

f

u

n

i

t

y

{f_{{\rm{unity}}}}

funity):

• 开环增益降为 1(0 dB)时的频率点,此处的相位滞后决定了闭环稳定性。

• 相位裕度描述的是“闭环系统的稳定性”,但需通过开环频率响应分析得出。相位裕度通过开环数据预测闭环稳定性,二者密不可分。数据表中标注的PM值(如64°)已隐含闭环测试条件(如 G=1),实际上数据手册确实给出了。

\hspace{2em} 总之这是参数是讨论开环传递函数和闭环系统稳定性的关系(经典控制理论中有讲)。这里给出结论:

相位裕度对稳定性的影响

• 相位裕度 > 45°:如果相位裕度大于 45°,闭环系统通常是非常稳定的,反应平稳,不容易出现振荡。

• 相位裕度 30° 到 45°:相位裕度在此范围内时,系统稳定性良好,但可能会出现轻微的过渡响应,表现为轻微的震荡。

• 相位裕度 10° 到 30°:相位裕度较小,系统可能有较大的过渡响应,且易于出现轻微的振荡。稳定性较差。

• 相位裕度 < 10°:如果相位裕度过小,系统容易不稳定,并且可能在某些频率下产生持续振荡。

7.5 过载恢复时间(Overload recovery time)

\hspace{2em}

运放的过载状态通常发生在输入信号超过了运放的输入范围或输出超出了运放的输出范围时。常见的过载情形包括:

输入信号过大:当输入信号超出运放的输入线性范围时,运放的输入级无法正常处理信号,从而进入饱和状态。

输出信号过大:当输入信号过大,或反馈设计不当时,运放的输出可能会饱和到供电电压的极限(例如,正电源或负电源电压)。

\hspace{2em}

在过载状态下,运放的输出可能被“锁定”在接近电源电压的极限值,不再按照输入信号的变化而变化。

过载恢复的过程

\hspace{2em}

一旦输入信号恢复到可接受的范围或被调节到线性区域,运放需要一定的时间来从饱和状态恢复。这一过程涉及以下几个步骤:

\hspace{2em}

输入信号恢复到线性范围:过载恢复通常从输入信号恢复到正常范围开始。如果输入信号回到正常范围,运放会逐渐从饱和状态恢复。

\hspace{2em}

输出电压变化:运放的输出将随着输入信号的变化逐渐回到预期的线性响应。

\hspace{2em}

恢复到稳定状态:最终,运放的输出信号会回到预期的线性区域,恢复到正常的工作状态。

7.6 总谐波失真 + 噪声(Total harmonic distortion + noise) THD+N

\hspace{2em} 运放的总谐波失真(THD)是当运放的输入信号为纯的正弦波时(这里说纯的正弦波是指无谐波的正弦波),运放的输入信号中的各次谐波(2次,3次,至n次)的均方根值,与输出号基波的RMS值之比。定义如下式:

THD = V 2 2 + V 3 2 + V 4 2 + … + V n 2 V s \text{THD}=\frac{\sqrt{{{\text{V}}_{2}}^{2}+{{\text{V}}_{3}}^{2}+{{\text{V}}_{4}}^{2}+\ldots +{{\text{V}}_{\text{n}}}^{2}}}{{{\text{V}}_{\text{s}}}} THD=VsV22+V32+V42+…+Vn2

\hspace{2em} 其实际测试时,一般只测试前五次谐波(2次到6次)。这是因为谐波的幅值随着谐波阶次的增高而快速降低。六次以上的谐波已经占总谐的比率非常小,相对来说只是毛毛雨啦。因此只测前五次谐波已经充分反应全部的谐波成份了。(当然在有些厂商的ADC中它们会测量到2-9次谐波,这样的结果会更精确)

\hspace{2em} 运放的总谐波失真加噪声很好理解,就是上式分母中再加上噪声RMS值,定义如下式。式中的Vnoise是指可测量带宽内的噪声的RMS值。

T H D = V 2 2 + V 3 2 + V 4 2 + … + V n 2 + V n o i s e 2 V s {\rm{THD}} = {{\sqrt {{{\rm{V}}_2}^2 + {{\rm{V}}_3}^2 + {{\rm{V}}_4}^2 + \ldots + {{\rm{V}}_{\rm{n}}}^2 + {\rm{V}}_{{\rm{noise}}}^2} } \over {{{\rm{V}}_{\rm{s}}}}} THD=VsV22+V32+V42+…+Vn2+Vnoise2

\hspace{2em} 好多厂家的数据手册中,标示的THD其实代表着THD+N,这是因为大部分测试系统并没有区分与信号相关的谐波和其它噪声信号。

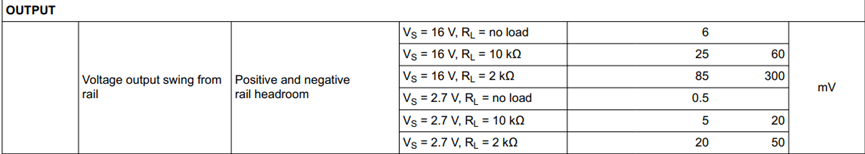

8. 输出(OUTPUT)

8.1 相对于电源轨的电压输出摆(Voltage output swing from rail)

\hspace{2em}

该运放是轨对轨的输出。但是实际输出不可能达到100%输出。对于普通运放,比如15V供电时,说输出电压摆幅可以达到13.5V,其实输出电压接近13.5V时,运放的特性就开始变差,主要表现在放大倍数急剧下降,信号开始失真,增益越大失真越严重。Rail to Rail运放的广告宣传中会说能达到正负电源的输出范围,实际上,当信号与电源轨的距离小于300mv时,放大器就会开始产生失真。

\hspace{2em}

那什么时候可以相信datasheet上标称的电压摆幅呢?把运放当做比较器用的时候!Rail to rail运放作为比较器用的时候,其输出电压可以非常接近电源轨,一般只有20mv左右的距离。建议:普通运放电源的正负极电压应该分别比要求的输出电压高2V以上,RailtoRail型运放应该高300mV以上。

8.2 短路电流(Short-circuit current) I S C {{I}_{SC}} ISC

\hspace{2em}

输出电路时候的电流。

8.3 容性负载驱动(Capacitive load drive) C L O A D {{C}_{LOAD}} CLOAD

\hspace{2em}

运算放大器(或其他驱动器)在其输出端接电容负载时的稳定性和驱动能力。

\hspace{2em}

驱动ADC采样电容时,Capacitive Load Drive 很关键

8.4 开环输出阻抗(Open-loop output impedance) Z O {{Z}_{O}} ZO

\hspace{2em}

在没有负反馈(开环)条件下,运算放大器输出端对外呈现的阻抗。

9. 电源(POWER SUPPLY)

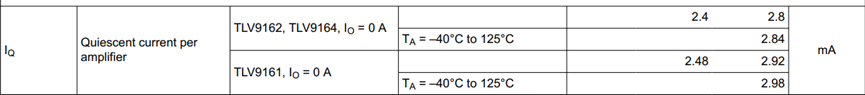

9.1 每个放大器的静态电流(Quiescent current per amplifier) I Q {{I}_{Q}} IQ

\hspace{2em}

在无输入信号、无负载的情况下,每个放大器所消耗的电源电流。可以把它理解为:运放“空闲待机”时就要吃掉的那点电流。它不参与输出,也不是由负载引起的,而是运放自身内部电路(偏置电流、电压级、缓冲器等)工作的基本功耗。

\hspace{2em}

每个放大器:是指每个通道。

\hspace{2em}

低功耗应用(电池供电、可穿戴设备)需要选用低静态电流的运放

\hspace{2em}

在多通道应用中,总静态功耗 = 每个通道的静态电流 × 通道数

\hspace{2em}

影响整体系统待机功耗与热设计

10. 关断(SHUTDOWN)

10.1 每个放大器的静态电流(Quiescent current per amplifier) I Q S D {{I}_{QSD}} IQSD

\hspace{2em}

在关断状态的静态电流。就是在失能是的静态电流。可以看出SHDN引脚拉高的时候,功耗会显著降低。

10.2 关断时的输出阻抗(Output impedance during shutdown) Z S H D N {{Z}_{SHDN}} ZSHDN

\hspace{2em}

SHDN引脚拉高的时候对外的阻抗。

10.3 逻辑高电平阈值电压(放大器被禁用)(Logic high threshold voltage (amplifier disabled)) V I H {{V}_{IH}} VIH

\hspace{2em}

SHDN引脚的高电平阈值。超过此电压,SHDN识别为高电平。

10.4 逻辑低电平阈值电压(放大器被启用)(Logic low threshold voltage (amplifier enabled)) V I L {{V}_{IL}} VIL

\hspace{2em}

SHDN引脚的低电平阈值。低于此电压,SHDN识别为低电平。

10.5 放大器启用时间(从关断开始)(Amplifier enable time (from shutdown)) t O N {{t}_{ON}} tON

\hspace{2em}

SHDN启动时需要的时间。

10.6 放大器禁用时间(Amplifier disable time) t O F F {{t}_{OFF}} tOFF

\hspace{2em}

SHDN关闭时需要的时间。

10.7 SHDN 引脚输入偏置电流(每个引脚)(SHDN pin input bias current (per pin))

\hspace{2em}

每个SHDN引脚的漏电流,(多通道的运放会有多个SHDN引脚)

6921

6921

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?