最近对serdes CDR 突然性的感兴趣,而我本人是名数字IC工程师,对于FFE、CTLE(高通滤波器,前仿真可以确定参数),大家都可能比较好理解,说白了,纯模拟电路占比的比较多,无非一些关键参数可以通过数字寄存器进行配置。对于DFE 可能大家肯定由如下几个问题:

1ui delay 延迟要求由来

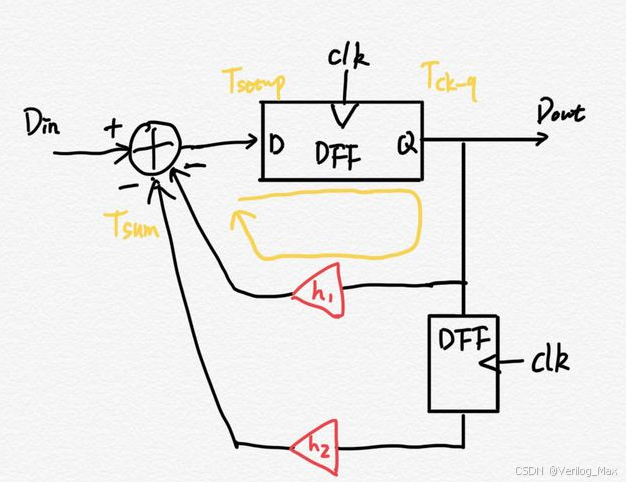

对于 1 tap

即 Tsetup + tck-q + Tsum <= 1ui,这样才能使当前 1bit ui 的判决结果必须在下一拍数据到来时,对其产生负反馈作用。

那 2 tap ,是不是 ,是不是delay 变成了 2Ui

看你怎么理解,如果从D in 计算delay 的话,的确判决结果 必须在 2 Ui 内 反馈至Din,即H2 路径。

也可以理解成1ui ,即从2 tap 的路径DFF判决结果开始计算,也必须满足1ui

多tap dfe 说白了就是多bit 之前的判决结果对当前单前1bit 信号进行反馈补偿。

ps:码间串扰不仅影响后1bit信号,由于高频信号的拖尾很严重,可能会影响后面几bit 甚至更多,因此多tap DFE 也是当前CDR电路比较热门的优化方向。

1116

1116

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?