1、一个4体并行低位交叉存储器,每个模块的容量是64K×32位,存取周期为200ns,假定四个存储可以连续访问,以下说法中,( )是正确的。(单选)

A.在连续工作一段时间后,200ns内储器向CPU提供256位二进制信息

B.连续工作一段时间后,200ns内存储器向CPU提供128位二进制信息

C.在连续工作一段时间后,200ns存储器向CPU提供32位二进制信息

D.以上答案都不正确

对于CPU来说可以同时访问四个模块 4X32=128

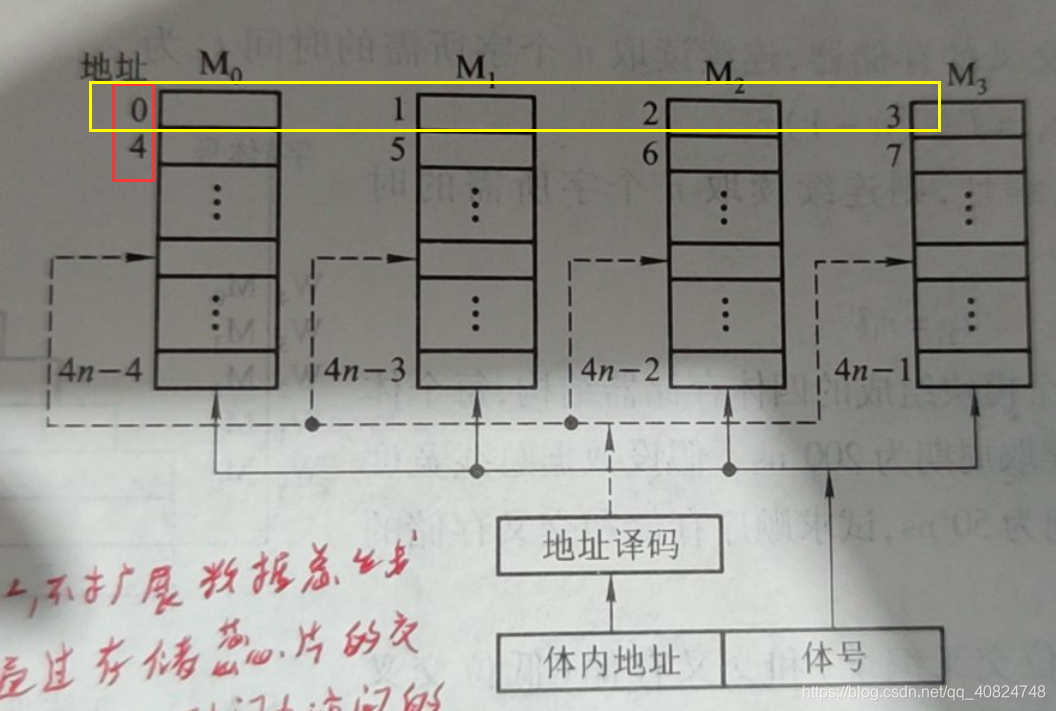

低位多体交叉:

多模块并行(局部性 原理)、相邻地址处于不同存储体中、每个存储体均需要地址寄存器、性能提升、扩充容量方便

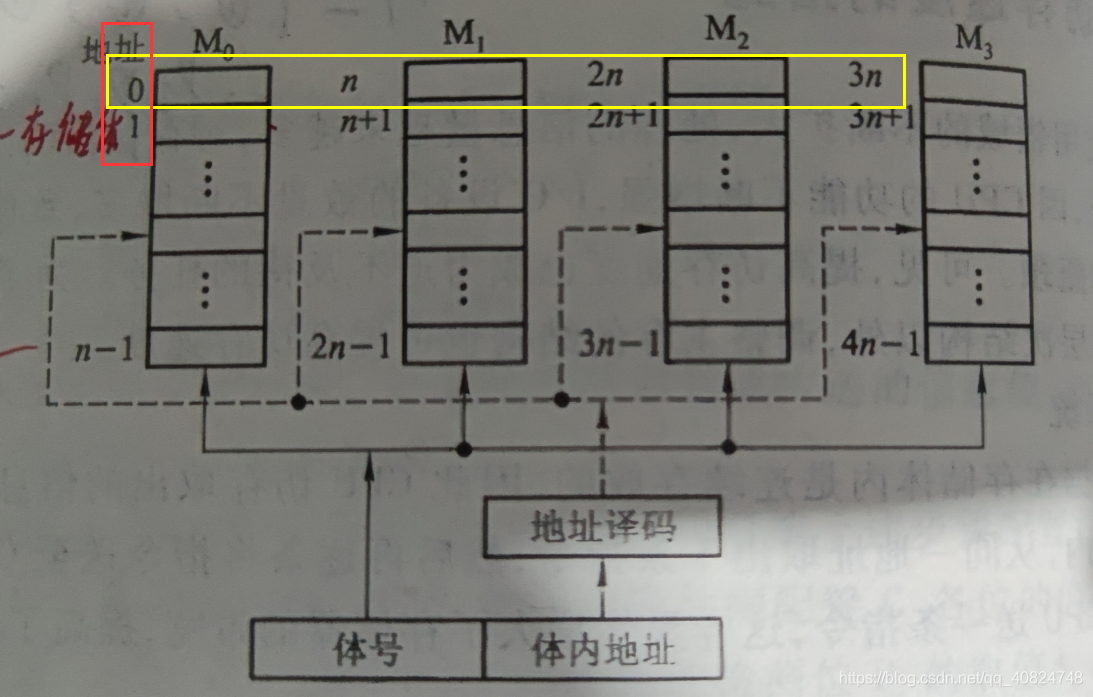

高位多体交叉:

多模块串行(局部性原理)、相邻地址的数据处于同一存储体、共一个地址寄存器、性能无提升、扩充容量方便

本文讨论了一个4体并行低位交叉存储器的特性,每个模块容量为64K×32位,存取周期200ns。由于低位交叉设计,CPU可以同时访问四个模块,实现数据的并行传输。这种设计利用了局部性原理,提高了存储系统的性能,尤其在连续访问时能显著提升数据吞吐量。

本文讨论了一个4体并行低位交叉存储器的特性,每个模块容量为64K×32位,存取周期200ns。由于低位交叉设计,CPU可以同时访问四个模块,实现数据的并行传输。这种设计利用了局部性原理,提高了存储系统的性能,尤其在连续访问时能显著提升数据吞吐量。

5万+

5万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?