存储器概述

存储器分类

存储器是计算机系统中的记忆设备,用来存放程序和数据。

构成存储器的存储介质,目前主要采用半导体器件和磁性材料。一个双稳态半导体电路或一个CMOS晶体管或磁性材料的存储元,均可以存储一位二进制代码。这个二进制代码位是存储器中最小的存储单元,称为存储位元。由若干存储位元组成一个存储单元,然后再由许多存储单元组成一个存储器。

根据存储材料的性能及使用方法不同,存储器有各种不同的分类方法。

- 存储介质: 半导体存储器,磁表面存储器;

- 存取方式: 随机存储器,顺序存储器;

- 存储内容可变性: 只读存储器(ROM),随机读写存储器(RAM);

- 信息易失性: 易失性存储器,非易失性存储器;

- 系统中的作用: 内部存储器、外部存储器;(主存储器、高速缓冲存储器、辅助存储器、控制存储器)

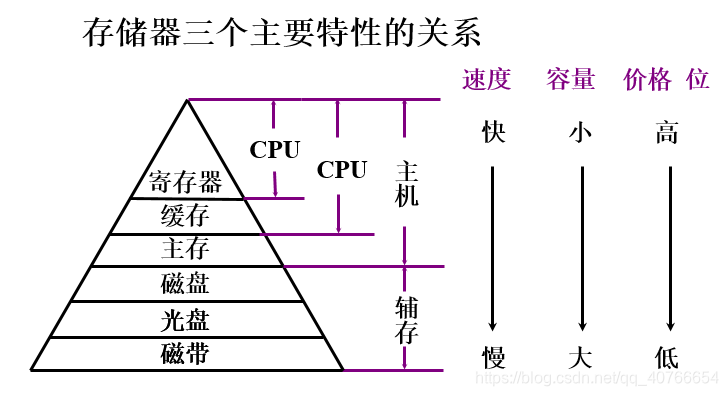

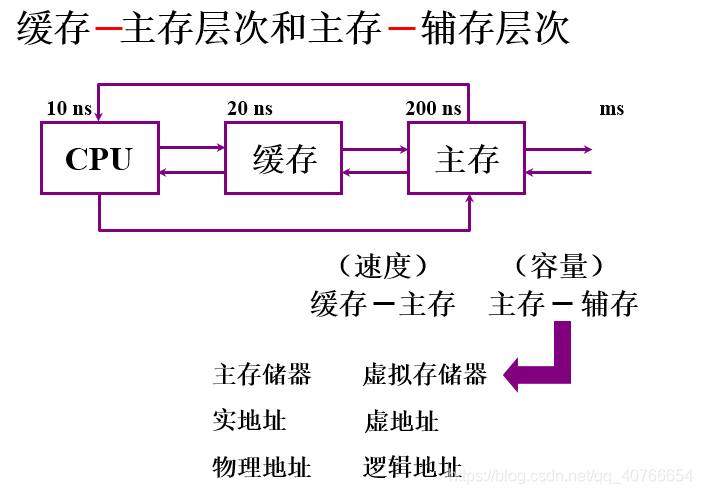

存储器的分级

CPU能直接访问的存储器称为内存储器,它包括cache和主存储器。CPU不能直接访问外存储器,外存储器的信息必须调入内存储器后才能为CPU进行处理。

主存储器的技术指标

字存储单元(Word): 存放一个机器字长的存储单元;

字节存储单元(Byte): 存放一个字节的单元;

存储容量: 存储器中可以容纳存储单元总数;

存取时间: 又称存储器访问时间,一次读操作命令发出到该操作完成,将数据读出到数据总线上所经历的时间;

存储周期: 指连续启动两次读操作所需间隔的最小时间;

存储器带宽: 单位时间里存储器所存取的信息量,通常以位/秒(b/s)或字节/秒(B/s)做度量单位。

SRAM存储器

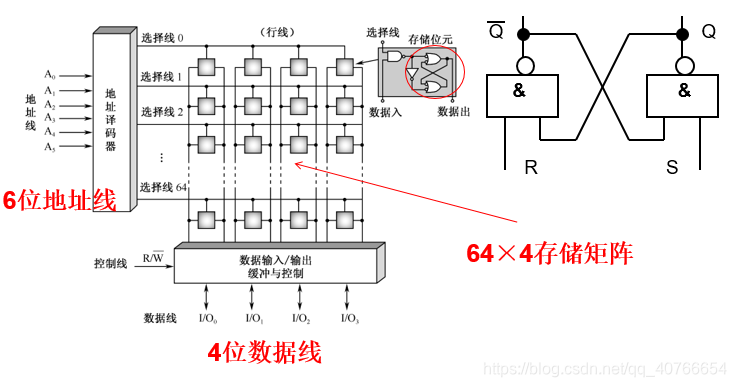

基本的静态存储元阵列

所有的SRAM的特征是用一个锁存器(触发器)作为存储元。只要直流供电电源一直加在这个记忆电路上,它就无限地保持记忆的1状态或0状态。如果电源断电,那么存储的数据(1或0)就会丢失。

任何一个SRAM,都有三组信号线与外部打交道:①地址线,上图中有6条即

A

0

A_0

A0、

A

1

A_1

A1、

A

2

A_2

A2、

A

3

A_3

A3、

A

4

A_4

A4、

A

5

A_5

A5,它指定了存储器的容量是

2

6

=

64

2^6=64

26=64个存储单元。②数据线,上图中有4条即

I

/

O

0

I/O_0

I/O0、

I

/

O

1

I/O_1

I/O1、

I

/

O

2

I/O_2

I/O2、

I

/

O

4

I/O_4

I/O4,它指定了存储器的字长是4位,因此存储位元的总数是64×4=256。③控制线,上图中

R

/

W

^

R/\widehat{W}

R/W

,它指定了对存储器进行读(

R

/

W

^

R/\widehat{W}

R/W

高电平),还是进行写(

R

/

W

^

R/\widehat{W}

R/W

低电平)。注意,读写操作不会同时发生。

地址译码器输出有64条选择线,我们称为行线,它的作用是打卡每个存储位元的输入与非门。当外部输入数据为1时,锁存器便记忆了1;当外部输入数据为0时,锁存器便记忆了0。

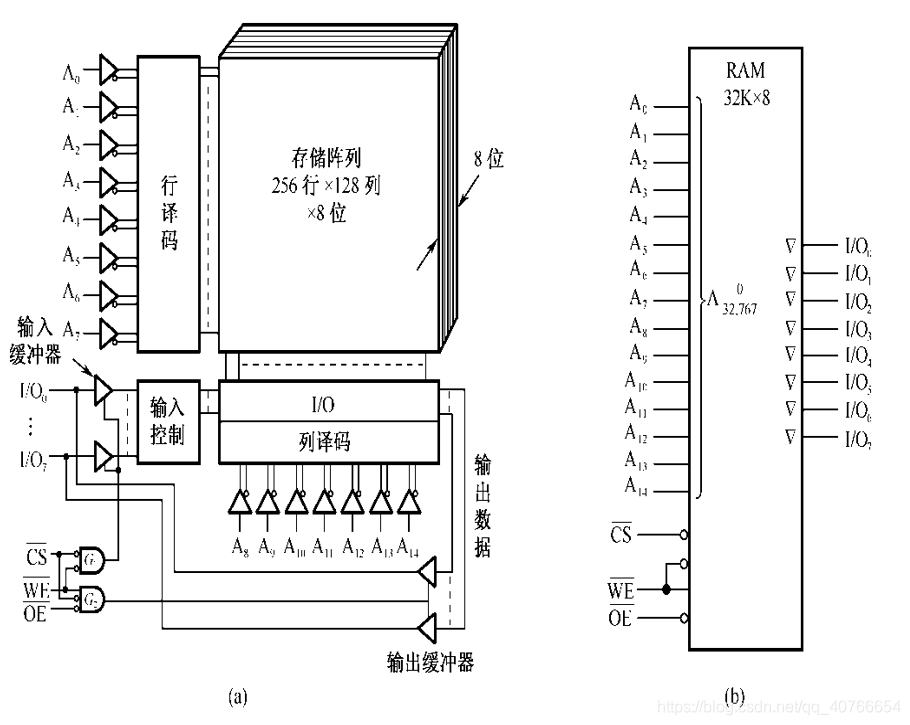

基本的SRAM逻辑结构

图(a)为结构图;图(b)为逻辑图。

图(a)表示存储容量为32K×8位的SRAM逻辑结构图。它的地址线共15条,其中x方向8条(

A

0

A_0

A0 ~

A

7

A_7

A7),经行译码输出256行,y方向7条(

A

8

A_8

A8 ~

A

14

A_{14}

A14),经列译码输出128列,存储阵列为三维结构,即256行×128列×8位。双向数据线有8条,即

I

/

O

0

I/O_0

I/O0 ~

I

/

O

7

I/O_7

I/O7。向SRAM写入时,8个输入缓冲器被打开,而8个输出缓冲器被关闭,因而8条I/O数据线上的数据写入到存储阵列中去。从SRAM读出时,8个数据缓冲器被打开,8个输入缓冲器被关闭,读出的数据送到8条I/O数据线上。

控制信号中

C

S

‾

\overline{CS}

CS是片选信号,

C

S

‾

\overline{CS}

CS有效时(低电平),门

G

1

G_1

G1、

G

2

G_2

G2均被打开。

O

E

‾

\overline{OE}

OE为读写使能信号,

O

E

‾

\overline{OE}

OE有效时(低电平),门

G

2

G_2

G2开启,当写命令

W

E

‾

\overline{WE}

WE=1时(高电平),门

G

1

G_1

G1关闭,存储器进行读操作。写操作时,

W

E

‾

\overline{WE}

WE=0,门

G

1

G_1

G1开启,门

G

2

G_2

G2关闭。注意,门

G

1

G_1

G1和

G

2

G_2

G2是互锁的,一个开启时另一个必定关闭,这样保证了读时不写,写时不读。

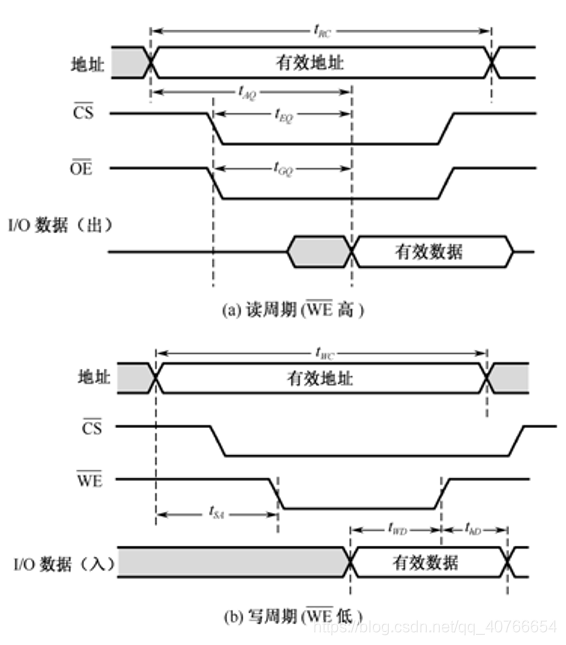

读/写周期波形图

在读周期中,地址线先有效,以便进行地址译码,选中存储单元。为了读出数据,片选信号

C

S

‾

\overline{CS}

CS和读出使能信号

O

E

‾

\overline{OE}

OE也必须有效(由高电平变为低电平)。从地址有效开始经

t

A

Q

t_{AQ}

tAQ(读出)时间,数据总线I/O上出现了有效的读出数据。之后

C

S

‾

\overline{CS}

CS、

O

E

‾

\overline{OE}

OE信号恢复高电平,

t

R

C

t_{RC}

tRC以后才允许地址总线发生改变。

t

R

C

t_{RC}

tRC时间我们叫读周期时间。

在写周期中,也是地址线先有效,接着片选信号

C

S

‾

\overline{CS}

CS有效,写命令

W

E

‾

\overline{WE}

WE有效(低电平),此时数据总线I/O上必须置写入数据,在

t

W

D

t_{WD}

tWD时间段将数据写入存储器。之后撤消写命令

W

E

‾

\overline{WE}

WE和

C

S

‾

\overline{CS}

CS。为了写入可靠,I/O线的写入数据要有维持时间

t

h

D

t_{hD}

thD,

C

S

‾

\overline{CS}

CS的维持时间也比读周期长。

t

W

C

t_{WC}

tWC时间叫做写周期时间。为了控制方便,一般取

t

R

C

t_{RC}

tRC=

t

W

C

t_{WC}

tWC,通常叫做存取周期。

DRAM存储器

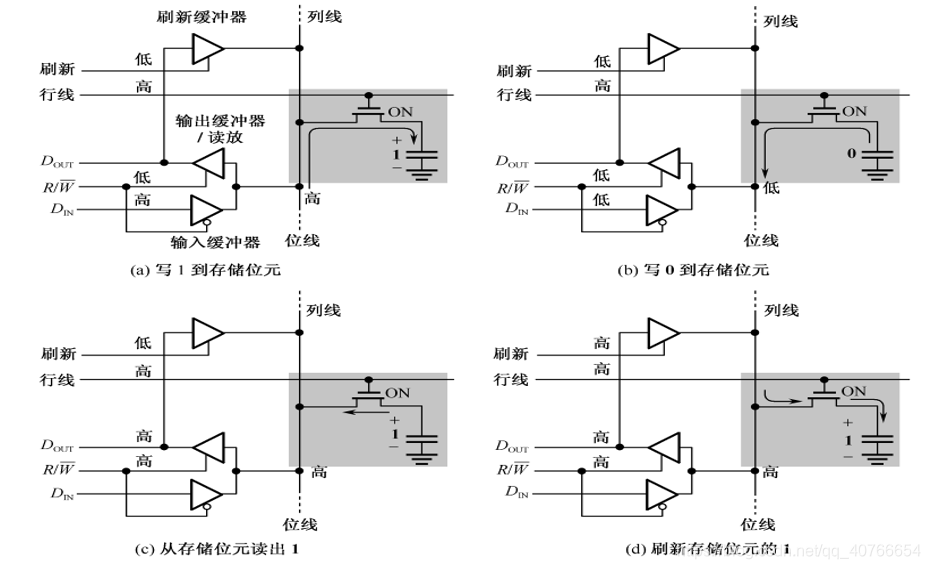

DRAM存储元的记忆原理

SRAM存储器的存储元是一个触发器,它具有两个稳定的状态。而DRAM存储器的存储元是由一个MOS晶体管和电容器组成的记忆电路。其中MOS管作为开关使用,而所存储的信息1或0则是由电容器上的电荷量来体现——当电容器充满电荷时,代表存储了1,当电容器放电没有电荷时,代表存储了0。

图(a)表示写1到存储元。此时输出缓冲器关闭、刷新缓冲器关闭,输入缓冲器打开(R/

W

‾

\overline{W}

W为低),输入数据

D

I

N

D_{IN}

DIN=1送到存储元位线上,而行选线为高,打开MOS管,于是位线上的高电平给电容器充电,表示存储了1。

图(b)表示写0到存储元。此时输出缓冲器和刷新缓冲器关闭,输入缓冲器打开,输入数据

D

I

N

D_{IN}

DIN=0送到存储元位线上;行选线为高,打开MOS管,于是电容上的电荷通过MOS管和位线放电,表示存储了0。

图©表示从存储元读出1。输入缓冲器和刷新缓冲器关闭,输出缓冲器/读放打开(R/

W

‾

\overline{W}

W为高)。行选线为高,打开MOS管,电容上所存储的1送到位线上,通过输出缓冲器/读出放大器发送到

D

O

U

T

D_{OUT}

DOUT,即

D

O

U

T

D_{OUT}

DOUT=1。

图(d)表示图©读出1后存储元重写1。此时输入缓冲器关闭,刷新缓冲器打开,输出缓冲器/读放打开,读出数据

D

O

U

T

D_{OUT}

DOUT=1又经刷新缓冲器送到位线上,再经MOS管写到电容上。

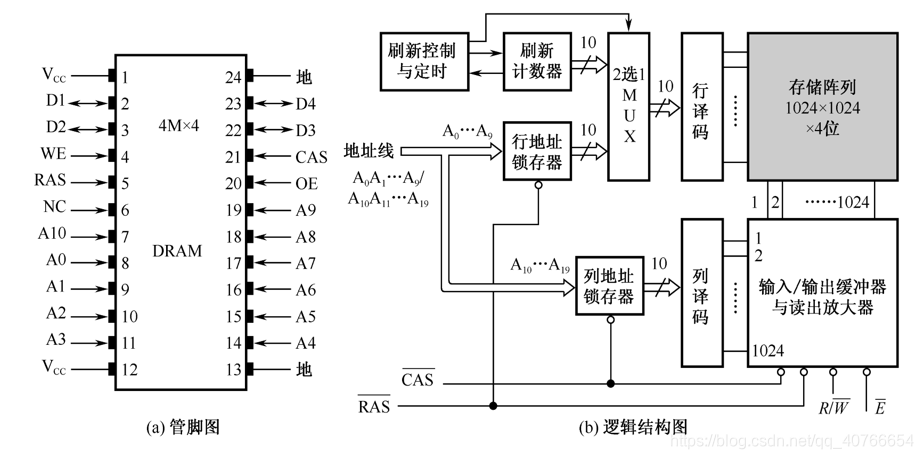

DRAM芯片的逻辑结构

与SRAM不同的是:

(1)增加了行地址锁存器和列地址锁存器。

(2)增加了刷新计数器和相应的控制电路。

读/写周期、刷新周期

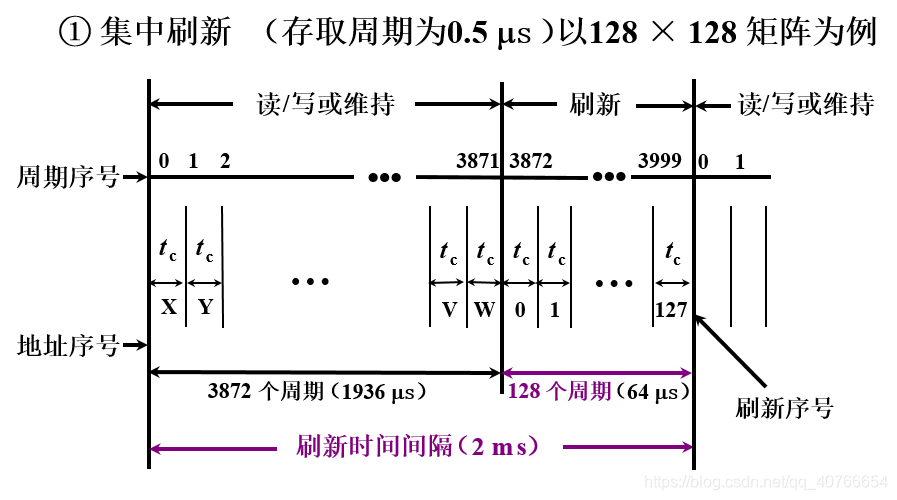

电容的衰减特性,需要每隔8ms到16ms(早期芯片2ms)进行一次充电叫刷新。

刷新方式有两种:

集中式刷新:所有行在一个刷新周期中都被刷新;

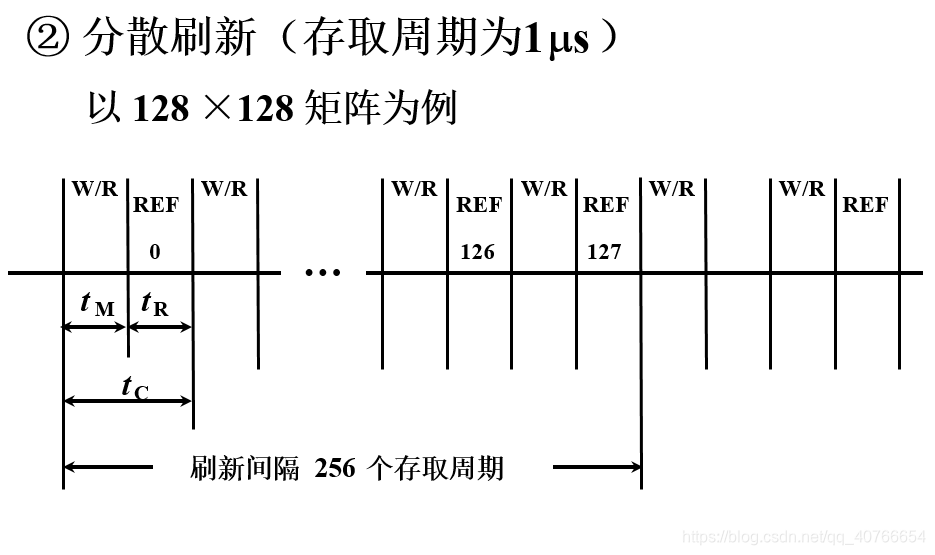

分散式刷新:每一行刷新插入到正读/写周期之中;

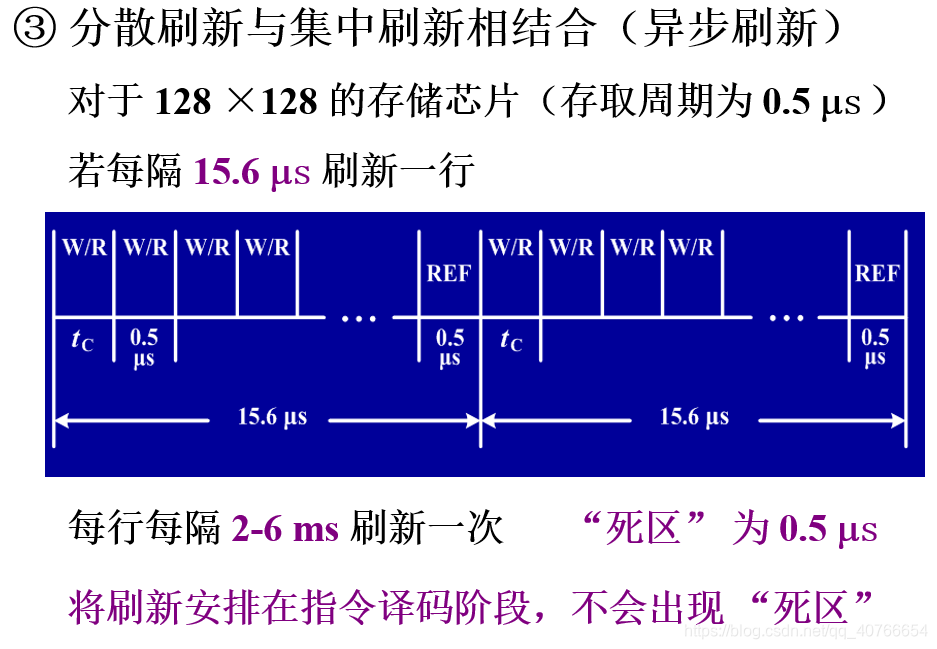

分布式刷新:集中式刷新与分散式刷新相结合的方式。

1700

1700

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?