FPGA系统性学习笔记连载_Day13【简易计时器实验】之【Xilinx Spartan-6实现】篇

本系列为FPGA系统性学习学员学习笔记整理分享,如有学习或者购买开发板意向,可加交流群联系群主。

连载《叁芯智能fpga设计与研发-第13天》 【简易计时器实验】之【Xilinx Spartan-6实现】

原创作者:紫枫术河 转载请联系群主授权,否则追究责任

本实验记录一个简易计时器,要求时间分为 时、分、秒,增加2个按键,1个为启动计时、1个为停止计时。

数码管的驱动原理,网上有太多的例程,这里我先不赘述,请自行上网查询,后续到了数码管专题篇再给大家出对应的文章

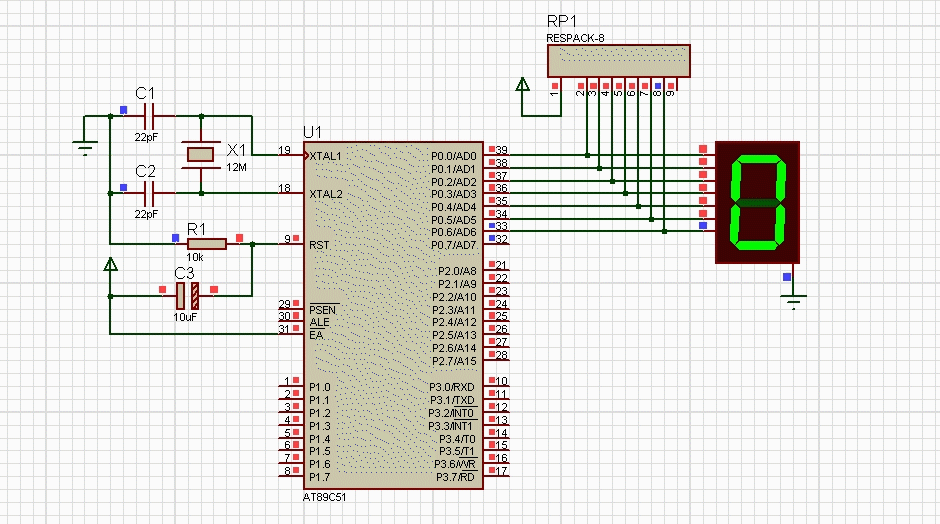

一、一位数码管显示原理

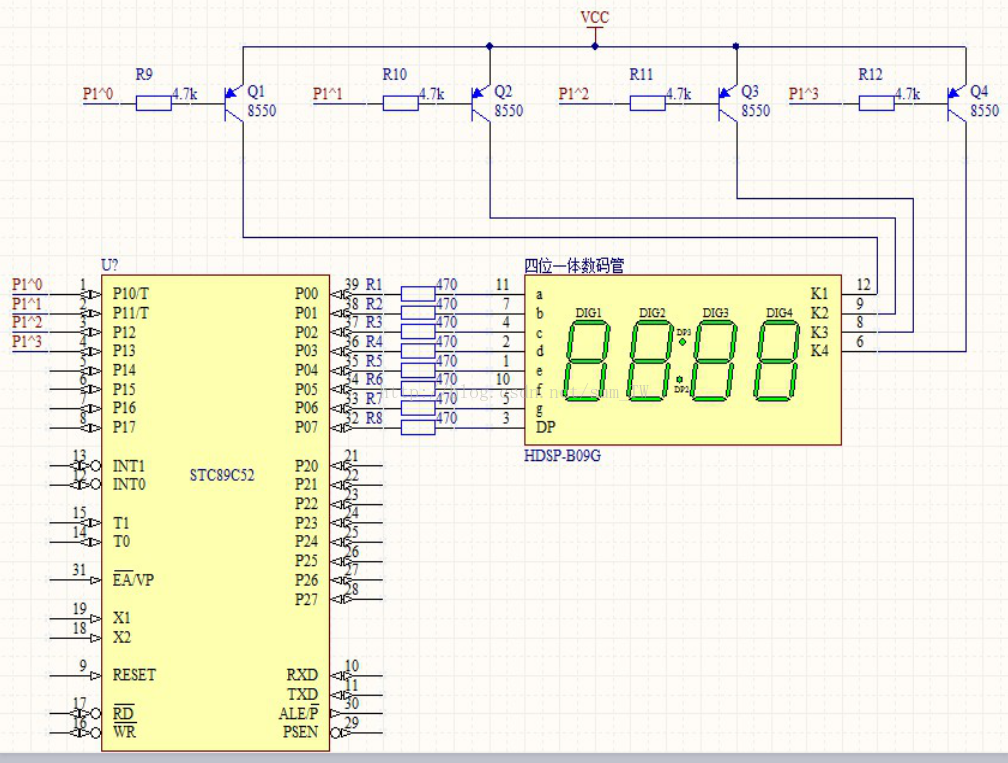

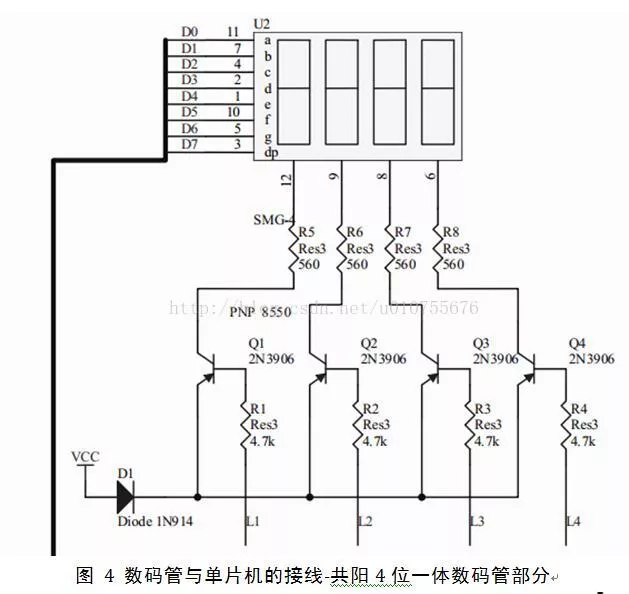

二、四位数码管显示原理

这篇博客介绍了使用Xilinx Spartan-6 FPGA设计和实现简易计时器的过程,包括数码管显示原理、设计框架及代码实现。作者通过digital_clock.v、clock.v和seven_tube_driver.v三个模块详细阐述了计时器的硬件和软件设计,并提供了硬件原理图和效果展示。

这篇博客介绍了使用Xilinx Spartan-6 FPGA设计和实现简易计时器的过程,包括数码管显示原理、设计框架及代码实现。作者通过digital_clock.v、clock.v和seven_tube_driver.v三个模块详细阐述了计时器的硬件和软件设计,并提供了硬件原理图和效果展示。

订阅专栏 解锁全文

订阅专栏 解锁全文

6745

6745

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?