第二章 Verilog Laguage

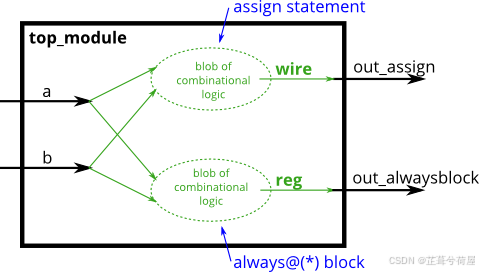

2.4.1 Always block (combitional)

// synthesis verilog_input_version verilog_2001

module top_module(

input a,

input b,

output wire out_assign,

output reg out_alwaysblock

);

assign out_assign = a & b;

always@(*)begin

out_alwaysblock = a & b;

end

endmodule

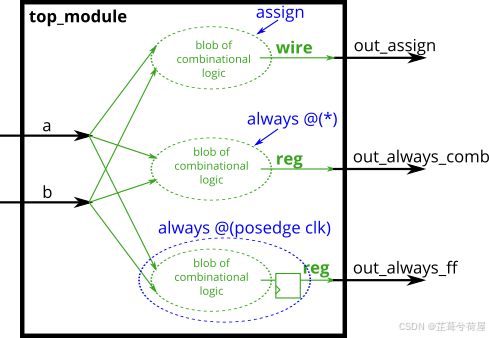

2.4.2 Always block (clock)

clock 块 输出生成了一个触发器,触发器是存储数据的基本单元,可以存储一位二进制代码;一/多个触发器可以组成1/多位寄存器,都是由时钟触发,锁存器由电平触发。

时钟信号:有低电平和高电平两个状态,是有固定周期的方波信号;

电平信号:只有高电平或者低电平一个状态;

// synthesis verilog_input_version verilog_2001

module top_module(

input clk,

input a,

input b,

output wire out_assign,

output reg out_always_comb,

output reg out_always_ff );

reg out;

assign out_assign = a ^ b;

always@(*)begin

out_always_comb = a ^ b;

end

always@(posedge clk)begin

out_always_ff <= a ^ b;

end

endmodule

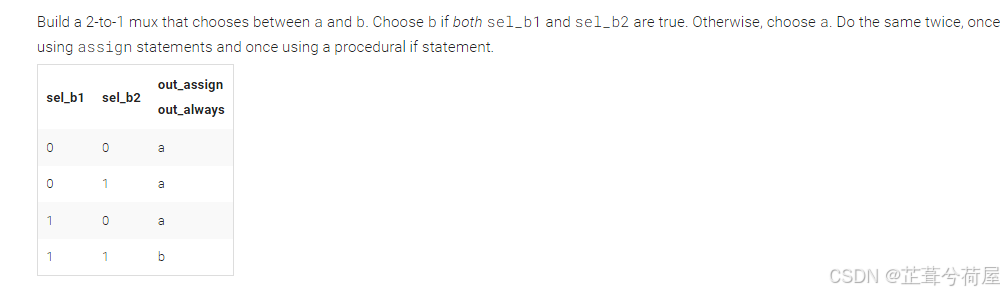

2.4.3 Always if

// synthesis verilog_input_version verilog_2001

module top_module(

input a,

input b,

input sel_b1,

input sel_b2,

output wire out_assign,

output reg out_always );

assign out_assign = (sel_b1 & sel_b2) ? b : a;

always@(*)

begin

if(!(sel_b1 & sel_b2))

out_always <= a;

else

out_always <= b;

end

endmodule

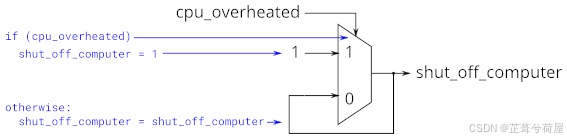

2.4.4 Always if 2

// synthesis verilog_input_version verilog_2001

module top_module (

input cpu_overheated,

output reg shut_off_computer,

input arrived,

input gas_tank_empty,

output reg keep_driving ); //

always @(*)

begin

if (cpu_overheated)

shut_off_computer = 1;

else

shut_off_computer = 0;

end

always @(*) begin

if (~arrived)

keep_driving = ~gas_tank_empty;

else

keep_driving = 0;

end

endmodule

2.4.5 Always case

// synthesis verilog_input_version verilog_2001

module top_module (

input [2:0] sel,

input [3:0] data0,

input [3:0] data1,

input [3:0] data2,

input [3:0] data3,

input [3:0] data4,

input [3:0] data5,

output reg [3:0] out );//

always@(*) begin // This is a combinational circuit

case(sel)

3'd0: out = data0;

3'd1: out = data1;

3'd2: out = data2;

3'd3: out = data3;

3'd4: out = data4;

3'd5: out = data5;

default :out = 1'b0;

endcase

end

endmodule

2.4.6 Priority encoder

4-2 编码器

// synthesis verilog_input_version verilog_2001

module top_module (

input [3:0] in,

output reg [1:0] pos );

always @(*)begin

case(1)

in[0] : pos = 2'd0;

in[1] : pos = 2'd1;

in[2] : pos = 2'd2;

in[3] : pos = 2'd3;

default : pos = 2'd0;

endcase

end

endmodule

// synthesis verilog_input_version verilog_2001

module top_module (

input [3:0] in,

output reg [1:0] pos );

always @(*)

begin

if(in[0])

pos = 2'd0;

else if(in[1])

pos = 2'd1;

else if(in[2])

pos = 2'd2;

else if(in[3])

pos = 2'd3;

else

pos = 2'd0;

end

endmodule

2.4.7 Priority encoder with casez

8-3 编码器

// synthesis verilog_input_version verilog_2001

module top_module (

input [7:0] in,

output reg [2:0] pos );

always @(*)

begin

casez(1)

in[0]: pos = 3'd0;

in[1]: pos = 3'd1;

in[2]: pos = 3'd2;

in[3]: pos = 3'd3;

in[4]: pos = 3'd4;

in[5]: pos = 3'd5;

in[6]: pos = 3'd6;

in[7]: pos = 3'd7;

default:pos = 3'd0;

endcase

end

endmodule

// synthesis verilog_input_version verilog_2001

module top_module (

input [7:0] in,

output reg [2:0] pos );

always @(*)

begin

casez(in[7:0])

8'bzzzzzzz1: pos = 3'd0;

8'bzzzzzz1z: pos = 3'd1;

8'bzzzzz1zz: pos = 3'd2;

8'bzzzz1zzz: pos = 3'd3;

8'bzzz1zzzz: pos = 3'd4;

8'bzz1zzzzz: pos = 3'd5;

8'bz1zzzzzz: pos = 3'd6;

8'b1zzzzzzz: pos = 3'd7;

default:pos = 3'd0;

endcase

end

endmodule

2.4.8 Always nolatches

// synthesis verilog_input_version verilog_2001

module top_module (

input [15:0] scancode,

output reg left,

output reg down,

output reg right,

output reg up );

always@(*)

begin

left = 1'b0; down = 1'b0; right = 1'b0; up = 1'b0;

case(scancode)

16'HE06B : left = 1'b1;

16'he072 : down = 1'b1;

16'he074 : right = 1'b1;

16'he075 : up = 1'b1;

endcase

end

endmodule

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?