s3c2440数据手册的第五章是关于内存控制器的,这篇文章就是关于它的理解和备忘(暂不涉及SDRAM的编程)。内存类芯片常见的基本就那么几大类。使用很频繁的,,后面可能专门对它们做一个总结。

-

2440的内存控制器基本情况:

——共有8个存储体(bank),每一个bank最大都达到一个128m,共1g了。除bank0(必须是只能是设置为访问外部是16/32位)外,其他存储体的可编程访问外部芯片的位的大小为8/16/32位。

——8个存储体中,前六个用于ROM、SRAM等(在它手册里,写成SROM, means ROM or SRAM type memory )。bank6/7用于ROM、SRAM、SDRAM等。

——7个bank开始地址是固定的,最后一个,地址和空间大小是灵活的

——前6个大小被确定,后2个大小可变,且必须一致(所以,最后一个的地址才是灵活的)

——所有内存组访问周期都可编程

——外部等待(extend wait)来延长总线通讯周期

——对于SDRAM,支持自刷新和关闭模式(所以,只对bank6/7有效) -

内存控制器/读写内存操作的流程

在对非SDRAM的内存芯片读写操作时,只需要按照2440的手册,将内存芯片和2440的引脚对应接好(特别注意是一片还是两片),然后直接编程,配置寄存器,主要就是注意16/32/8位选好、时序(时序就是,让2440的各个T> = 内存芯片的各个T)。内存控制器会自动读取或者写入的了。 -

几个问题:

Q:为什么每个bank最大寻址区域为128m?

A:外接的引脚地址线,是27根,即是2^27 = 128m

Q:看引脚图会发现data线是单独出来的,没有和gpxn口共用,而地址线只有一部分是和GPAn共用?

A:是。Data、addr这些引脚配置的模式都是high z模式的,只是2440包裹了这一层而已。但是而且这些引脚使用作为addr和data时,甚至还不用去设置GPXnCON和GPXnDATA之类的(GPXnDATA还好说,对于GPXnCON,是最不能理解的)

Q:nWAIT的n是什么意思

A:名称前面有n就是低电平有效。

Q:下面几个寄存器位的含义

A:nWBE为“写字节使能(write byte enable) ,nBE: 字节使能(byte enable),nCE:片选使能(nCE是内存类芯片的引脚名称,对于2440来说,是nGCSn),nWE:写使能 ,nOE:读使能 -

bank0的功能(比较特殊,挑出来说)

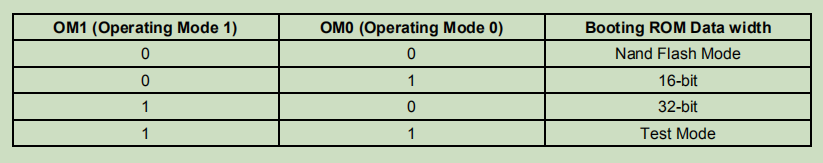

Bank0数据总线必须配置为16位和32位之一的宽度(事实上,配置寄存器时也只有32/16位可选)。由于可转换的ROM存储体(映射到ACN_0000)的总线宽度应 在第一次ROM访问之前确定,这将取决于在复位时OM的逻辑级别[1:0]。

-

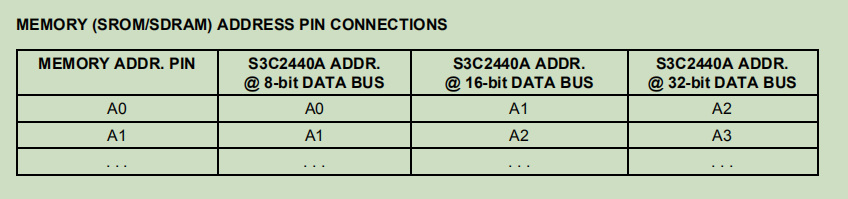

内存控制器设计好了的对应的接线引脚和内部的逻辑

对于外接的不同位数的rom之类的内存类芯片 (SROM/SDRAM),内存控制器设计好了,对应的接线引脚和内部的逻辑。本来自己韦东山关于这一块的视频只看到一点时,觉得如果mcu和内存类芯片如果地址线不是addr0对应addr0的话,会需要编程的人,自己一个一个去推移地址,很麻烦(虽然,这些地址线可能本来就不在一起的)。

但是,根据内存控制器的规则,对于cpu/编程人员,根本不用于设计/考虑外部引脚的不同接法,一贯编程即可。(像51这种,没有内存控制器,所以才需要编程人员兼顾这一点,而且和51不同的是,2440不需要编程时,自己delay去达到时序要求,而是直接配置寄存器来实现delay来达到时序要求。这就是高级mcu的不同了)

-

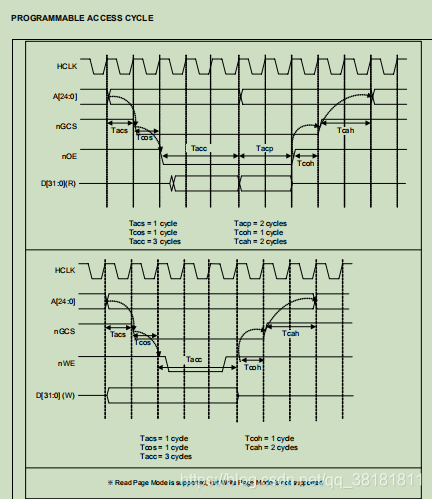

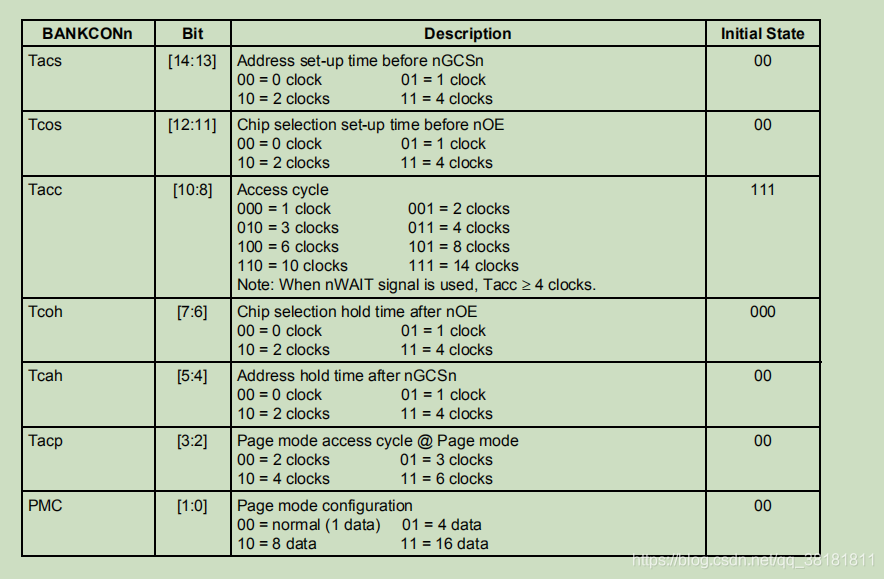

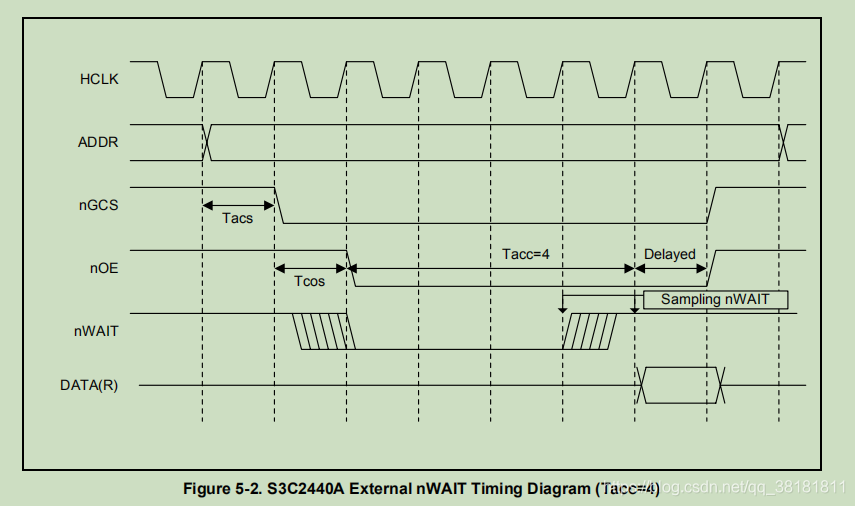

2440的时序图:

读内存是:发addr——发片选信号GCS——发读信号OE——开始得到data——结束OE——结束GCS——结束addr

写内存是:发addr——发片选信号GCS——发写信号WE—开始发送data——结束WE——结束GCS——结束addr

至于什么结束得到data和 结束发送data,不是很清楚。因为,不同的内存芯片的data如果需要有效地被读取和被写入,需要一个最低维持时间。显然,这个时间,不是2440能够控制的。所以,需要去具体使用的内存手册里,看。

事实上,2440的时序的,每个T都要大于内存芯片的T,就能够满足。还有的是,有时候可以设置addr和GCS同时发出之类的,即是没必要每个T都要存在,可以为0的。减少工作量(一般内存芯片有些T是不介意的)。

-

nXBREQ/nXBACK Pin Operation

这个暂时没接触过,先空着,待补。 -

关于burst

这个暂时没接触过,先空着,待补。 -

nBWE 和 nBE的区别和关系

看下面的BWSCON寄存器的位时,就会发现,STn这一位是这么说的,

=0时,不使用UB/LB,引脚为nBWE[3:0];

=1时,使用UB/LB,引脚为nBE[3:0]。(就是有4个引脚,nBWE[3:0]和nBE[3:0]共用了他们)

UB 、LB是指高位和低位。比如要外接1片16位的SRAM,16位所以需要使用UB 、LB,用nBE。而如果是1片8位的SRAM,则不需要使用UB 、LB,用nBWE。但是,如果将这个16位的SRAM,换成2片8位的SRAM,如果执行写操作,是对2片ROM同时进行的,这样,当执行写字节指令时可能会破坏另一芯片中的数据。 那怎么避免本来是传给SRAM1的数据同时也传给SRAM2呢?

这时就需要nBWE 。如果说nGCSn是针对大类的内存类芯片的片选(比如所有bank,都是同样的地址线,怎么确定传给哪个bank)。那么nBWE就是,在确定的那个bank内,如果有多个内存芯片进行数据位扩展,确定传给具体哪个芯片。

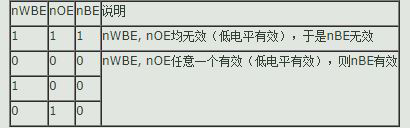

根据手册描述“nBE[3:0] is the ‘AND’ signal nWBE[3:0] and nOE”,即nBE是nWBE和nOE的“与”信号,这句话给了我们非常重要的启示,应该说深刻揭示出了nWBE, nBE之间的本质、内涵。(OE是读信号,可不是写信号)

首先看一下真值表:

注意到nWBE[3:0],nOE仅一根信号线。由此可见,nBE就是字节选通信号(读、写选通)。读的时候,多片均选通,写的时候,分片进行选通(当然,也要它有实际接线才行)。

可以参考:

http://blog.sina.com.cn/s/blog_3e8a48bf0100dd8o.html

从2440的手册Figure 5-4到5-9总结:

对于ROM,没有UB、LB引脚,所以接多片做数据位拓展时,nWE接nBWE;

对于SRAM,有UB、LB引脚。

是否芯片位数>=16时,是的话一定要用UB、LB引脚,所以一定要接nBE。

是否为多片芯片,是的话8位则使用nBWE;

是否为多片芯片,是的话>=16位则使用nBE。

(配置寄存器这一part,最好就是配合手册和电路图来配置)。

- 关于寄存器

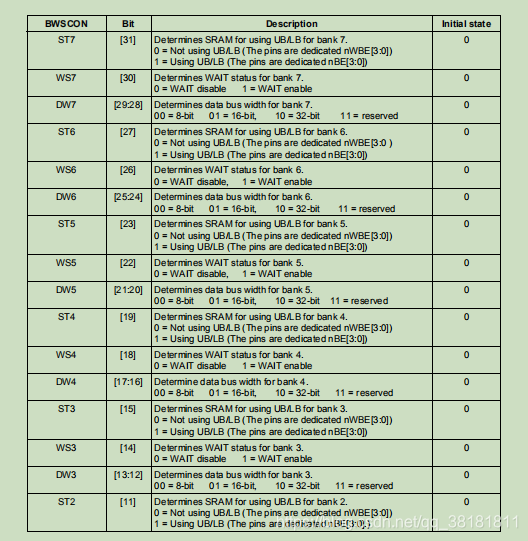

宽度和wait寄存器:BUS WIDTH & WAIT CONTROL REGISTER (BWSCON)

| Register | Address | R/W | Description | Reset Value |

| BWSCON | 0x48000000 | R/W | Bus width & wait status control register | 0x000000 |

具体的位:

注意:nBE[3:0]为AND信号nWBE[3:0]和nOE。(这一个,会详细的讲)

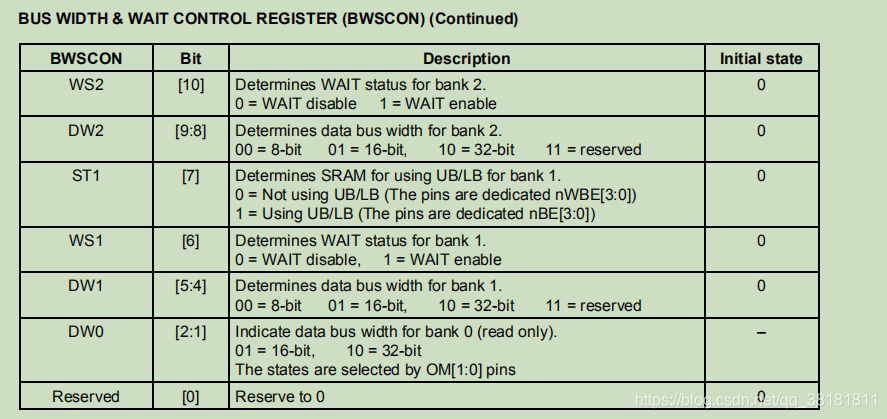

Bank控制寄存器:BANK CONTROL REGISTER (BANKCONN: NGCS0-NGCS5)

| Register | Address | R/W | Description | Reset Value |

| BANKCON0 | 0x48000004 | R/W | Bank 0 control register | 0x0700 |

| BANKCON1 | 0x48000008 | R/W | Bank 1 control register | 0x0700 |

| BANKCON2 | 0x4800000C | R/W | Bank 2 control register | 0x0700 |

| BANKCON3 | 0x48000010 | R/W | Bank 3 control register | 0x0700 |

| BANKCON4 | 0x48000014 | R/W | Bank 4 control register | 0x0700 |

| BANKCON5 | 0x48000018 | R/W | Bank 5 control register | 0x0700 |

具体的位:

(每个T终于出现了,顺便附两张时序图)

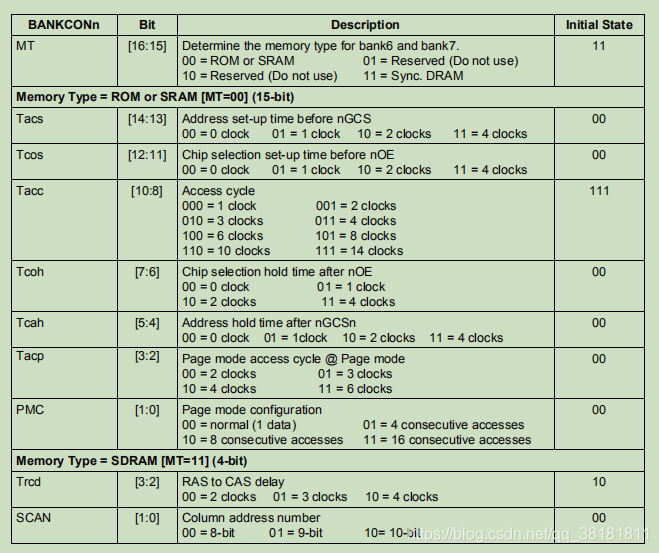

Bank6/7的bank控制寄存器BANK CONTROL REGISTER (BANKCONn: nGCS6-nGCS7)

| Register | Address | R/W | Description | Reset Value |

| BANKCON6 | 0x4800001C | R/W | Bank 6 control register | 0x18008 |

| BANKCON7 | 0x48000020 | R/W | Bank 7 control register | 0x18008 |

具体的位:

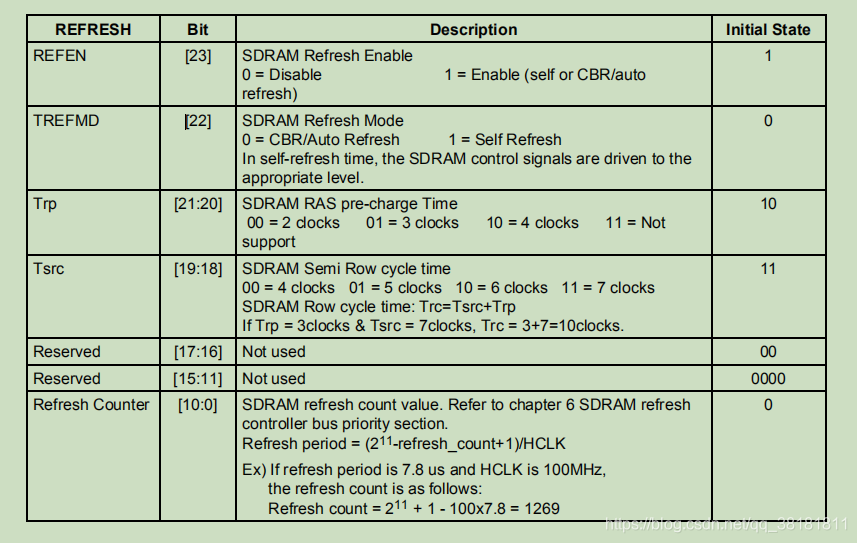

刷新寄存器:REFRESH CONTROL REGISTER

| Register | Address | R/W | Description | Reset Value |

| REFRESH | 0x48000024 | R/W | SDRAM refresh control register | 0xac0000 |

具体的位(专门用在SDRAM上的):

(刷新计数值。参见第6章刷新控制器总线优先级部分,等SDRAM做完后,可能补上。)

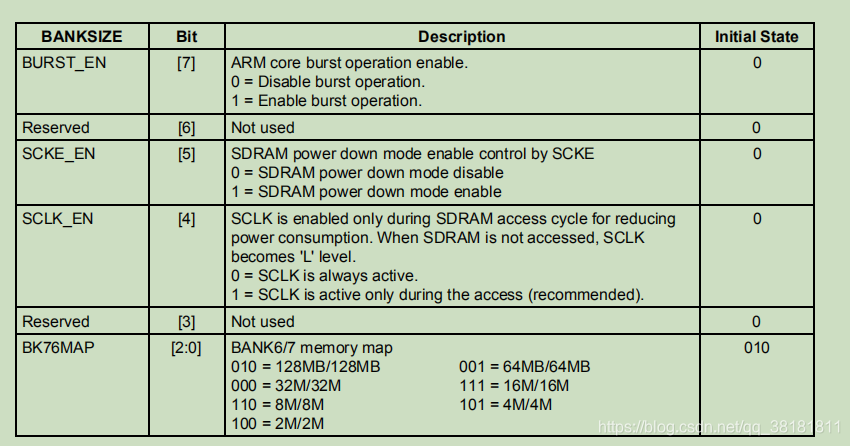

Bank6、7的size寄存器:BANKSIZE REGISTER

| Register | Address | R/W | Description | Reset Value |

| BANKSIZE | 0x48000028 | R/W | Flexible bank size register | 0x0 |

具体的位:

(最后一部分,也就说明了bank6、7的大小是必须统一的了)

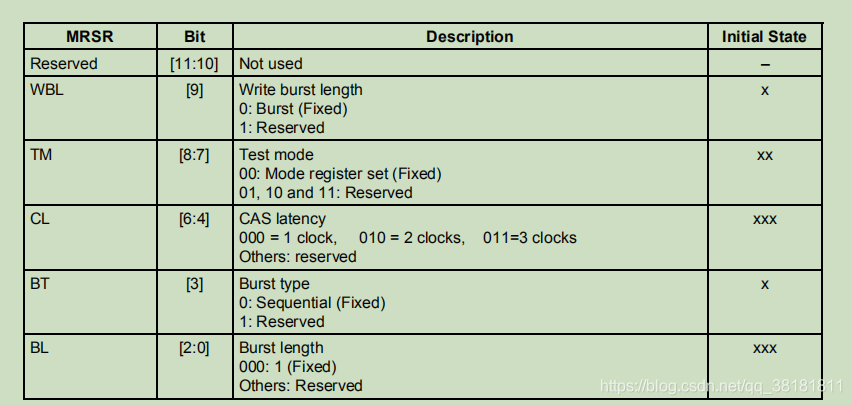

SDRAM模式寄存器:SDRAM MODE REGISTER SET REGISTER (MRSR)

(这个寄存器的用途不是特别懂,待查)

| Register | Address | R/W | Description | Reset Value |

| MRSRB6 | 0x4800002C | R/W | Mode register set register bank6 | xxx |

| MRSRB7 | 0x48000030 | R/W | Mode register set register bank7 | xxx |

具体的位:

注意:

当代码在SDRAM上运行时,MRSR寄存器不能被重新配置。(一般代码不会放在那里的)

在休眠模式下,sdram必须进入sdram自刷新模式。

本文介绍了S3C2440处理器的内存控制器,包括8个存储体的配置,特别是bank0的特殊性。内存控制器支持外部芯片的8/16/32位访问,并有自刷新和关闭模式功能。文章讨论了读写内存操作流程、时序配置、寄存器含义,并解答了关于bank寻址范围、数据线与地址线配置、时序图等相关问题。

本文介绍了S3C2440处理器的内存控制器,包括8个存储体的配置,特别是bank0的特殊性。内存控制器支持外部芯片的8/16/32位访问,并有自刷新和关闭模式功能。文章讨论了读写内存操作流程、时序配置、寄存器含义,并解答了关于bank寻址范围、数据线与地址线配置、时序图等相关问题。

976

976

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?