高速电路设计中除了要对信号完整性进行仿真与分析,电源完整性也占据着半壁江山,在正式学习仿真之前先来了解一下电源对信号的影响。

虽然电源完整性主要是讨论电源供给的稳定性问题,但是实际中“地”总是和电源密不可分的,通常把如何减少地平面的噪声也作为电源完整性的一部分进行研究。

一、电源噪声

造成电源不稳的原因一般有两个:

(1)器件高速开关状态下瞬态的交变电流过大;

(2)电流回路上存在的电感。

从变现形式上分类,又可以分为:

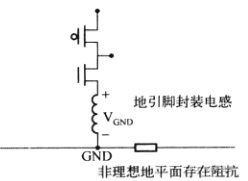

(1)同步开关噪声(SSN),地弹现象也可归于此类;

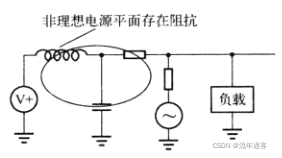

(2)非理想电源阻抗影响;

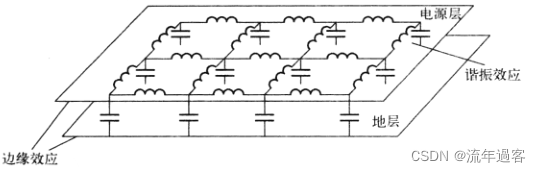

(3)谐振及边缘效应

对于理想电源来说,阻抗应该为0,但是实际上并非如此。

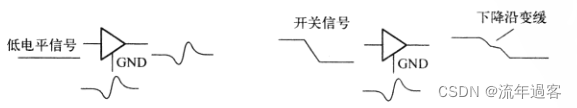

开关噪声对信号传输的影响较为显著,这是因为“地”线和平面间存在寄生电感,在开关电流的作用下,会造成一定的电压波动,此时相当于器件的参考地已经不是0电平了。

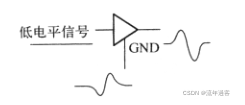

例如,在驱动端原本想要发送低电平,但是由于开关噪声引起的噪声波形,会导致信号下降沿变缓,如下图:

而在接收端同样受噪声影响,如下图所示:

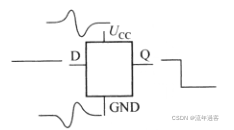

甚至在一些存储器件中,还可能因为电源和地噪声的影响造成数据意外翻转,如下图:

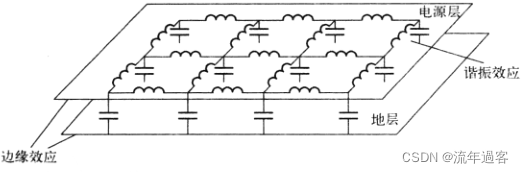

其实由下图可知,电源平面其实可以看作是由很多电感、电容构成的网络,或者可以叫做一个“共振腔”,在一定频率下这些电容电感会发生谐振,从而影响电源层阻抗。

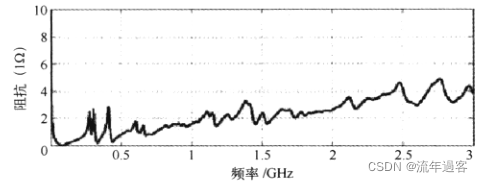

例如常见的FR4板材,假设电源层、地层的间距为4.5mil,随着频率的增加,电源阻抗变化如下:

除了谐振效应,电源、地平面的边缘效应同样不可忽视,这里说的边缘效应其实就是边缘反射和辐射,涉及到了EMI的范畴。但如果抑制了电源平面上的高频噪声,就可以很好地减轻边缘的电磁辐射,而常采用的方法就是添加去耦电容。

实际中边缘效应是不可避免的,所以在走线的时候要尽量远离赋铜区边缘,以避免EMI的干扰。

二、电源阻抗设计

电源噪声的产生很大程度上归结于非理想的电源分配系统,电源分配系统对电源稳定性有一定的要求,但实际中由于阻抗的存在,在瞬间电流流通时就会产生一定的电压降和电压波动。

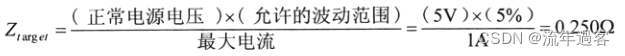

例如:一个5V电源,允许的电压噪声为5%,最大的瞬间电流为1A,那么设计的最大电源阻抗为:

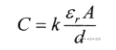

电源层和地层本身可以看作一个大的平板电容:

K:0.2249(d的单位为in)/ 0.884(d的单位为cm);

介电常数:FR4 材料在4.1-4.7;

A:敷铜平行部分的总面积;

d:电源、地之间的间距

电源、地之间耦合的电容值很小,但阻抗较大(一般有几欧姆),所以高速设计中仅依靠电源自身的耦合降低阻抗是不够的。

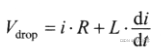

在设计电源阻抗时,需注意频率的影响,不仅需要计算直流阻抗(电阻),还需考虑较高频率时的交流阻抗(主要是电感),最高的频率将是时钟信号频率的两倍(主要是时钟的上升、下降沿,电源系统都会产生瞬时电流的变化)。通常可通过下面公式计算受阻抗影响的电源电压波动:

为此为降低电源的电阻和电感,可通过以下几种措施:

(1)使用电阻率低的材料,如铜;

(2)用较厚、较粗的电源线,并尽可能缩短长度;

(3)降低接触电阻;

(4)减小电源内阻;

(5)电源尽量靠近GND;

(6)合理使用去耦电容。

本文探讨了电源完整性在高速电路设计中的重要性,包括电源噪声产生的原因,如器件高速开关状态和电感的影响,以及同步开关噪声、非理想电源阻抗和谐振效应。电源平面的电感和边缘效应导致的电压波动和地弹现象会影响信号传输,甚至可能导致数据错误。解决方法包括使用低阻抗材料、优化电源线设计、减少接触电阻和合理布置去耦电容。电源阻抗设计时需考虑频率影响,确保电源分配系统的稳定性。

本文探讨了电源完整性在高速电路设计中的重要性,包括电源噪声产生的原因,如器件高速开关状态和电感的影响,以及同步开关噪声、非理想电源阻抗和谐振效应。电源平面的电感和边缘效应导致的电压波动和地弹现象会影响信号传输,甚至可能导致数据错误。解决方法包括使用低阻抗材料、优化电源线设计、减少接触电阻和合理布置去耦电容。电源阻抗设计时需考虑频率影响,确保电源分配系统的稳定性。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?