在上一章节我们用AD936X Evaluation Software 软件生成了寄存器配的脚本文件FDD,具体内容如下:由于配置内容太多,大部分进行了省略。从配置文件中我们可以查看每个寄存器应该配置的参数,但是并不能直接在FPGA工程中调用,需要对文件格式进行修改,改成function函数形式,可以在工程中直接调用。如果人工一行一行修改,基本不可能,太费事,因此需要找出配置文件的规律,依靠自己编写的程序直接自动转换成我们需要的函数形式。

脚本自动转换程序下载: 百度网盘 提取码:mww7

//************************************************************

// AD9361 R2 Auto Generated Initialization Script: This script was

// generated using the AD9361 Customer software Version 2.1.3

//************************************************************

// Profile: Custom

// REFCLK_IN: 40.000 MHz

RESET_FPGA

RESET_DUT

BlockWrite 2,6 // Set ADI FPGA SPI to 20Mhz

SPIWrite 3DF,01 // Required for proper operation

ReadPartNumber

SPIWrite 2A6,0E // Enable Master Bias

SPIWrite 2A8,0E // Set Bandgap Trim

REFCLK_Scale 40.000000,1,2 // Sets local variables in script engine, user can ignore

SPIWrite 292,08 // Set DCXO Coarse Tune[5:0]. Coarse and Fine nominal values used with eval system. Other nominal values may be needed in a customer system

SPIWrite 293,80 // Set DCXO Fine Tune [12:5]

SPIWrite 294,00 // Set DCXO Fine Tune [4:0]

SPIWrite 2AB,07 // Set RF PLL reflclk scale to REFCLK * 2

SPIWrite 2AC,FF // Set RF PLL reflclk scale to REFCLK * 2

SPIWrite 009,07 // Enable Clocks

WAIT 20 // waits 20 ms

//

//

//

//此处省略多行内容

//

//

//

SPIWrite 076,00

//************************************************************

// Setup RSSI and Power Measurement Duration Registers

//************************************************************

SPIWrite 150,0B // RSSI Measurement Duration 0, 1

SPIWrite 151,00 // RSSI Measurement Duration 2, 3

SPIWrite 152,FF // RSSI Weighted Multiplier 0

SPIWrite 153,00 // RSSI Weighted Multiplier 1

SPIWrite 154,00 // RSSI Weighted Multiplier 2

SPIWrite 155,00 // RSSI Weighted Multiplier 3

SPIWrite 156,00 // RSSI Delay

SPIWrite 157,00 // RSSI Wait

SPIWrite 158,0D // RSSI Mode Select

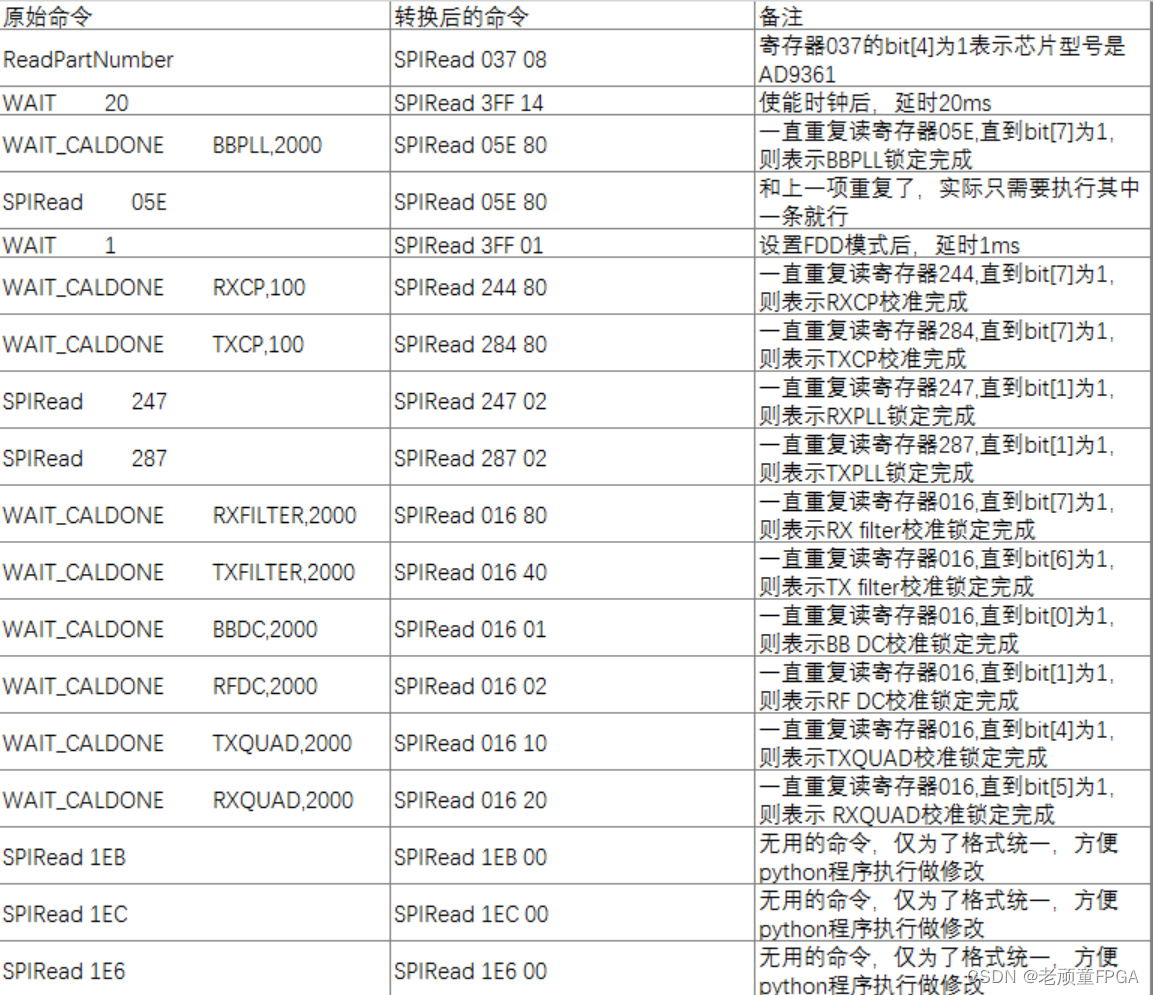

SPIWrite 15C,69 // Power Measurement Duration配置文件中包含三部分:读寄存器,写寄存器,延迟等待。SPIWrite表示写寄存器,下面表格中都读寄存器。

根据总结的规律,我编写了一个脚本自动转化软件,可以直接将AD936X Evaluation Software 软件生成的脚本转换成FPGA可以直接调用的Verilog的function函数,加快9361的配置过程。

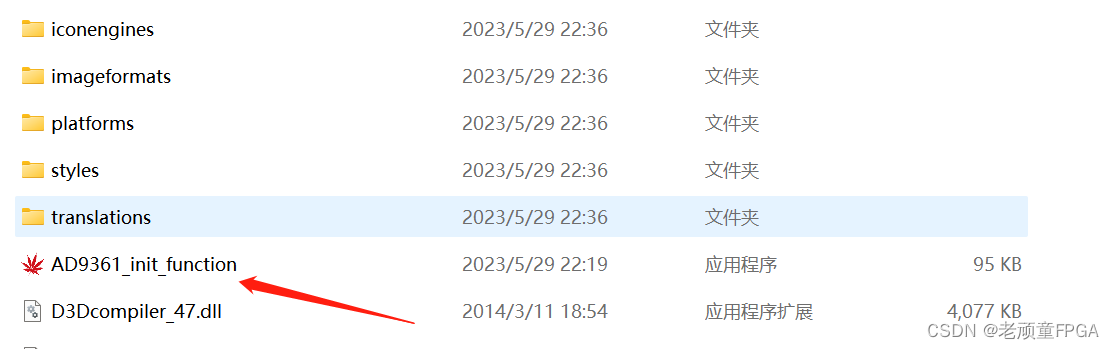

具体方法如下:双击程序图标

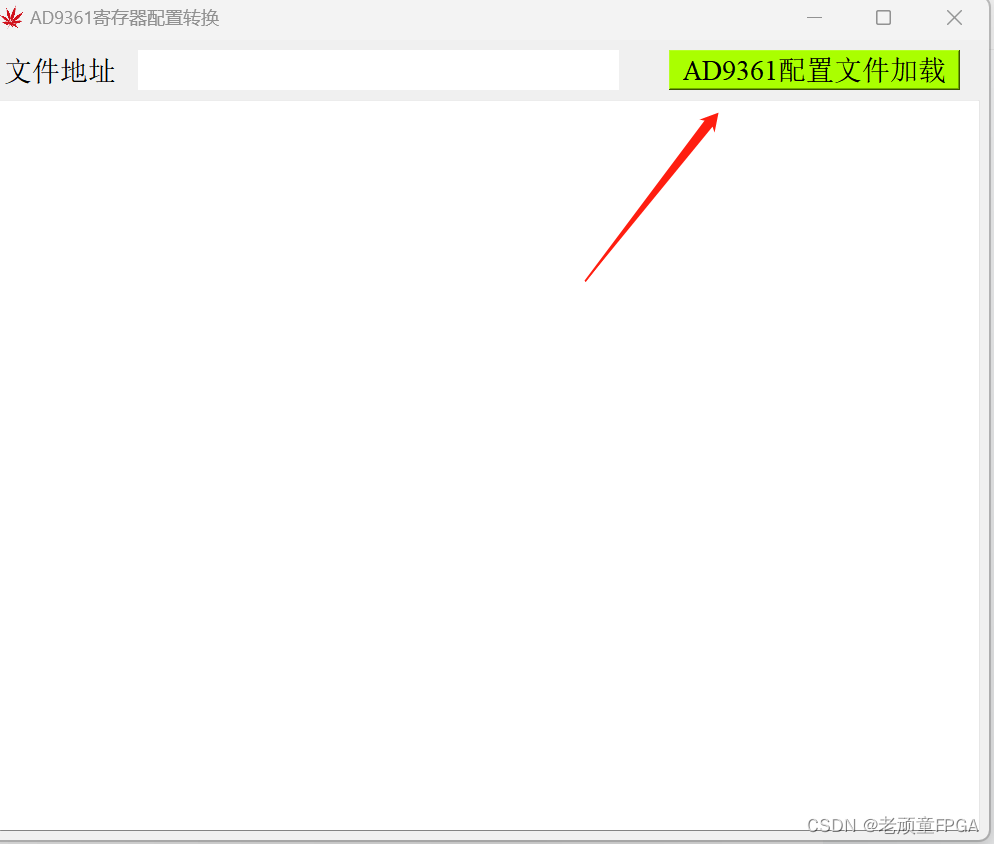

软件打开界面,点击绿色按钮。

选择AD936X Evaluation Software 软件生成的脚本文件,即可直接得到转换的Verilog的function函数。

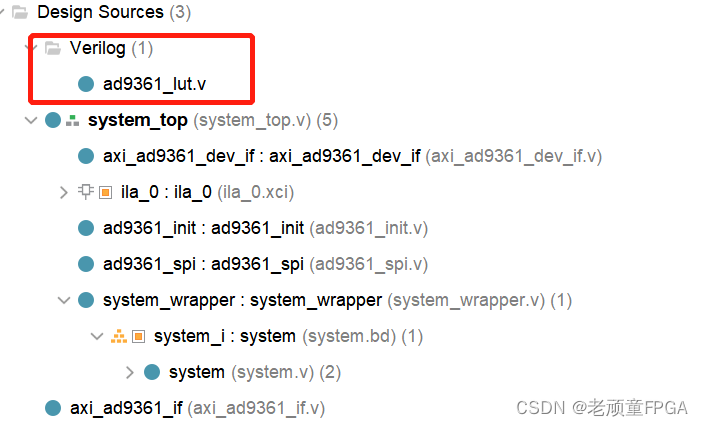

默认在电脑D盘生成ad9361_lut.v文件,可以将该文件直接调用到FPGA工程即可。

利用这个转换软件轻松得到我们需要的函数格式。下面就是编写SPI和寄存器的读写状态机文件,将转换的ad9361_lut.v文件中的寄存器值写到ad9361中去,请看博客下一章节。

文章介绍了一种方法,将AD936XEvaluationSoftware生成的配置脚本自动转换为FPGA可直接调用的Verilogfunction,以简化AD9361的配置过程。用户可以通过自编程序将原始脚本批量转换,并在D盘生成ad9361_lut.v文件,然后在FPGA工程中直接引用。

文章介绍了一种方法,将AD936XEvaluationSoftware生成的配置脚本自动转换为FPGA可直接调用的Verilogfunction,以简化AD9361的配置过程。用户可以通过自编程序将原始脚本批量转换,并在D盘生成ad9361_lut.v文件,然后在FPGA工程中直接引用。

2965

2965