测试数据部分

1产生数据:

由于fpga采用的是verilog硬件语言,只要ccd那里时序没问题,数据一定是可靠的。

当然了,如果硬件上有干扰另当别论,在实际测试时候,由于供电的纹波以及高频振荡,偶尔有干扰信号出现,

出现这个干扰,首先使用fpga自我校验,如果校验不成功,则fpga板子上led亮用来提示

2传输数据:

在测试的时候这里问题出现的是最少的,因为用了usb传输,usb有个机制是传输主动获取,在协议上没啥大问题,这里不具体展开

在实际测试的时候,只要usb能连接的上,线不松动,数据就没问题

3校验数据:

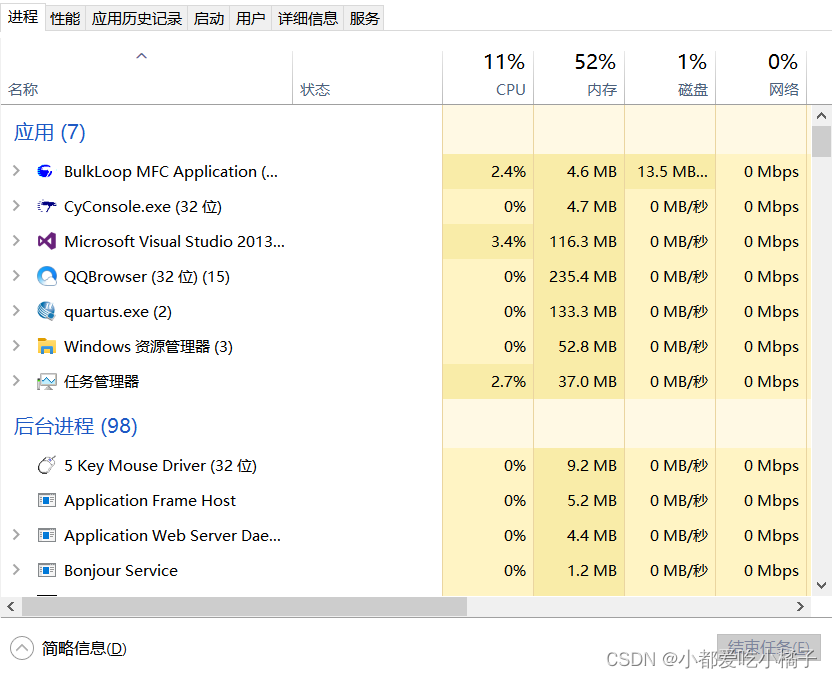

使用Visual Studio 2013 用c++的mfc写的调用usb保存传输过来的数据到硬盘,这里采用了内存拷贝技术,这篇文章暂时不展开这个技术。

在采用PyCharm Community Edition使用python脚本处理

这样好处是,python适合处理大数据,在上一章讲过一秒产生8M左右的数据,连续1分钟数据量是很可观的,虽然python效率不如

在c++中直接处理快,但是c++我考虑只是传输保存,这样要是加入处理动作,势必会影响效率,所以用python,还能方便出图像

实际在我的硬盘下保存数据为13.5M/S速度,已经相当不错了

本文介绍了一个利用FPGA进行数据产生与自我校验,并通过USB传输数据的测试系统。文中详细讨论了使用Python处理大规模数据的优势,包括高速数据保存与图像输出等。

本文介绍了一个利用FPGA进行数据产生与自我校验,并通过USB传输数据的测试系统。文中详细讨论了使用Python处理大规模数据的优势,包括高速数据保存与图像输出等。

643

643

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?