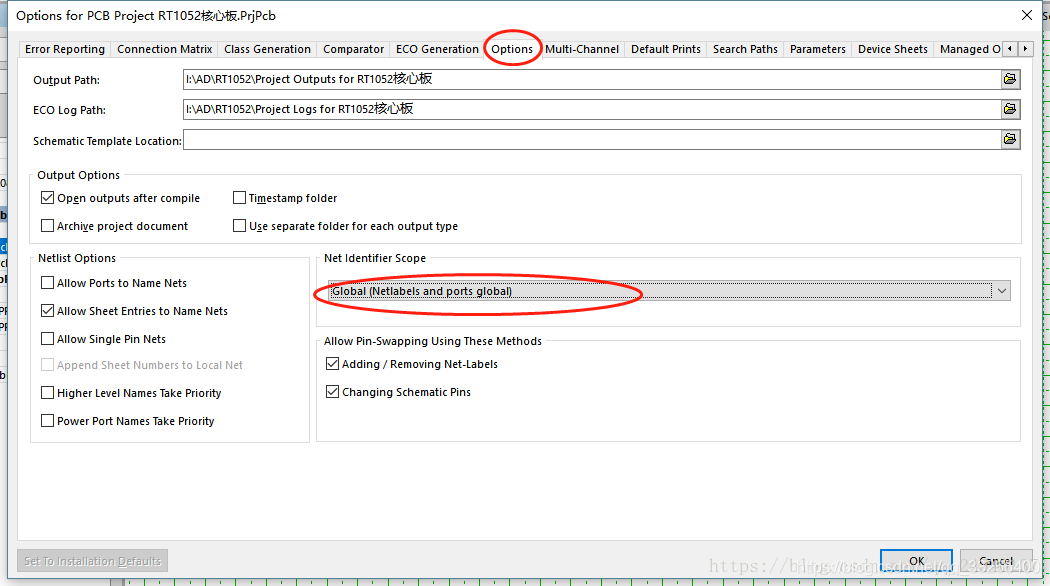

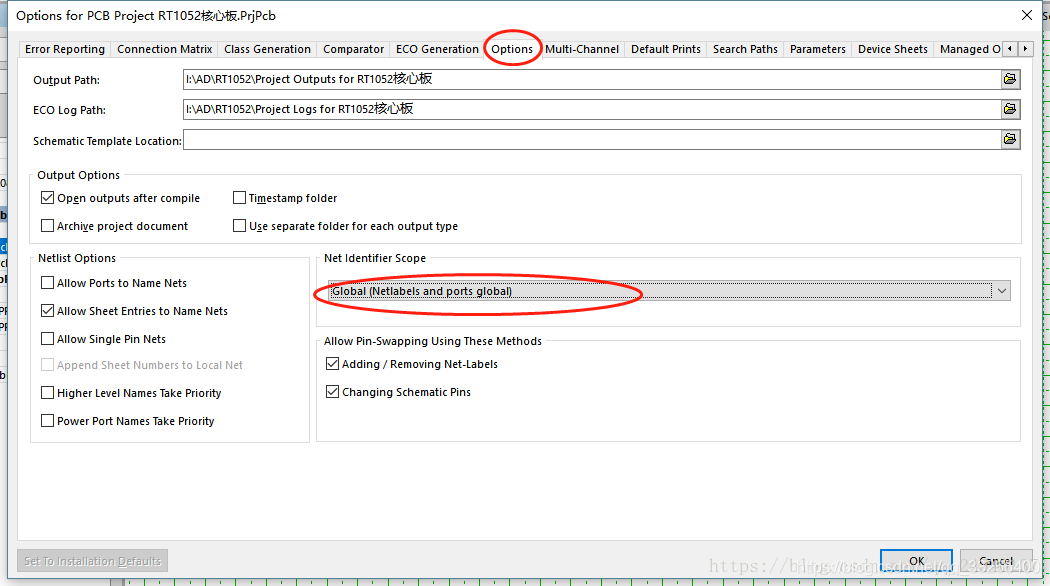

选择project--project options --options,按下图操作:

Altium designer 同一个工程中把多个原理图的相同网络编号关联起来

最新推荐文章于 2024-05-16 14:02:46 发布

选择project--project options --options,按下图操作:

1万+

1万+

1186

1186

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?