smic library中special cells

目录

1. endcap cell

2.tap cell

3.antenna fix cell

4.fillcap cell

5.fillcaptie cell

6.tiehi & tielo cell

7.spare cell

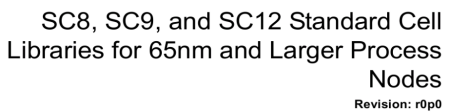

1. endcap cell

为了确保Nwell 是enclosed(封闭)的,加在core 每row的首尾,以及blockage macro的周围,保证Nwell 的完整性。

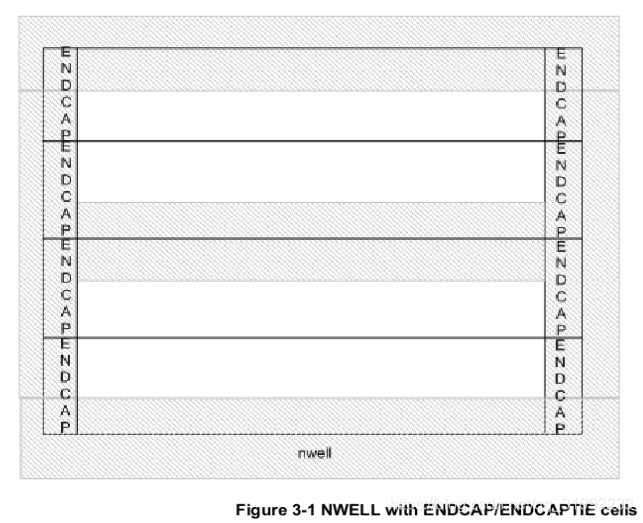

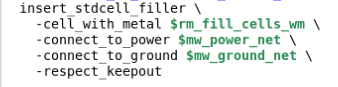

ICC 命令:

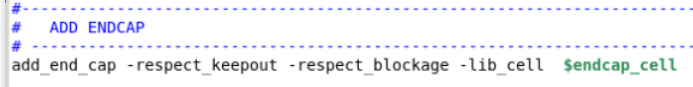

2.well tap cell

因为本library中stdcell里面没有直接将衬底接vss,N well 没有接VDD,所以为了避免闩锁效应需要在一定间隔插入 well tap cell。

如果不插入tap cell会导致闩锁效应(latch up cell ),其是由NMOS的有源区、P衬底、N阱、PMOS的有源区构成的n-p-n-p结构产生的,当其中一个三极管正偏时,就会构成正反馈形成闩锁。插入tie cell 会将PN结反偏。

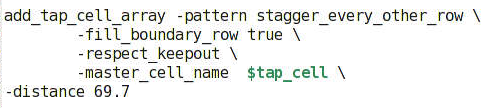

ICC命令:add_tap_cell_arry

- fill_boundary_row true 这个选项会打开边界处会自动补充cell以满足-distance的条件,

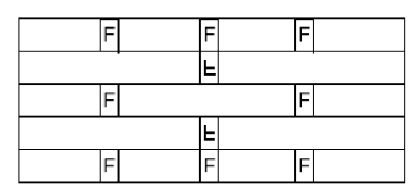

- pattern 一般会用stagger_every_other_row ,也就是下图所示,所以在design rule上给的tap out 数据会乘以2,也就是distance距离。

在这里要注意tap cell之间的间距

3.antenna fix cell

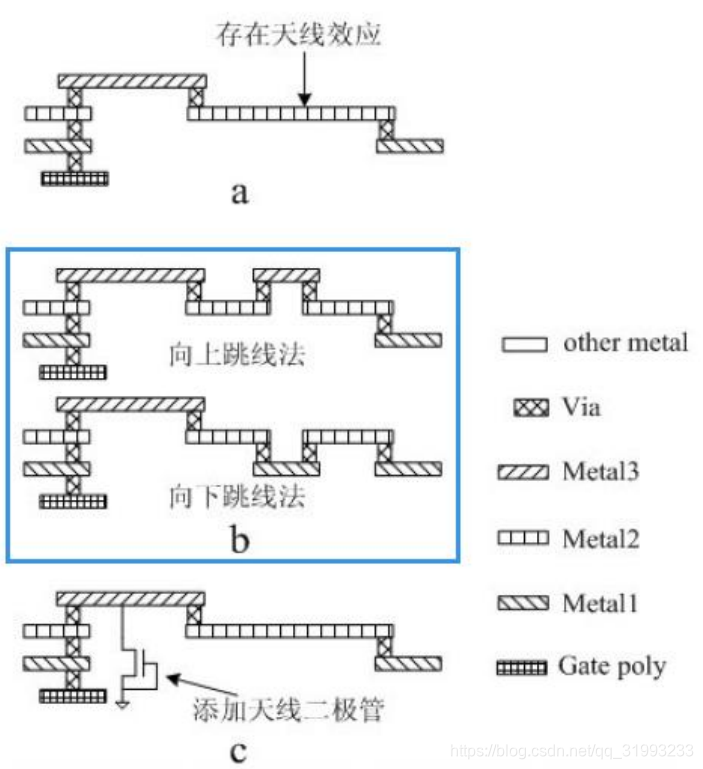

在芯片生产过程中,暴露的金属线或者多晶硅(polysilicon)等导体,就象是一根根天线,会收集电荷(如等离子刻蚀产生的带电粒子)导致电位升高。天线越长,收集的电荷也就越多,电压就越高。若这片导体碰巧只接了MOS 的栅,那么高电压就可能把薄栅氧化层击穿,使电路失效,这种现象我们称之为“天线效应”

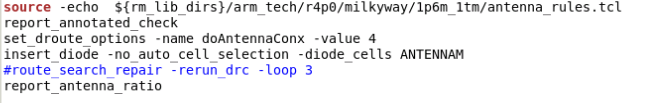

通常使用插入天线效应二极管的方法,在栅极加反偏二极管。

ICC 命令:

4.fillcap cell

做为std cell 的filler ,为了填充std cell之间的空隙。主要是把扩散层连接起来满足DRC规则和设计需求,并形成power rails,没有metal。

有两种结构:

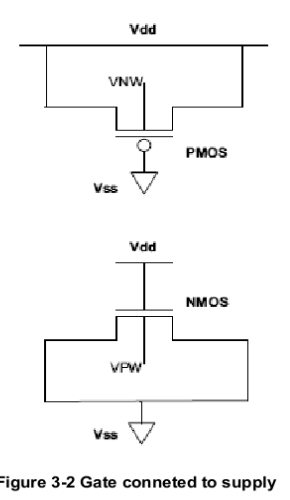

(1)gate connected to supply

cell 输入直接接VDD/VSS有去耦电容。

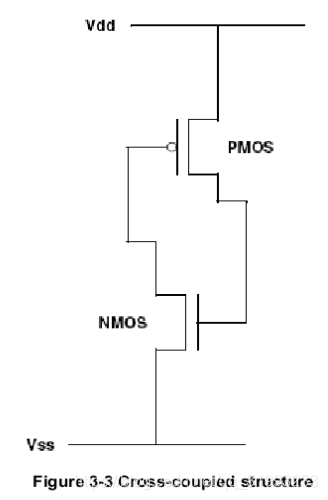

(2)cross_coupled structure

在VDD 和VSS之间有去耦电容,well是floating的,为了减少ground bounce(地弹)

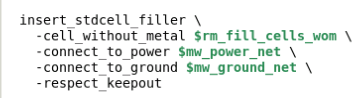

ICC命令:

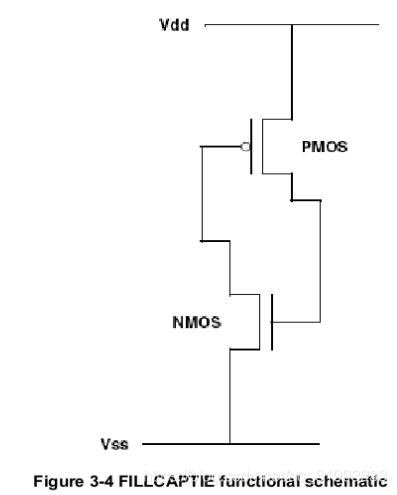

5.fillcaptie cell

做为std cell 的filler ,为了填充std cell之间的空隙。主要是把扩散层连接起来满足DRC规则和设计需求,并形成power rails。为了减少ground bounce,well被tie在power rail,cell 里面有metal。

ICC 命令:

注意插时候先插入有metal的filler,后插入without metal filler cell

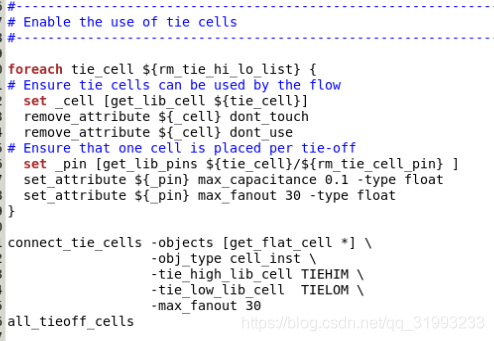

6.tiehi & tielo cell

将输入接1’b0/ 1’b1的cell输入接TIELO /TIEHI

ICC命令:

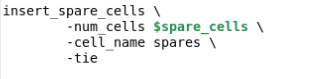

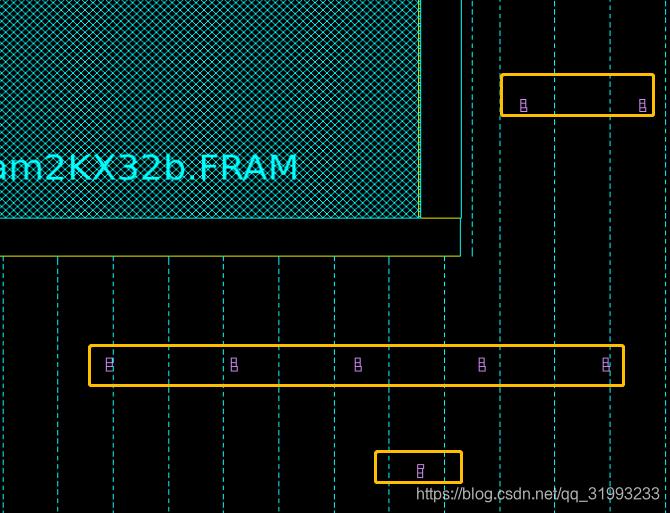

7.spare cell

spare cell是place之后插入的冗余的cell;post mask修改电路,添加逻辑使用spare cell; base 的mask不动,只修改metal layer的逻辑连接关系,实现逻辑修改。

ICC命令:

1362

1362

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?