- 用集成二进制译码器设计一组合逻辑电路,实现全减器功能

1.真值表和逻辑抽象

| A | B | Ci | D | CO |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 |

A为被减数;B为减数;Ci为来自低位的借位;D为差;CO为向高位的借位。

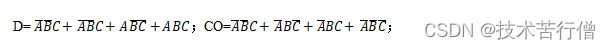

2.标准与或表达式

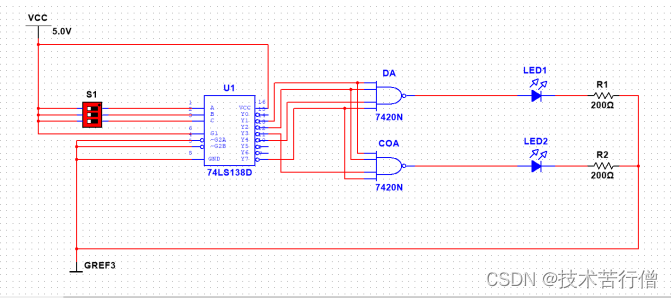

3.确定二进制译码器型号 并画出电路图

74LS138 和2 个与非门,vcc 5V、2个LED灯,若干链接线;

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?