摘 要

信号发生器是一种应用广泛的信号源,在多重领域可见其身影,当前阶段,信号合成对于DDS技术的依赖性较

强, DDS技术所设计出来的信号发生器所占据的市场份额相当大。对于集成DDS单芯片而言,其性能的优化离不开半

导体技术高速发展的助力,也正是在半导体技术的推动下,使其功能更加丰富。

本论文就是基于单片机实现DDS高频信号发生器的设计,其中的难点就是在通过功能需求寻找硬件并且通过功能

需求编写代码烧录至单片机中实现对应功能。本文首先会简述DDS高频信号发生器设计的基本原理并且阐述每个所用

电子元件的功能,并根据不同电子元件构成的子电路如温度传感器电路、液晶电路、按键电路等及总体功能介绍,

最后实现DDS高频信号发生器的设计。

关键词:STC89C51;DDS高频信号发生器;LCD1602

1 引言

1.1 研究的背景意义

信号发生器又称为波形发生器,是应用比较广泛的信号源,很多系统对于信号发生器的依赖性较强,主要为自动

控制系统、自动测量系统、无线电通信系统等等。反思传统信号发生器,模拟电路作为其基本构成单元。此类信号

发生器将电容、电阻、同轴线等作为其振荡回路,从而产生正弦波形。想要完成频率变动的目标,需要发挥机械对

可变元件的驱动作用。但是此类模拟信号发生器应用于信号输出时,所输出的参数的精准性不高,再加上体积大、

能耗高显然不受行业青睐。而对于通过数字电路所构成的信号发生器而言,性能相对理想,但无奈体积依然庞大,

价格也高,所以也不能广泛推广使用。早期,信号发生器主要扮演目标控制系统调试需要的信号源的模拟者角色。

模拟工作的顺利推进离不开场效应管等纯硬件的助力,但是波峰会失真,整体效果不佳。结合波形发生器的设计方

案,可进一步细分为硬件设计法、软件设计法、软硬件结合设计法。其中,硬件设计法即纯硬件设计法的功能非常

简单,波形改变的目标难以达成,同时控制活动也无法灵活进行,毫无智能性可言。而软件设计法开展起来并不复

杂,可灵活改变程序、优化功能,但是对比硬件设计法,无论是波形精度还是响应速度都不占优势。软硬件结合波

形发生器设计方法兼顾了软件设计法以及硬件设计法的优势,性能佳、控制灵活、智能化水平高[2]。

1.2 相关的研究

信号合成信号发生器其实是一种测量工具,在20年代随着电子设备的问世,信号合成信号发生器也随之进入到

人们的视线[3]。1932年,英国科研界聚焦新型无线电接收器设备的研究工作。此类无线电接收器的构成相对简单,

即本地振荡器、混频器、音频放大器。针对输入信号、本地振荡器而言,如果两者所处的相位、频率混合保持一致

时,那么表示输出时依托被调制载波准确音频。起初的测试成效非常乐观[4]。但渐渐的意识到,工作固定时间后,

同步接收工作受到本振频率漂移的影响,开展起来困难重重。PLL进化的开端即反馈电路。随后,借鉴1932年法国科

研者所著的论文,英国科研者完成了此类反馈系统的开发工作,至此,锁相频率合成技术迎来了发展新机遇。[5]

1971年,DDS技术由tierhey提出,随后LJK进一步就DDS技术展开深入、细致、全面的剖析,一类速度更快,功

耗更低的DDS结构正式与世人见面。此后,人们对于DDS的改造活动非常热衷,仅仅用了三十余年的时间,直接数字

频率合成技术的稳定性、成熟度都变得非常可观。时至今日,直接数字频率合成技术在商业型号发生器中依然有着

广泛运用。伴随着科技力量的进一步增强,通信技术、雷达技术也在迎头前进,尤其是六零年代,信号发生器发展

速度惊人,通过不断发展衍生出多种新型型号发生器,例如合成型号发生器、函数发生器、程控型号发生器等等。

这一系列型号发生器的性能的优化水平不断提升,当然信号发生器的结构更简化、功能更全面。

随着计算机科学的发展,计算机是一种高速运行计算的电子计算机器,可以进行数值计算,也可以进行逻辑计

算,通过二进制0、1代码可以几乎完成计算机的所有功能,计算普遍的特点就是有储存功能使得计算机的功能变得

更加强大,是能够按照程序代码完成对应功能,自动化高效完成对数据处理的现代智能电子设备。[8-10]

1.3 研究的主要内容及步骤

本文主要研究的是对DDS信号发生器的设计,利用STC89C51单片机、AD9833模块、LCD1602显示屏完成不同信号

波形产生的功能。数字信号可随意改变的波形发生器,依托AD9833以及51单片机完成设计,该设备可产生任意信号波形,同时可结合具体需要完成波形频率、幅度等的改变。与此同时,为了保障具体操作控制工作高效展开,可将

按键以及液晶显示屏增加到单片机上,修改后,波形也会随着变化,信号波形参数的显示离不开LCD的助力。显然,

该设计优势突出,主要表现为简单的电路结构、完善的系统功能、更好的契合具体需求。

第1章:概述了目标系统设计的背景及意义,对信号发生器、单片机、系统的发展历程总结。

第2章:介绍了信号发生器的设计方案和原理,根据各元件的功能确定元件选择,分析了DDS信号发生器的设计

要求和使用元件的原因。

第3章:主要介绍了各个模块的功能和设计原理图,分析了各个模块与单片机的关系,并提供了必要的硬件清

单,以帮助改进后续工作。

第4章:围绕软件设计工作进行,总结了与软件设计关联的基础内容,给出了基础流程示意图,详细介绍了主、

子程序。

最后,总结全文,总结文章涉及到的理论,详细说明了设计环节遇到的问题。

2总体设计

2.1总体设计目标

(1)可通过按键实现频率设定输出;

(2)针对0-10M波形,输入目标可借助按键实现,显示目标可通过LCD实现;

(3)针对输出频率值、波形、幅值等指标,想要实时显示,需要1602液晶显示屏的助力。

(4)针对AD9833模块,在转接座的配合下,支持更换。

(5)可以输出正弦波、方波和三角波三种波形;

2.2模块方案的选择

2.2.1单片机的选择

STC89C51具有加密性强,超强抗干扰等功能,能够保证数据的真实性和准确性,并且是一个同时具备低功耗,

超低价和高可靠的单片机。这一单片机供电电压可选择范围广,为3.8-5.5V,引脚有40个,运行速度较快,片内资源

丰富。[12-15]。STC89C51的结构如图2-1所示。

图2-1 STC89C51结构框图

2.2.2显示模块选择

该系统的显示器模块只需波形的相关数据。LCD1602 其作为一种字符型的液晶显示器,具备低功耗和显示清晰

的优点,此外液晶显示也是其一大特色。作为点阵型液晶模块,支持两行字符同时显示,同时数字、字母等均可显

示出来,该液晶屏控制简单,显示清晰,用来显示字母和数字会更加方便,可以很快速方便地连接到单片机

LCD1602 在可实现显示频率数值的前提下,是液晶显示器中成本最小的。[16]关于 LCD1602 的实物图如图2-2所

示。

图2-2 LCD1602实物图

2.2.3 频率合成模块的选择

针对频率合成,常用的实现方式有直接模拟合成、锁相环综合、直接数字合成。首先直接模拟合成在精准性高

的时钟源以及单个参考频率或者多个参考频率的配合下,依托分频、倍频、混频等技术手段来达成频率产生的目

的。该实现方式拥有较快的变频速度,缺点是硬件体积大,功率损耗高;锁相环综合法在锁相环技术的助力下,顺

利实现倍频、分频的目标。锁相环综合是现阶段结构简单的全集成电路。但是该方法也有应用缺陷,一旦频率分辨

率高出一定范围后,那么系统的转换效率就得不到保障。DDS(直接数字频率合成)法高效快速,补足了锁相环技术

的弊端,转换速度快、频率稳定性强、精准性高、集成简单、分辨力理想。

2.2.4 按键输入模块选择

该设计目标的实现,前提是做好键盘模块的设计工作。因为正弦波以及方波需要的输出频率仅需要借助键盘完

成输入。其中单独的矩阵按键应用作为广泛,此类按键占用的微控制器的I/O资源非常少,但是整体配置的繁杂性较

高。考虑到该设计仅需要很少的按键,因此选择单独的按键作为按键输入模块。

独立按键的结构比较简单,独立I/O口输入线与按键连接起来,这样一个单独按键就此形成。各个按键分别占用

一个微控制器的I/O端口,同时也会干扰其他按键的正常操作。此次设计中,独立的按钮直接连接到微控制器的引脚

P14至P17。

2.3 设计方案的选择

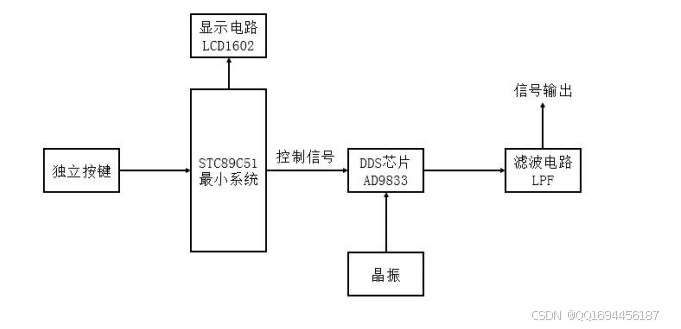

根据以上方案的分析,本设计的总体设计最终确定为:选择STC89C51单片机作为主控系统,AD9833芯片及其外

围电路作为信号发生电路。下图2-3是总体框图。

图2-3 系统总体框图

3 系统硬件电路设计

3.1总体硬件原理图

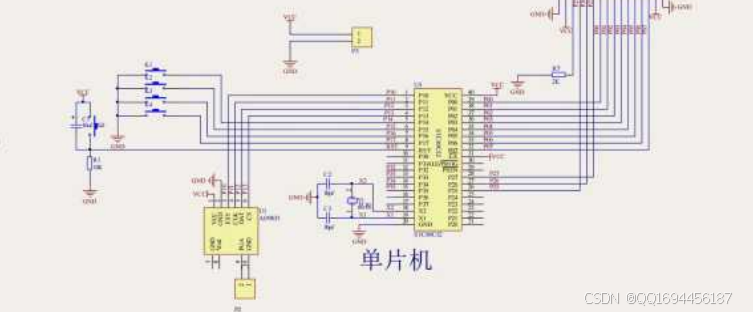

下图3-4为总体硬件原理图,一共有四个模块,分别是单片机设计模块、频率合成模块、按键输入模块和液晶显

示模块。在其中,设计方案控制板为STC89C51单片机;依靠对应的外围电路,频率合成模块顺利形成。按键输入模

块中采用了四个独立的按键。这种按键构造并不繁杂,可以联接独立的I/O口输入线,产生独立的按键。液晶显示屏

模块是LCD1602,支持数字、字母等的现实,并且控制程序并不复杂,可以将目标信息清楚的显示出来,带给人们极

大的便利。

图3-1 总体硬件原理图

3.2 单片机片内资源

单片机用户可通过单片机来获取的内容就是单片机内部资源。单片机内部资源主要包括FLASH、RAM、SFR。同时

单片机程序的存储工作依托OTPROM实现。伴随着科技力量的增强,FLASH进一步优化,表现出更突出的应用特征,例

如支持重写、大容量、低成本等等。同时单片机运用FLASH,最关键的一点是即便断电也不会发生数据丢失的尴尬情

况。这点与存储文档、音乐等文件的计算机硬盘有很大的共性。关闭电源后,下次重新启动计算机时,所有文件仍

然存在。

单片机数据存储空间为RAM,在程序执行环节会有数据生成,而RAM就扮演着这些数据的存储者的角色。实际上,

这与计算器很相近。加减法计算工作通过计算器实现,部分中间数据会在RAM中存储,如果遇到断电的情况,那么数

据也随之丢失。也就是计算机打开后,计算活动就从零重新开始。但是也有优势,即读写速度快、支持无限写。也

就是说,无论程序如何执行或读写,生命周期都是无限的。

第三个资源是特殊功能寄存器SFR。微控制器有很多功能,每个功能都配备一个或多个 SFR。通过读写SFR,实

现单片机的各种功能。Flash程序空间为 8K 字节(1K = 1024字节,1字节 = 8位),RAM 数据空间为 512 字节。

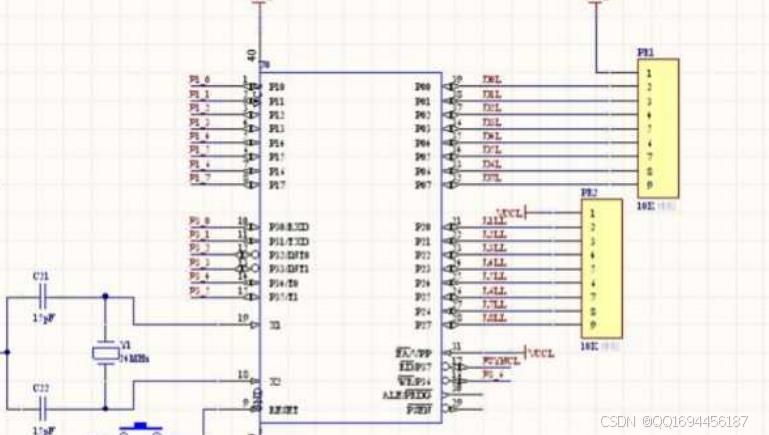

对于单片机系统电路而言,其核心为STC89C51。 STC89C51拥有丰富的I/O口和片上资源。 P3.0、P3.1和P3.7分

别连接到AD9833的 SDATA(引脚6)、SCLK(引脚7)和 FSYNC(引脚8),以控制zSPI接口访问。如图3-2所示。

图3-2 单片机系统电路图

3.3单片机系统与外部电路接口

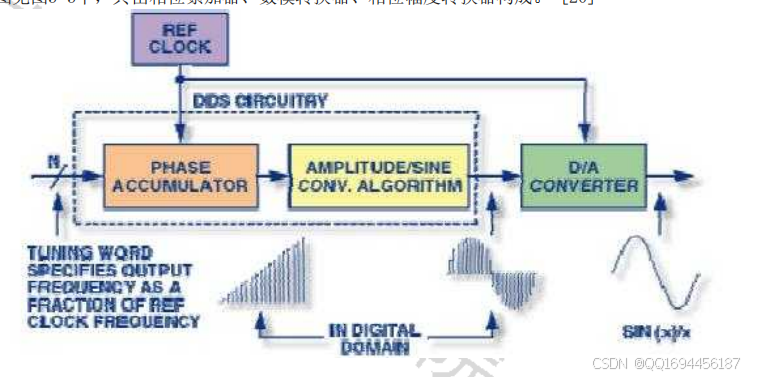

3.3.1 DDS信号发生器

DDS结构示意图见图3-3下,其由相位累加器、数模转换器、相位幅度转换器构成。 [20]

图3-3 DDS结构图

对于相位累加器而言,所产生的正弦波的幅度没有线性规律可言。但是相位的增长却呈现出线性特征。对于DDS

而言,正式在该功能的促进下完成信号的成功创建工作。根据图3-4显示,N是DDS频率控制字位数,将360°均分为

2N等份。

DAC接收到二进制数字信号之后,完成该信号的转换工作,模拟信号替代二进制数字信号并被输出。这里值得注

意是的,输出频率分辨率并不会受到DSC位数的干扰。因为频率控制字位数是输出频率分辨率的决定性因素。

DDS的数学原理如下:

1.参考时钟/系统时钟

参考时钟是DDS的输入时钟频率。DAC采样率为系统软件时钟,频率与输出频率成正比。自然,输出频率也是有稳定的范畴,上限是系统软件时钟频率的40%。参考时钟受到有无应用到内部PLL倍频器的影响,如果没有应用,系

统时钟就是参考时钟,如果使用到,那么参考时钟*M即系统时钟,M是PLL倍频器的倍频系数。

2.频率控制字(Frequency Tuning Word)

针对输出频率,决策要素是频率操纵字值。输出频率屏幕分辨率伴随着频率操纵字的总数而提升,频率分辨率

为Fc/2N。

3.DAC 输出电压范围(Voltage Compliance Range)

DAC输出电压范围受到输出类型的直接影响,如果是电流输出型,那么输出电压必须控制在恰当范围内。同时输

出电流在负载端建成的电压值也不能超出该范围。不然,输出级有可能会损坏。[21]

DDS(直接数字频率合成)采用AD9833,AD9833是一款完全集成的电路,功能完善,既可以产

生射频信号同时还可以做好方案的调制、解调等工作。在DSP技术的助力下,繁杂的调制解调算法得以简化,同时不

影响结果的精准性。

AD9833 属于可编程波形发生器的范畴,该设备能耗不高。在SPI接口的促进下,顺利与单片机实现连接。同时

AD9833可被编程,并且以三角波、方波的形式输出。输出频率范围较广,0-10MHZ范围内即可。此外,该波形发生器

的外围电路不复杂,不需要专门设置外部元件。无论是输出的频率还是输出的相位均可依托软件完成编程,可灵活

调整。

AD9833所需的25MHz系统时钟由有源晶振来供给,单片机通过FSYNC、SCLK、SDATA和三个引脚控制AD9833。AD9833作

为全集成DDS电路,很容易产生12.5MHz的正弦波,仅需外部参考时钟、低精度电阻、去耦电容即可。[22]

AD9833 的引脚图如图3-6所示,其引脚按功能主要分为三类:电源引脚(表3-1),模拟信号引脚(表3-2),

数字接口和控制接口引脚(表3-3)。

表3-1 电源引脚

引脚 引脚功能

(1)

VDD

模拟和数字接口部分的供给,电源正电压范畴在2.3V和5.5V中间。事实上,必须在引脚和AGND中间并联,并

且还要接入0.1F和10F非耦合电容。

(2)

CAP

/2.

5V

数字电路工作电压是2.5V,AD9833的内部结构数字电路设计选用2.5V标准工作电压工作中。当VDD超过2.7V

时,必须在CAP/2.5V和DGND中间连接一个100uF的非耦合电容,才可以使内部结构标准工作电压正常的工作

中。当VDD低于2.7V时,要求CAP/2.5V和DGND直接相连。

(3)

DGND

数字地

(4)

AGND

模拟地

表3-2 模拟信号引脚

引脚 引脚功能

(1)COMP DAC偏差管脚

(2)VOUT 电压输出

表3-3 数字接口和控制接口引脚

引脚 引脚功能

(1)MCLK 数字时钟输入。DDS输出频率是MCLK的二进制分数形式,输出频率的准确性和相位噪声由这个时钟决定。

(2)SDATA串行数据输入。采用16位数据字格式。

(3)SCLK 串行时钟输入。在SCLK时钟的降低沿,串行通信数据信息移进AD9833。

(4)FSYC 控制输入低电平有效。

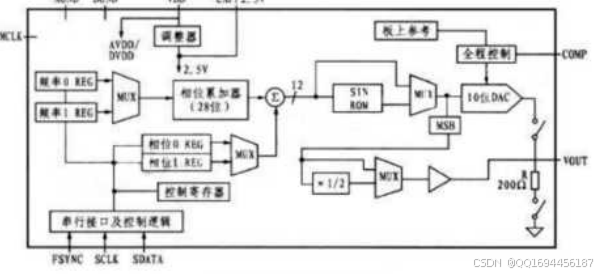

AD9833的内部结构如图3-7所示。它主要由数控振荡器和相位调制器、正弦查找表和10位数模转换器组成。数控振荡

器和相位调制器由两个频率选择寄存器、一个相位累加器、两个相移寄存器和一个相移加法器组成。[23]

图3-7 AD9833内部结构图

信号发生器由DDS芯片AD9833和单片机STC89C51组成。用户通过按键输入的信号必须被STC89C51接收,经过处理

后,将计算出的控制字发送到AD9833,AD9833产生下一个信号。

3.3.2 键盘和显示

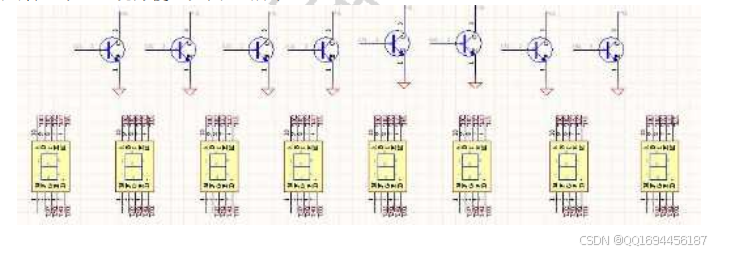

显示电路用数码管显示,直观方便,如图3-9所示。

图3-9 显示电路

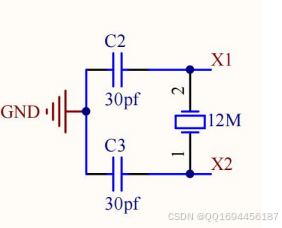

3.3.3晶振

晶体振荡器为系统软件提供基本上的时钟信号。通常,一个系统同用一个晶体振荡器,便于各部分保持同步。

在一些通信系统中,基频和微波射频应用不一样的晶体振荡器,并根据电子器件工作频率调节来同歩。

在该体系中,晶体振荡器与单片机内部结构电源电路紧密结合,产生单片机需要的时钟频率。单片机全部命令

的运行全是根据此。晶体振荡器提供的时钟频率越高,单片机的运作速率越快。晶振采用12MHz高平稳无源晶振,,

给CPU提供高稳定的时钟信号,12M单片机晶振,一般由于一个机器周期是12个时钟周期,更方便计时。图3-10为晶

振原理图

图3-10 晶振

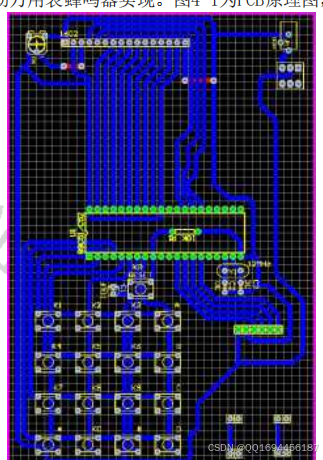

3.4焊接及调试

3.4.1焊接

根据电路原理图进行焊接,焊接时要确保各部分正负极电平连接没有问题。同时两端电压值与对应标准吻合,

保障焊点牢固,规避误焊的情况。待检查无误后,即可启动程序。焊接操作时,电源反接、引脚反接等情况无法完

全规避,一旦出现这些问题,电路会发生故障,甚至导致元器件被烧毁。待焊接工作结束后,必须做好短路、焊接

错误等情况的检测工作,检测操作借助万用表蜂鸣器实现。图4-1为PCB原理图,阐述了焊接的基本原理。

图3-10 PCB原理图

3.4.2调试

焊接完成,接通电源后,屏幕显示正常, 按键调试正常。并且可以通过矩阵按键实现频率的设置,然后输出,

正常波形输出0-5M波形可以完全显示,5M-10M波形出现谐波并且慢慢失真降低。幅值0-4.4V按键可调,步进值为0.1

V,并且可以液晶显示。当然到底输出哪类波形,可借助按键来选定。

4 系统软件设计

4.1主程序设计

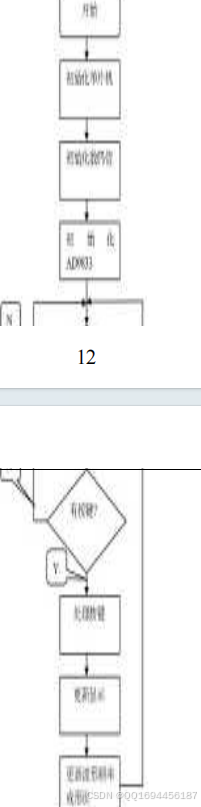

软件采用C语言编写,使用循环扫描在4x4键盘上完成扫描任务。程序流程示意图如图4-1下。

图4-1 程序主流程图

AD9833的核心任务明确,即以尽可能快的速度完成正弦波形的建立以及频率的切换工作。在软件的配合下,不

同的频率控制字被设置出来,频率切换的目标顺利达成。不同的频率控制字在AD9833中的写入操作即可完成,信号

输出通过软件程序完成控制。由于编程时AD9833频率控制字是16位,因此SPI写操作需分两步展开,当然还必须格外

关注AD9833数据位写顺序。它的数据格式高在前面,低在后面。

4.2子程序设计

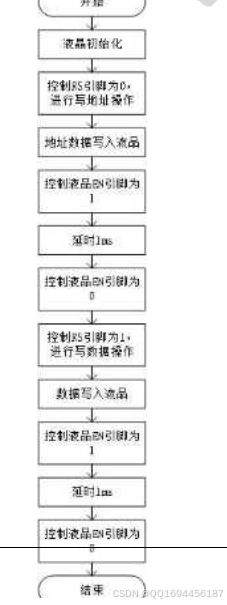

如图4-2,是系统的子程序流程图。首先进行液晶初始化,第一步完成液晶初始化操作,然后写地址时必须控制

RS引脚是0.地址数据写道液晶中,负责对液晶进行控制的引脚的EN是1,延时1ms后,控制液晶的引脚EN为0,控制RS

的引脚为1,进行数据写入的操作,随后数据写入液晶,EN为1,再延时1ms后,EN为0。

图5-2 子程序流程图

结 论

本课题的设计目标是细致把握好单片机STC89C51以及DDS芯片AD9833的运行原理,设计时实施的时候遇到了很多

棘手问题。通过外围电路的高效设计,目标外围电路的设计目标依托Proteus达成。功能的实现依托Keil平台编写的

程序,然后波形的输出通过外围硬件实现。

依据设计目标,顺利成功完成了根据直接频率合成技术(DDS)的信号源的设计,并经过了相应的硬件软件检测,

完成了设计目标的主要问题。所设计的信号源可以正弦波形、波形和三角波,并且输出频率范围在0-10M之间,而且

可以利用功能键更改步进值,调整频率大小,并在LCD1602液晶显示器上展示对应的信息。该设计方案不但电源电路

构造简易,系统软件功能齐全,还可以达到具体使用的规定,满足更多现实应用的需求。

1684

1684

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?