public class A {

volatile int a = 0;

public static void main(String[] args) {

A a = new A();

a.testVolatile();

}

public int testVolatile() {

a = 126;

return a;

}

}

root@ecs-b074:~

0x0000ffff65172230: orr w0, wzr,

0x0000ffff65172234: dmb ish

0x0000ffff65172238: str w0, [x1,

0x0000ffff6517223c: dmb ish

0x0000ffff8cc39194: sub sp, sp,

0x0000ffff8cc39198: stp x29, x30, [sp,

0x0000ffff8cc3919c: orr w12, wzr,

0x0000ffff8cc391a0: add x10, x1,

0x0000ffff8cc391a4: stlr w12, [x10]

0x0000ffff8cc391a8: ldp x29, x30, [sp,

0x0000ffff8cc391ac: add sp, sp,

0x0000ffff8cc391b0: ldr x8, [x28,

0x0000ffff8cc391b4: cmp sp, x8

0x0000ffff8cc391b8: b.hi 0x0000ffff8cc391c0

0x0000ffff9117224c: dmb ish

0x0000ffff91172250: ldr w0, [x1,

0x0000ffff91172254: dmb ishld

0x0000ffff98c391ac: ldar w0, [x10].

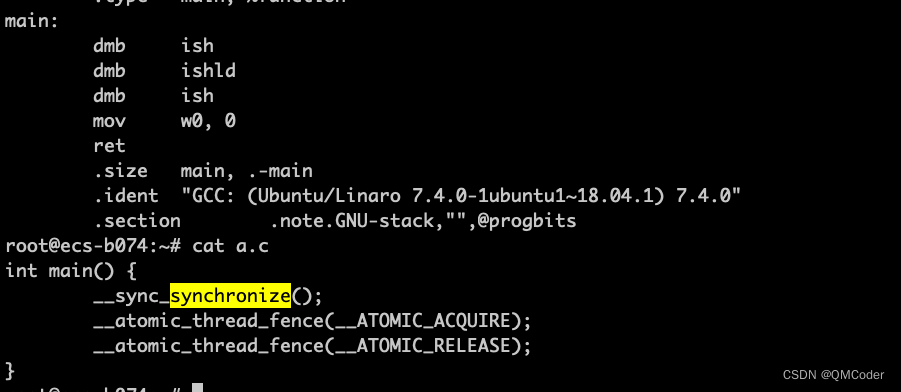

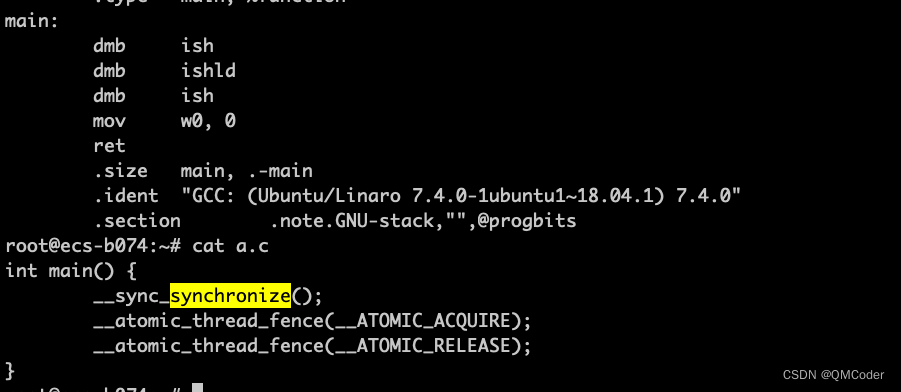

linux arm 内存屏障

__sync_synchronize();

__atomic_thread_fence(__ATOMIC_ACQUIRE);

__atomic_thread_fence(__ATOMIC_RELEASE);

jdk17 宏定义

#define FULL_MEM_BARRIER __sync_synchronize()

#define READ_MEM_BARRIER __atomic_thread_fence(__ATOMIC_ACQUIRE);

#define WRITE_MEM_BARRIER __atomic_thread_fence(__ATOMIC_RELEASE);

inline void OrderAccess::loadload() { acquire(); }

inline void OrderAccess::storestore() { release(); }

inline void OrderAccess::loadstore() { acquire(); }

inline void OrderAccess::storeload() { fence(); }

inline void OrderAccess::acquire() {

READ_MEM_BARRIER;

}

inline void OrderAccess::release() {

WRITE_MEM_BARRIER;

}

inline void OrderAccess::fence() {

FULL_MEM_BARRIER;

}

{

Label notVolatile;

__ tbz(r5, ConstantPoolCacheEntry::is_volatile_shift, notVolatile);

__ membar(MacroAssembler::StoreStore);

__ bind(notVolatile);

}

{

__ pop(dtos);

if (!is_static) pop_and_check_object(obj);

__ access_store_at(T_DOUBLE, IN_HEAP, field, noreg , noreg, noreg);

if (rc == may_rewrite) {

patch_bytecode(Bytecodes::_fast_dputfield, bc, r1, true, byte_no);

}

}

{

Label notVolatile;

__ tbz(r5, ConstantPoolCacheEntry::is_volatile_shift, notVolatile);

__ membar(MacroAssembler::StoreLoad);

__ bind(notVolatile);

}

参考:

dmb解释1

dmb解释2

文章详细展示了Java中volatile变量在不同编译器下如何实现内存屏障,包括dmb指令的使用,以及对读写操作的内存顺序保证。讨论了内存模型在多线程环境下的重要性,如storestore、loadload、loadstore和loadacquire等内存屏障的实现。

文章详细展示了Java中volatile变量在不同编译器下如何实现内存屏障,包括dmb指令的使用,以及对读写操作的内存顺序保证。讨论了内存模型在多线程环境下的重要性,如storestore、loadload、loadstore和loadacquire等内存屏障的实现。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?