阿里云盘最近老火了,云盘空间够大、下载也不限速,但是资源这方面还是差点,所以今天来给大家分享一个站点,里面有很多网友分享的阿里云盘资源,这下啥都有了!

先给大家瞅瞅这个站点长啥样:

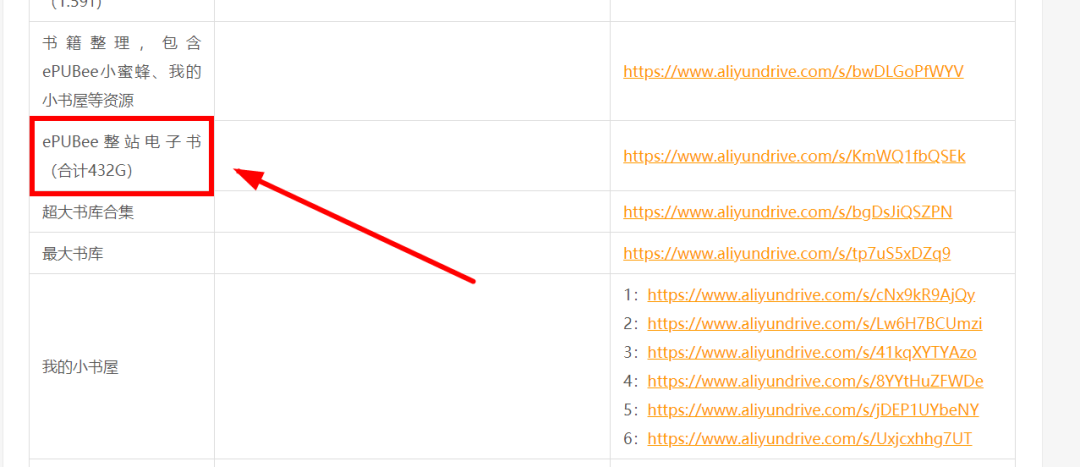

虽然卖相一般,光分享链接就有 290+,且个个是合集。

比如 ePUBee 小蜜蜂这个电子书资源站,这个里面就有把小蜜蜂全站扒下来的阿里云盘资源。

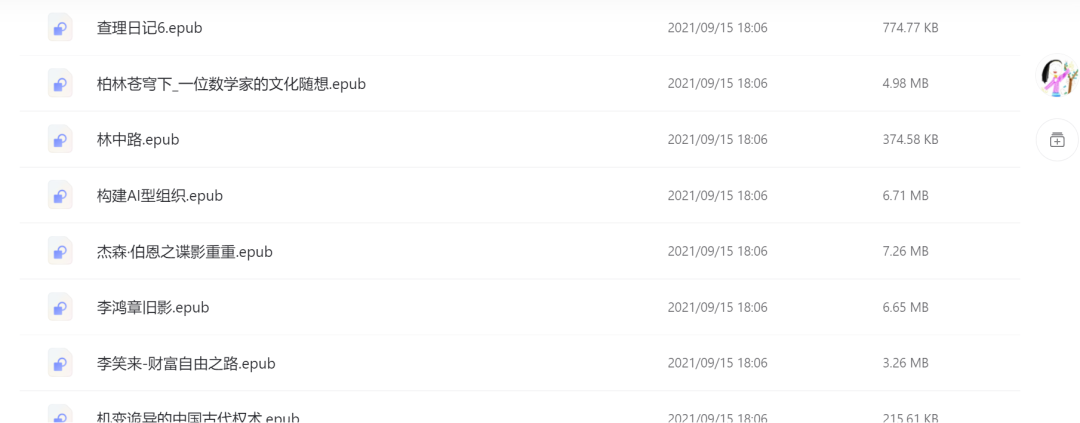

合计 432G 的电子书,点进去看你会发现全都是整理好的 epub 格式的电子书:

比如还有超2000册的计算机图书,永久有效

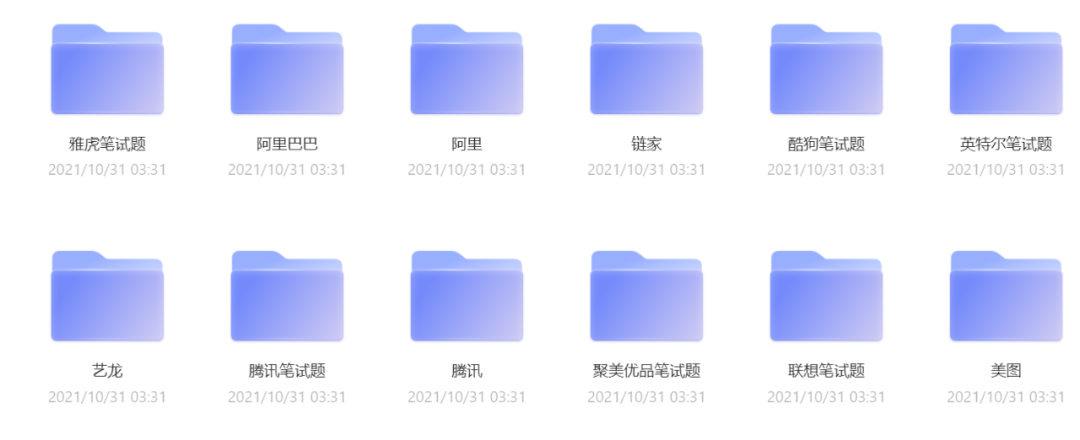

比如各大企业面试笔试汇总

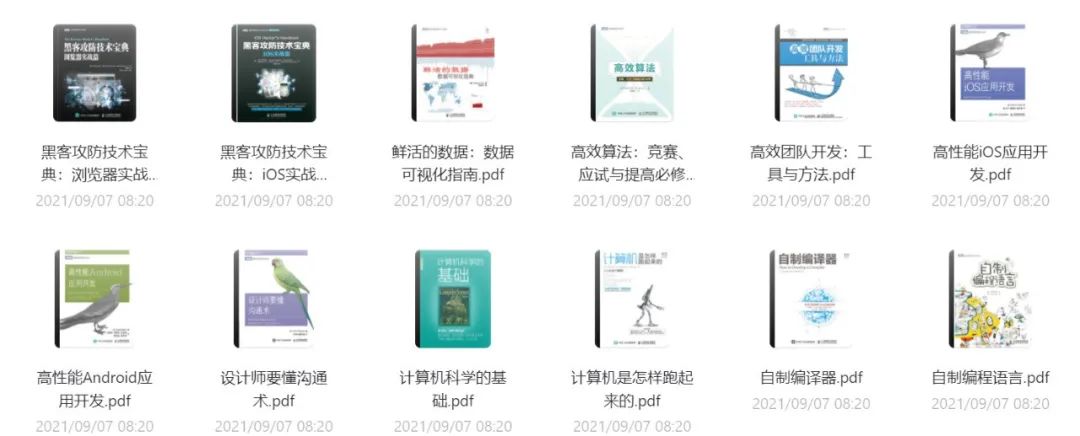

比如图灵设计丛书300+合集(PDF)

比如 10000+ 的 PPT 模板:

这个里面,还不乏大厂的内部培训资料、自媒体教程、理财课、心理学、面试汇总等等等等,想了解的小伙伴还是去亲自去看一下吧。

帖子的最前方,有 9 个资源大杂烩,套娃收录的是像这个帖子一样的资源文档。

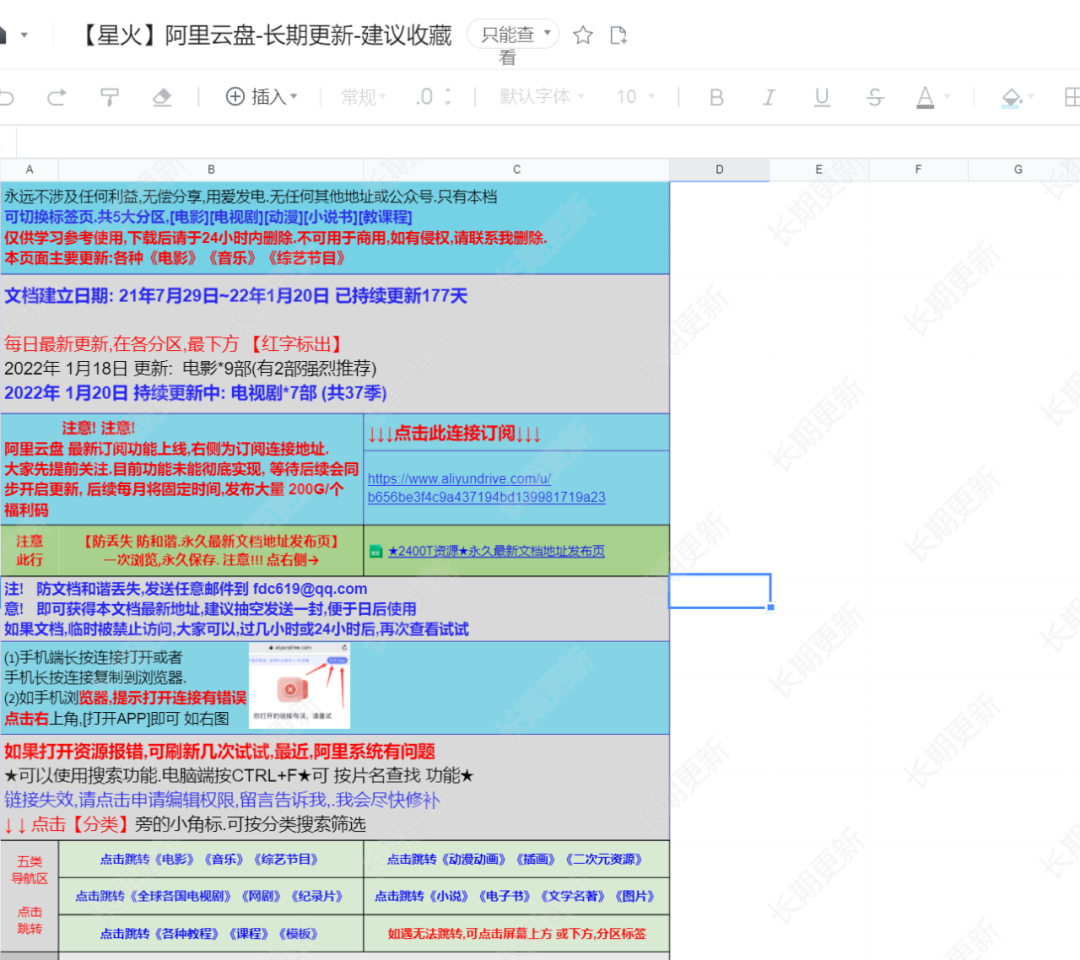

点开可以看到持续更新177天的腾讯文档,资源内容包罗万象,影视音乐、全球各国电视剧、动漫漫画等等。

这里还有上千个阿里云盘分享链接,大多数也都是合集的那种,一共算下来有 2400T 的资源。

获取资源

公众号回复

阿里

两个搜索引擎

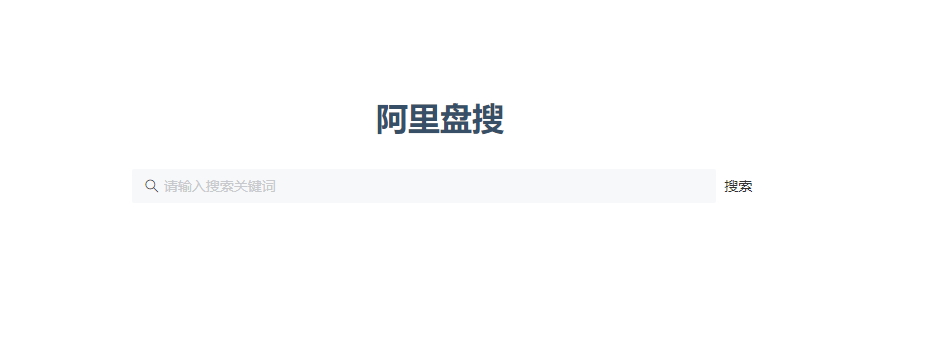

阿里盘搜

这是一个干净到只剩下站名和搜索框的网站,广告什么的通通没有。

所以你想要什么资源,直接去输入框里搜就行了,比如我们搜个「漫威 4K」的关键词,就有 N 个漫威电影全集的阿里云盘分享链接。

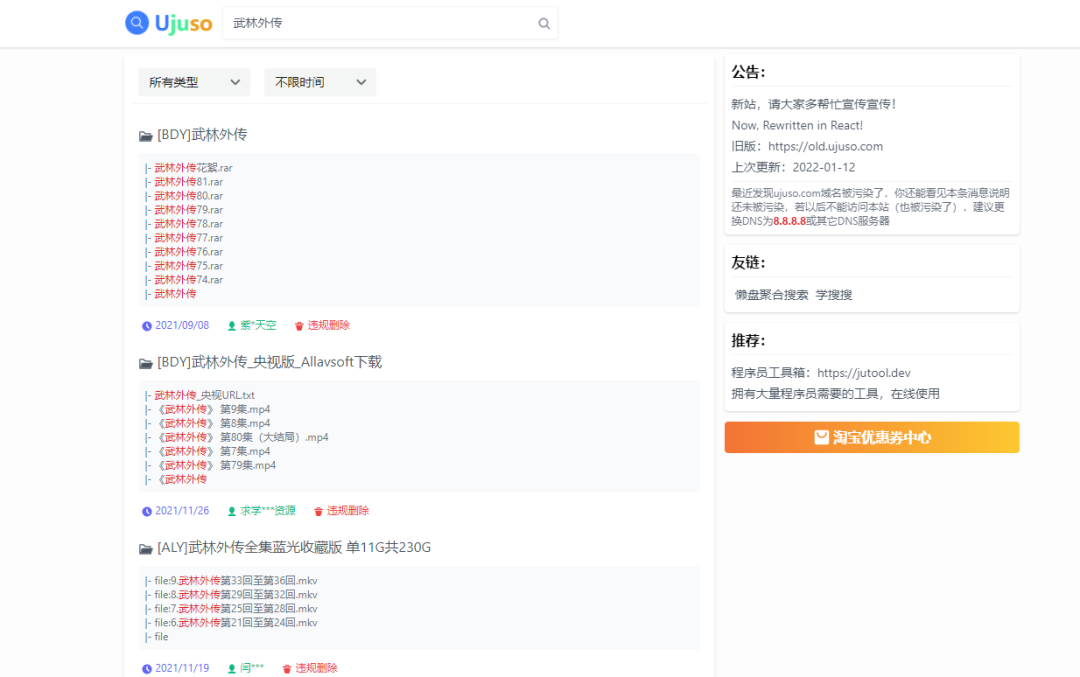

优聚搜

瞅瞅优聚搜的主页,同样很干净,我们不用管那些搜索框下的热门关键词,去搜索框里直接搜索内容即可。

优聚搜默认的是度盘、蓝奏云、阿里云盘的全局搜索,能看到网上各种分享,不乏有蓝光收藏版的资源存在。

获取资源

公众号回复

阿里

6万+

6万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?