题目

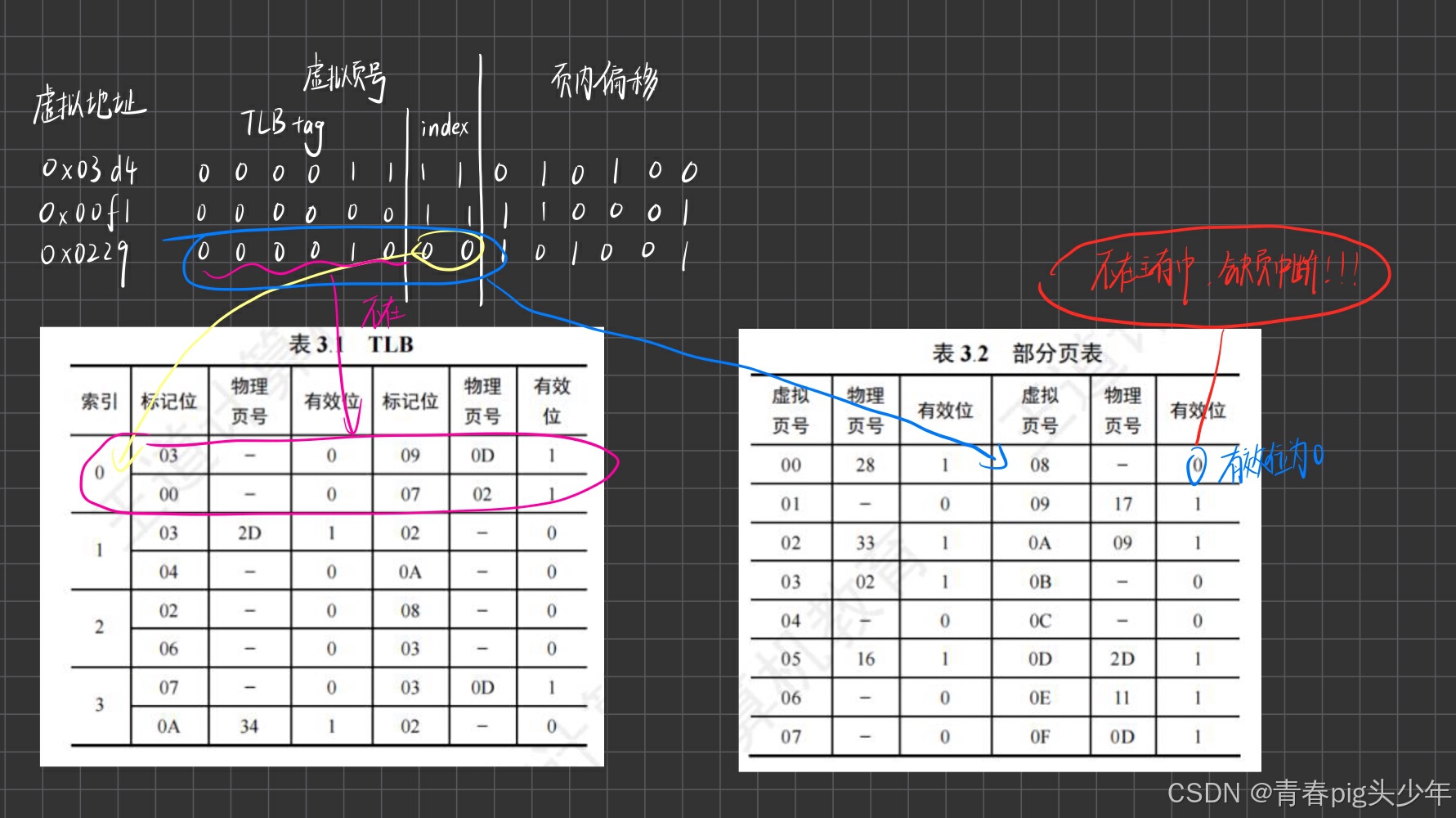

设某系统满足以下条件:

- 有一个TLB与一个data Cache

- 存储器以字节为编址单位

- 虚拟地址14位

- 物理地址12位

- 页面大小为64B

- TLB为四路组相联,共有16个条目

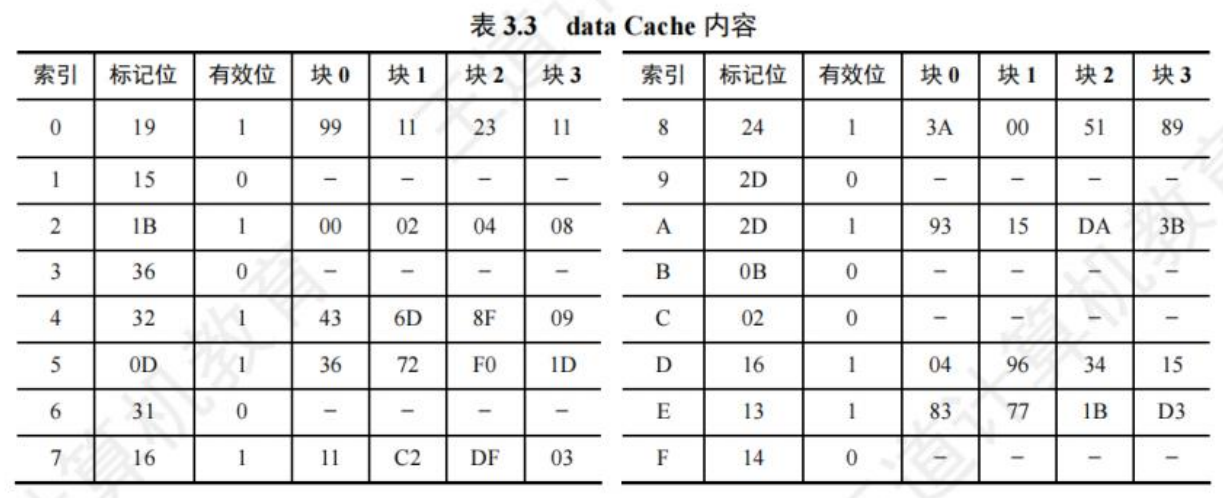

- dataCache是物理寻址、直接映射的,行大小为4B,共有16组

写出访问地址为0x03d4,0x00f1和0x0229的过程。

分析

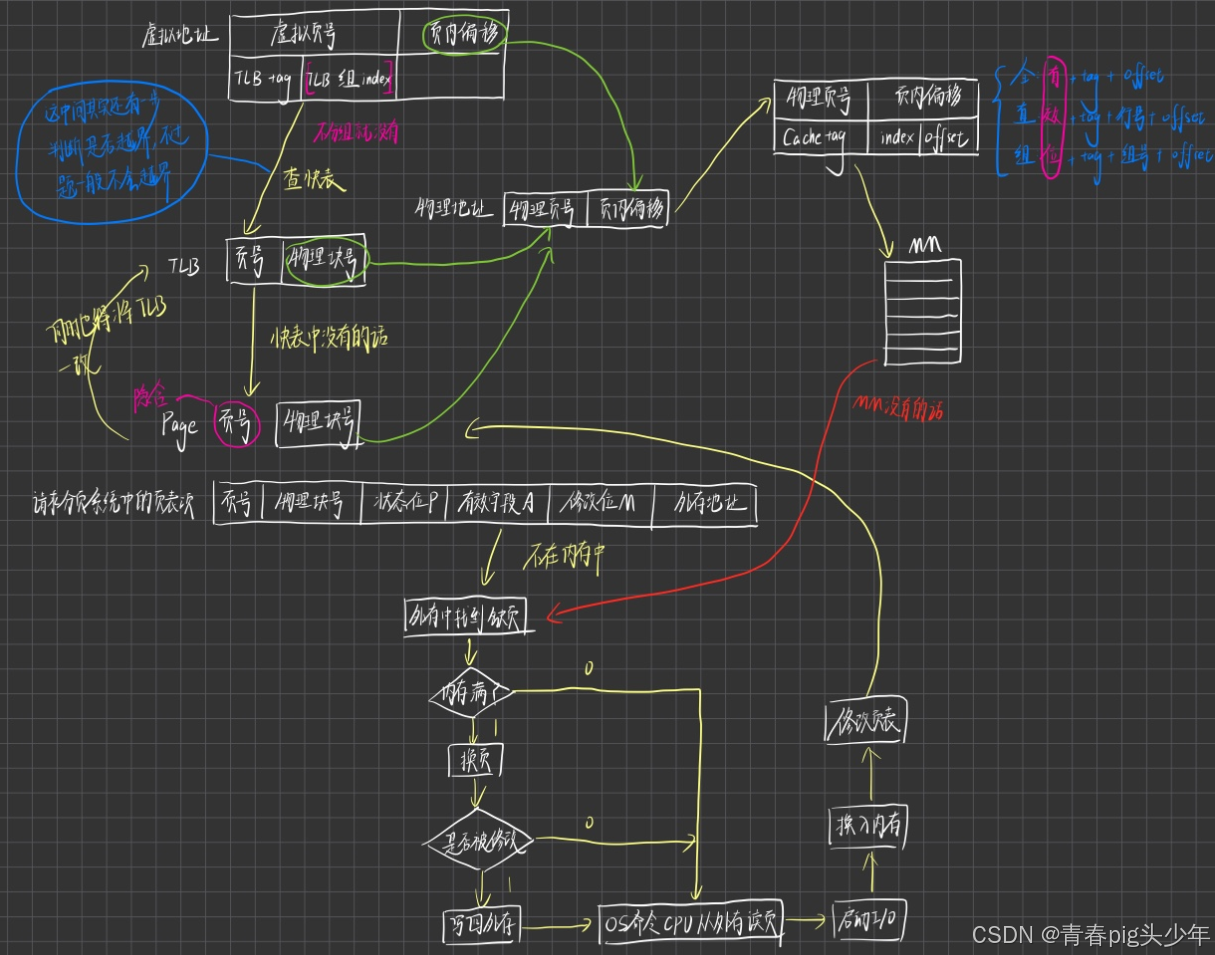

碰到这种OS和POCC合一块的题目,咱先不能慌张,先想一下这一整个寻址过程是什么样的呢?

(王道里面有原图)

流程我们都大抵知道对吧,那为什么还是做的晕头转向呢?

我想可能是没有搞清楚各个时候的地址结构以及对应的名词。但是如果变成下述我画的这个样子的话,应该还是很好捋清楚的。

答案

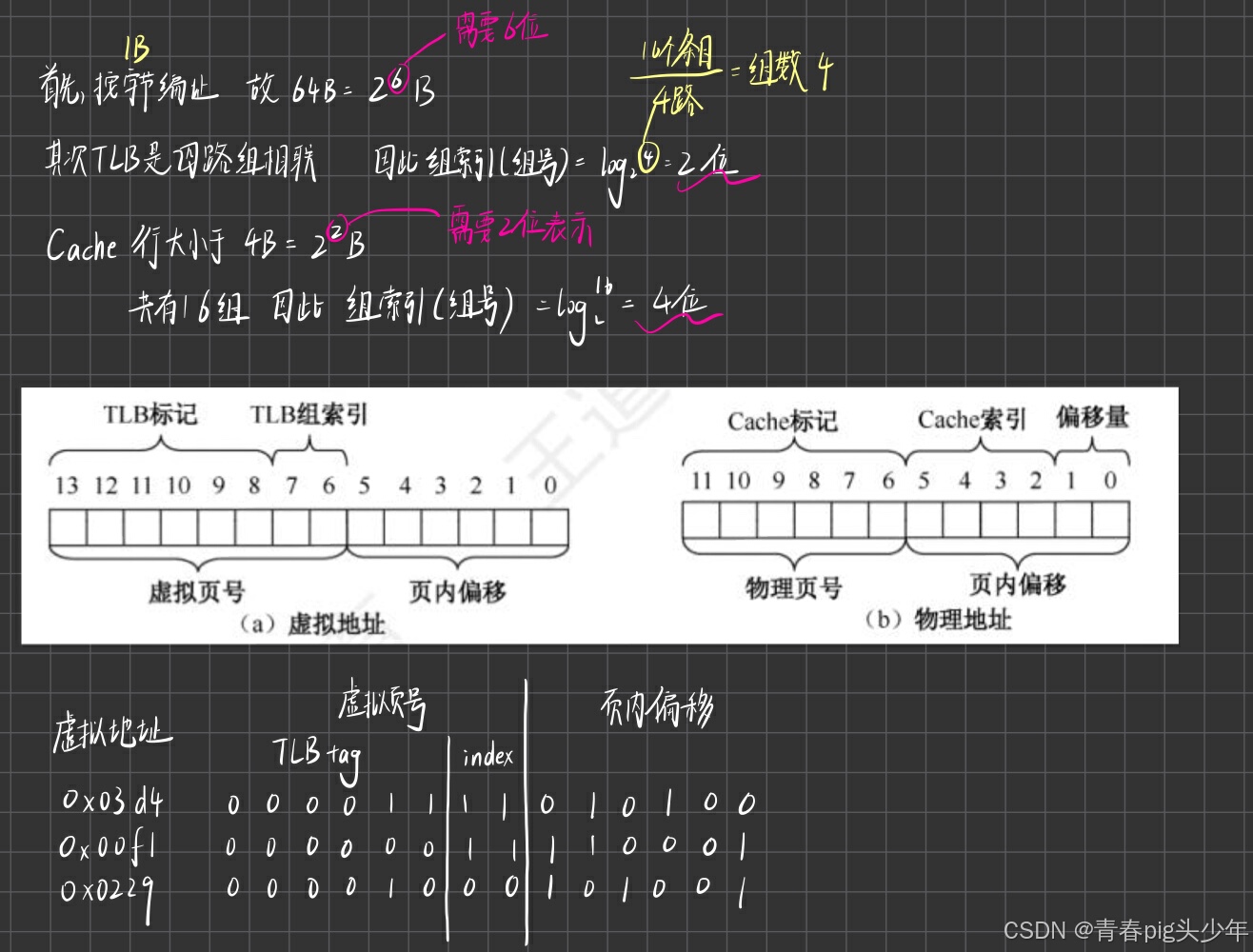

那首先我们是不是得先搞清楚虚拟地址和物理地址各自长什么样子嘞。(根据题设其实还是蛮轻松的对吧,稍微要注意一下的就是最后一条,“16组”才是关键!)

在得到每个地址的组索引和TLBtag之后。就要找出每个地址的页面在不在主存中,若是在主存中则还要找出物理地址。

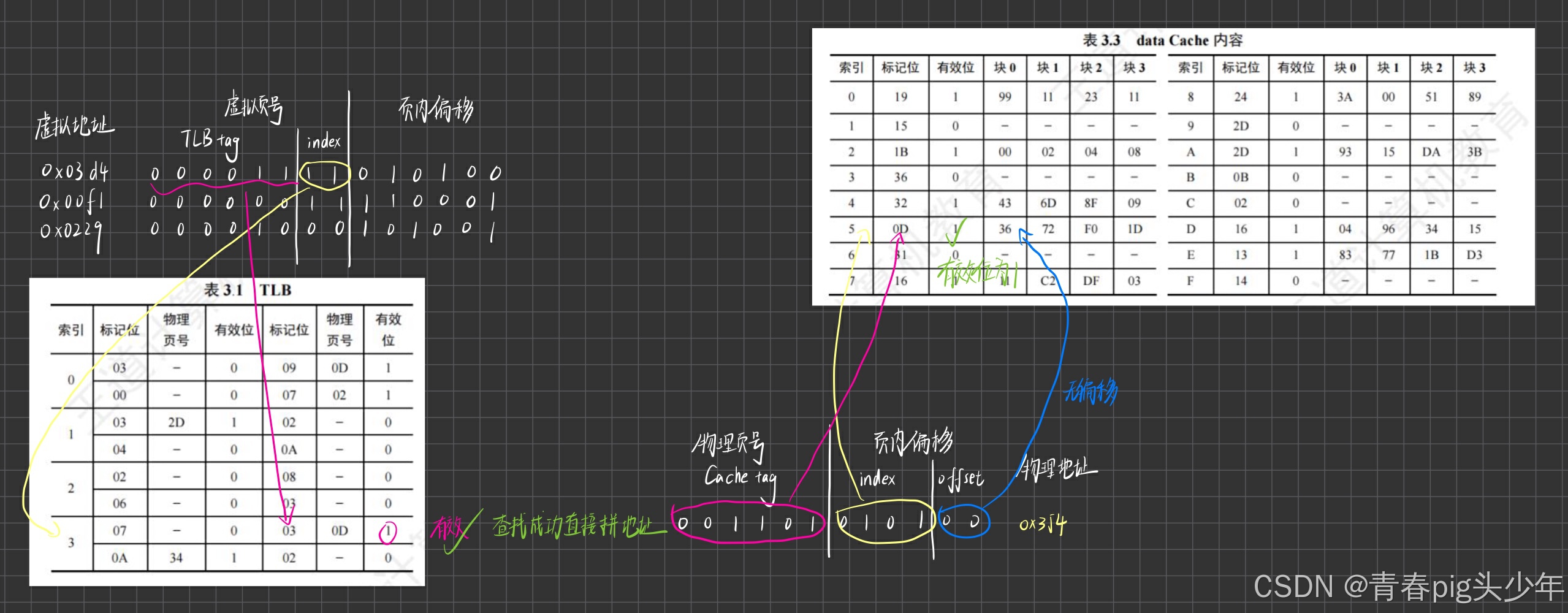

Case 1:TLB ✓ Page ✓ Cache ✓

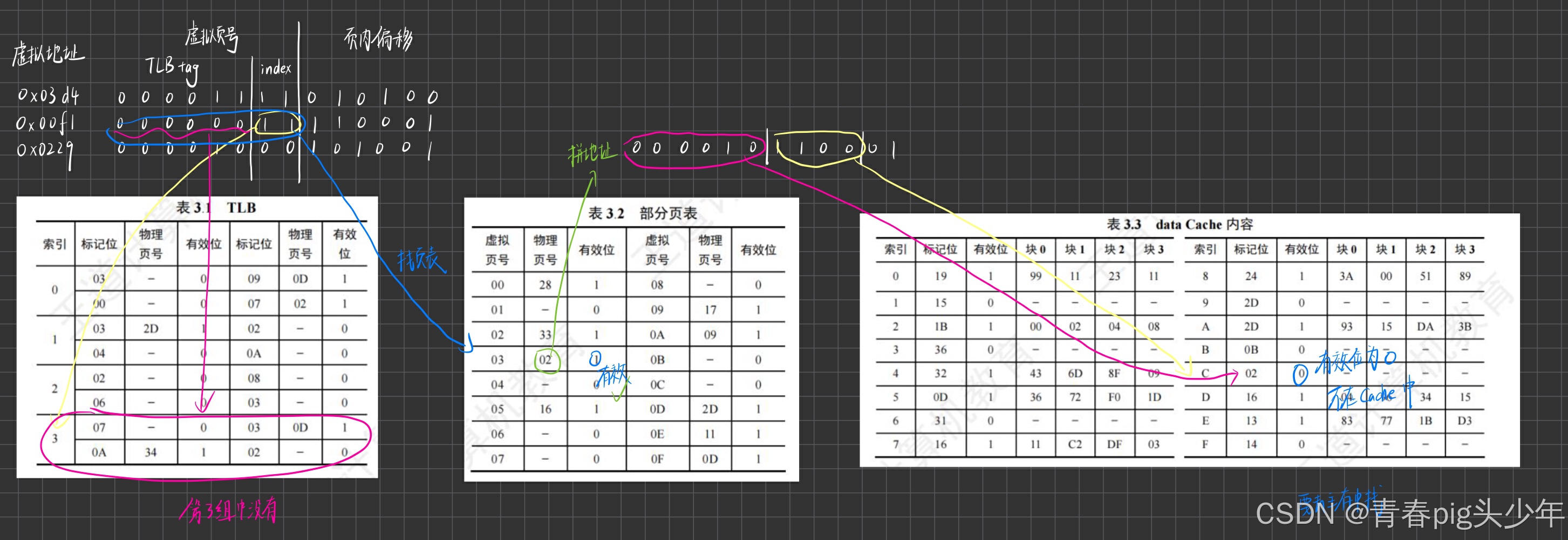

Case 2:TLB × Page ✓ Cache ×

(忘记画了,这个也是缺页中断)

Case 3:TLB × Page × Cache ×

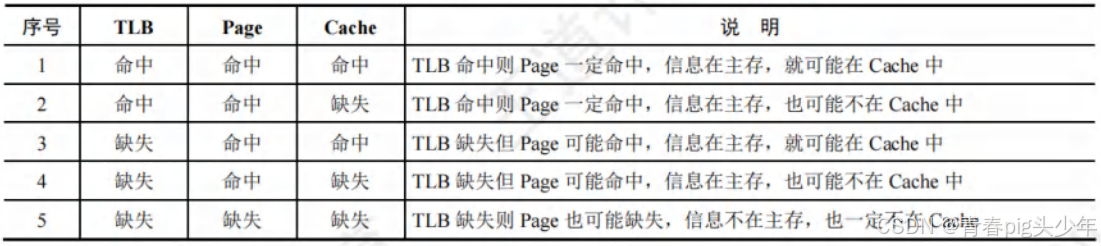

这个例子也是王道书里的经典题目了,基本涵盖了从虚拟地址到Cache查找内容的所有可能出现的情况,还是要好好理解下一下,把这部分知识吃下来。(查找顺序是从TLB到页表(TLB不命中),再到Cache和主存,最后是外存)

可以参照着这个图巩固一下记忆。

真题

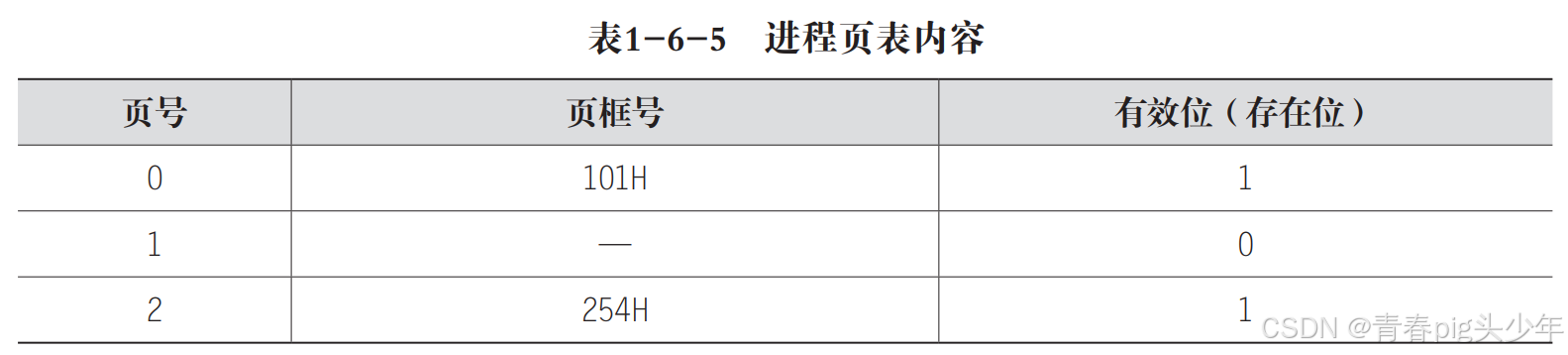

请求分页管理系统中,假设某进程的页表内容如表 1-6-5 所示。

页面大小为 4KB,一次内存的访问时间是 100ns,一次快表的访问时间是 10ns,处理 一次缺页的平均时间是 10^8 ns(已含更新快表和页表的时间),进程的驻留集大小固定为 2, 采用 LRU 页面置换算法和局部淘汰策略。

假设 :

①快表初始为空 ;

②地址转换时先访问快表,若快表未命中,则再访问页表(忽略访问页表之后的快表更新时间);

③有效位为 0 表 示页面不在内存中,产生缺页中断,缺页中断被处理后,返回产生缺页中断的指令处重新执行。

设有虚地址访问序列 2362H、1565H、25A5H,请问 :

(1)依次访问上述 3 个虚地址,各需要多少时间?给出计算过程。

(2)基于上述访问序列,虚地址 1565H 的物理地址是多少?请说明理由。

(1)页面大小为4KB=212B,故页内偏移量为12位,占虚地址的低12位,高4位为页号。

虚地址2362H的页号为2,页内地址为362H。先访问快表(10ns),未命中;再去访问页表 (100ns),获得对应的物理块号254H,其与页内地址362H拼接成物理地址254362H,同时将第 2页的信息装入快表中;最后根据这个物理地址访问内存(100ns)。因此,访问到虚地址对应单元的数据总共需要10ns+100ns+100ns=210ns。

同理,虚地址1565H的页号为1,页内地址为565H。先访问快表(10ns),未命中;访问页表(100ns),不在内存中,产生缺页中断,中断处理时间为10^8 ns,然后返回产生缺页中断的指 令处重新执行,并以此更新快表和页表;访问快表(10ns)便可得到对应的物理地址,根据物 理地址访问内存(100ns)。总共需要10ns+100ns+10^8 ns+10ns+100ns≈10^8 ns。

同理,虚地址25A5H的页号为2,页内地址为5A5H。先访问快表(10ns),该页信息已装入快表,获得对应的物理块号254H,从而拼接成物理地址2545A5H,根据该地址访问数据 (100ns)。总共需要110ns。

(2)访问1565H时,产生缺页中断,在处理中断时,合法驻留集为2(快表已经满了,因为第一次2就放进去了,第二次缺页之后快表也连同着更新放了1,所以这时候快表是满的),内存已满,LRU页面置换算法将选择淘汰0号页(因为2刚刚被用过),然后将101H号页框分配给1号页,这样便可得到页对应的物理块号 101H,其与页内地址565H拼接成的物理地址为101565H。

1697

1697

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?