参考来源:verilog编程艺术

设计SoC时重点考虑的问题:

-

设计规模问题:SoC集成了众多的数字模块和模拟模块,同时又要求在面积、性能和功耗上达到最优,导致规划、设计、验证、测试都极为复杂

-

时序收敛问题:随着工艺的进步,互连线延迟占主导地位,同时又要求很高的主频,导致让设计满足时序要求越来越难

-

信号完整性问题:信号之间的电容耦合作用会导致信号之间发生串扰,更长的互连线会导致线上电阻增加,从而导致可靠性、可制造性和系统性能降低

-

电源功耗问题:设计集成度、复杂度和工作频率的提高,会导致动态功耗快速地增加,同时随着工艺尺寸的缩小,静态功耗又急剧地增加。功耗增加会影响芯片的正常工作,会缩短芯片的寿命,会缩短电池的使用时间。为了进行低功耗设计,不得不使用了各种降低功耗的手段,例如使用多阈值的单元,划分电源域,动态调整电压,但是这些又曾加了设计的难度

-

可制造性和成品率:过去芯片的成品率取决于工厂的工艺水平,现在的成品率则依赖于设计本身的特征。随着集成度的提高,以及工艺的发展,出现了很多影响成品率的不良因素,例如平整性对时序的影响、过孔空洞效应等、

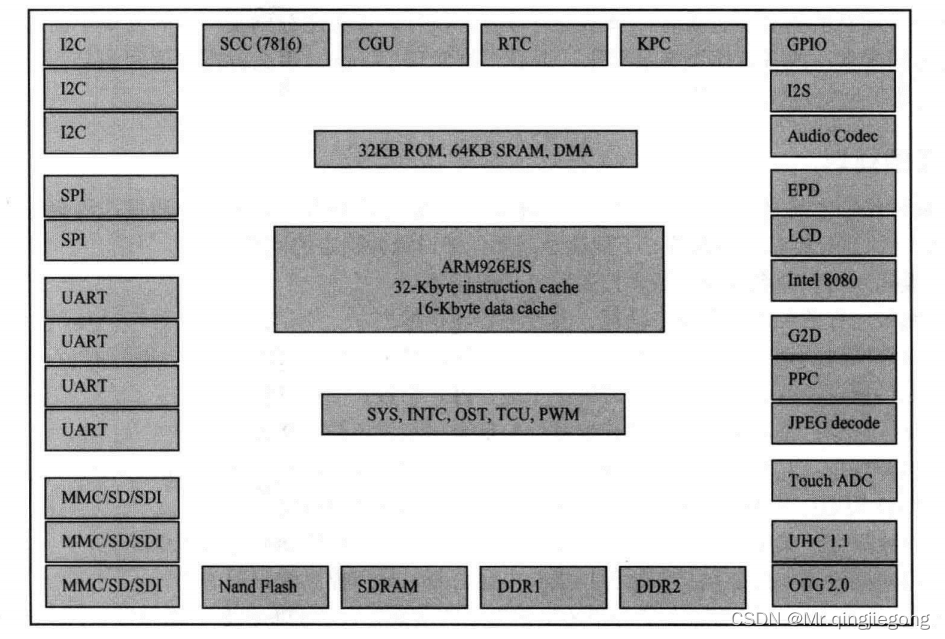

ARM926EJS芯片的构成框图,是一个完整的SoC,包含了CPU、内存和各种的控制器

本文探讨了在设计SoC时面临的挑战,如大规模整合、时序收敛、信号完整性、电源功耗控制以及可制造性问题,以ARM926EJS芯片为例,强调了Verilog编程在解决这些难题中的作用。

本文探讨了在设计SoC时面临的挑战,如大规模整合、时序收敛、信号完整性、电源功耗控制以及可制造性问题,以ARM926EJS芯片为例,强调了Verilog编程在解决这些难题中的作用。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?