一起来充电吧!

UG892

Chapter 1 Vivado System-Level Design Flow

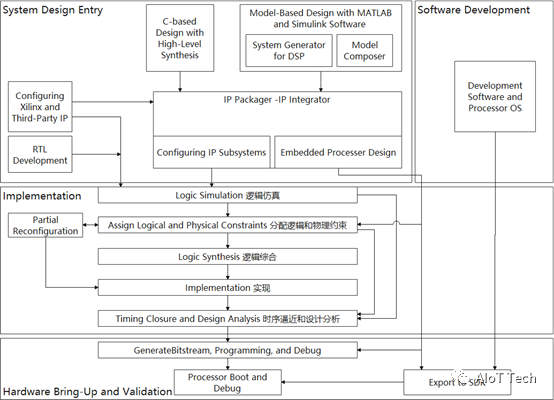

Vivado Design Suite 提供多种途径来完成包括Xilinx device design、implementation和verfication 的任务。我们可以使用传统的register transfer level(RTL)-to-bitstream(寄存器传输级-比特流)FPGA设计流程,也可以使用专注于IP核设计和基于C语言设计的system-level integration(系统级集成)设计流程。

设计流程的每个阶段都可以启用设计分析和仿真。设计分析功能包括逻辑仿真、I/O和时钟规划、功率分析、约束定义和时序分析、设计规则检查(DRC)、设计逻辑可视化、分析和修改实现结果、编程和调试。

VivadoDesign Suite Tutorial: Design Flows Overview (UG888)

整个解决方案集成在一个称为Vivado集成设计环境(IDE)的图形用户界面(GUI)中。VivadoIDE提供了一个接口来组装(assemble)、实现和验证设计或IP。此外,所有流程都可以使用Tcl命令运行。我们可以在Vivado设计工具Vivado20xx.xTcl shell或Vivado IDE Tcl控制台中编写Tcl命令。您可以使用Tcl脚本来运行整个设计流,包括设计分析,或者只运行设计流程中的一部分。

Vivado设计套件支持以下已建立的行业设计标准:

• Tcl

• AXI4, IP-XACT

• Synopsys design constraints (SDC)

• Verilog, VHDL, VHDL-2008, SystemVerilog

• SystemC, C, C++

Vivado设计套件解决方案是基于原生Tcl的,支持SDC和Xilinx设计约束(XDC)格式。广泛支持Verilog、VHDL和SystemVerilog综合语言使FPGA更容易采用。Vivado高级综合(HLS)支持使用C、c++或SystemC语言来定义逻辑。使用标准的IP互连协议,如AXI4和IP-xact,可以实现更快、更容易的系统级设计集成。对这些行业标准的支持还使电子设计自动化(EDA)生态系统能够更好地支持Vivado设计套件。此外,Vivado设计套件还集成了许多新的第三方工具。

下图展示了Vivado设计工具的高级设计流程。

RTL-to-BitstreamDesign Flow

您可以指定RTL源文件来创建项目,并使用这些源文件进行RTL代码开发、分析、合成和实现。Xilinx提供了一个推荐的RTL和约束模板库,以确保RTL和XDC以最佳形式与Vivado设计套件一起使用。Vivado合成和实现支持多种源文件类型,包括Verilog、VHDL、SystemVerilog和XDC。

Vivado Design Suite User Guide: System-Level Design Entry (UG895)

IPDesign and System-Level Design Integration

Vivado设计套件提供了一个环境,用户可以在单独的模块中配置、实现、验证和集成IP,或在系统级设计环境中实现这些功能。IP可以包括逻辑,嵌入式处理器,数字信号处理(DSP)模块,或基于c的DSP算法设计。定制IP是按照IP- xact协议打包的,然后通过Vivado IP目录提供。IP目录为IP的配置、实例化和验证提供对IP的快速访问。Xilinx IP利用axis4 interconnect标准支持更快的系统级集成。现有的IP可以在RTL或netlist格式的设计中使用。

Vivado Design Suite User Guide: Designing with IP (UG896)

IP Subsystem Design

Vivado IP Integrator环境使您能够使用AMBA AXI4互连协议将各种IP连接到IP子系统中。您可以使用块设计风格的接口以交互方式配置和连接IP,并通过绘制类似原理图的DRC-correct连接轻松连接整个接口。与传统的基于rtl的连接相比,使用标准接口连接IP节省了时间。提供了连接自动化以及一组drc,以确保正确的IP配置和连接。然后,这些IP块设计被验证、打包,并作为单一的设计源处理。块设计可以在设计项目中使用,也可以在其他项目中共享。IP Integrator环境是嵌入式设计和Xilinx评估板接口之间的主要接口。

Vivado Design Suite User Guide: Designing IP Subsystems UsingIP Integrator (UG994)

I/Oand Clock Planning

Vivado IDE提供一个I/O引脚规划环境,使I/O端口分配到特定的芯片封装引脚或内部垫片,并提供表格,让用户设计和分析封装和I/O相关的数据。内存接口可以交互式地分配到特定的I/O块(bank),以获得最佳的数据流。您可以使用Vivado引脚规划器中可用的视图和表分析设备和设计相关的I/O数据。该工具还提供了I/ODRC和同步切换噪声(SSN)分析命令,以验证I/O分配。

Vivado Design Suite User Guide:I/O and Clock Planning (UG899)

XilinxPlatform Board Support

在Vivado设计套件中,您可以选择一个现有的Xilinx评估板作为设计的目标。在评估板中,在目标板上实现的所有IP接口都显示了出来,以便能够快速选择和配置在设计中使用的IP。产生的IP配置参数和物理板子约束,如I/O标准和封装引脚约束,在整个流程中自动分配和激励。连接自动化能够快速连接到所选IP。

Vivado DesignSuite User Guide: System-Level Design Entry (UG895)

Synthesis

Vivado synthesis执行整个RTL设计的全局或自顶向下。但是,默认情况下,Vivado设计套件使用OOC(out-of-context)或自底向上的设计流来从Xilinx IP目录合成IP核,从VivadoIP集成器合成块设计。您还可以选择将分层RTL设计的特定模块合成为OOC模块。这个OOC流允许你综合、实现和分析层次设计、IP核或块设计的设计模块,脱离顶层设计,或独立于顶层设计。在顶级实现期间存储和使用OOC合成网列表,以保存结果并减少运行时间。OOC流程是支持分层团队设计、集成和实现IP和IP子系统以及管理大型复杂设计模块的有效技术。(out-of-context:作为独立的模块综合)

DesignAnalysis and Simulation

Vivado设计套件允许您在设计过程的每个阶段分析、验证和修改设计。您可以运行设计规则和设计方法检查,逻辑仿真,时序和功率分析,以改善电路性能。这个分析可以在RTL细化、合成和实现之后运行。

Vivado Design Suite UserGuide: Design Analysis and Closure Techniques (UG906)

Vivado仿真器使您能够在设计流程的不同阶段运行设计的行为和结构逻辑仿真。该仿真器支持Verilog和VHDL混合模式仿真,结果可以在集成在Vivado IDE的波形查看器中显示。您还可以使用可以集成到Vivado IDE并从Vivado IDE启动的第三方仿真器。

Placementand Routing

当合成的网列表可用时,Vivado implementation提供所有必要的特性,以优化、放置和路由网表到目标器件的可用设备资源上。Vivado实现的工作是满足设计的逻辑、物理和时间约束。

对于具有挑战的设计,Vivado IDE还提供了先进的布局规划功能,以改进实现结果。这包括将特定逻辑约束到特定区域的能力,或者手动放置特定的设计元素,并为后续的实现运行修复它们。

Vivado Design Suite UserGuide: Design Analysis and Closure Techniques (UG906)

HardwareDebug and Validation

在实现之后,可以对设备进行编程,然后使用Vivado逻辑分析器或在独立的Vivado Lab Edition环境中进行分析。调试信号可以在RTL设计中识别出来,也可以在合成后插入,并在整个流程中进行处理。您可以将调试核添加到RTL源文件中,添加到合成的网络列表中,或者在使用工程变更顺序(ECO)流程的实现设计中。您还可以修改连接到调试探头的网络,或将内部信号路由到一个封装引脚,以便使用ECO流进行外部探测。

Vivado Design Suite UserGuide: Programming and Debugging (UG908)

AlternateRTL-to-Bitstream Design Flows

Vivado设计套件还支持几个备选设计流,如下面的章节所述。这些流中的每一个都是从RTL-to-bitstream流派生出来的,所以上面描述的实现和分析技术也适用于这些其他的设计流。

SDAcceland SDSoC Design

SDAccel和SDSoC开发环境为C、c++和OpenCL API开发提供了类似gpu的、熟悉的软件应用程序开发和运行时体验。

SDAccel EnvironmentUser Guide (UG1023)

SDSoCEnvironment User Guide (UG1027)

EmbeddedProcessor Design

在创建嵌入式处理器设计时,需要一个略有不同的工具流程。由于嵌入式处理器需要软件才能有效启动和运行,因此软件设计流程必须与硬件设计流程一致。硬件和软件流之间的数据交换,以及跨这两个领域的验证对于成功是至关重要的。

创建嵌入式处理器硬件设计涉及Vivado设计套件的IP integrator。在Vivado IP integrator块设计中,需要实例化、配置和组装处理器核心及其接口。IP integrator执行基于规则的连接并提供设计帮助。通过implementation编译后,硬件设计被导出到Xilinx软件开发工具包(SDK)中,用于软件开发和验证。仿真和调试特性允许您跨两个域仿真和验证设计。

Vivado Design Suite UserGuide: Embedded Processor Hardware Design (UG898)

Vivado Design Suite Tutorial: Embedded Processor Hardware Design (UG940)

UltraFast Embedded Design Methodology Guide (UG1046)

Model-Based Design Using Model Composer

Model Composer是一个基于模型的图形设计工具,它能够在MathWorks MATLAB和Simulink产品中进行快速设计探索,并通过自动代码生成加速Xilinx设备设计。ModelComposer User Guide (UG1262)

Model-Based DSP Design Using Xilinx System Generator

作为Vivado设计套件的一部分安装的XilinxSystem Generator工具可用于实现DSP功能。使用System Generator作为独立工具创建DSP函数,然后将系统生成器设计打包到一个可以包含在Vivado IP目录中的IP模块中。从那里,生成的IP可以作为一个子模块实例化到Vivado设计中。VivadoDesign Suite User Guide: Model-Based DSP Design Using System Generator (UG897)

High-LevelSynthesis C-Based Design

Vivado设计套件中的C-based High-Level Synthesis (HLS)工具使您能够在设计中使用C、C++和SystemC来描述各种DSP功能。您可以使用Vivado HLS工具创建并验证C代码。使用高级语言可以抽象算法描述、数据类型、规范等。您可以使用各种参数创建“假设”场景,以优化设计性能和设备区域。

HLS允许您使用基于c的测试平台和仿真直接从其设计环境仿真生成的RTL。C-to-RTL合成将基于c的设计转换为一个RTL模块,该模块可以作为一个大型RTL设计的一部分被封装和实现,或者实例化为IPIntegrator块设计。

Vivado Design Suite User Guide:High-Level Synthesis (UG902)

Vivado Design Suite Tutorial: High-Level Synthesis (UG871)

PartialReconfiguration Design

部分重配置允许使用部分位流实时地重新配置正在运行的Xilinx设备的部分,从而改变正在运行的设计的特性和功能。必须正确地规划可重构模块,以确保它们按需要发挥最大性能。

部分重构流程需要一个严格的设计过程,以确保可重构模块被正确设计,以便在部分比特流更新期间实现无故障操作。这包括减少进入可重构模块的接口信号数量、布局规划设备资源和引脚设置;以及附着特殊的部分重配置drc。设备编程方法也必须适当地规划,以确保配置I/O引脚被适当地分配。

Vivado Design Suite User Guide: PartialReconfiguration (UG909)

Vivado Design Suite Tutorial: Partial Reconfiguration (UG947)

HierarchicalDesign

层次设计(HD)流程使您能够将设计划分为更小、更易于管理的模块,以独立处理。分层设计流程包括适当的模块接口设计、约束定义、布置图规划以及一些特殊的命令和设计技术。Vivado Design Suite User Guide:Hierarchical Design (UG905)

使用模块化方法进行分层设计,可以独立于设计的其余部分分析模块,并在自顶向下设计中重用模块。用户团队可以对设计的特定部分进行迭代,实现时序逼近和其他设计目标,并重用结果。

Vivado有几个特性支持分层设计方法,比如在顶层设计的OOC (outside of the context )综合逻辑模块。您可以选择特定的模块,或设计层次结构的级别,并将它们合成为OOC。可以应用模块级约束来优化和验证模块性能。然后在实现期间应用模块设计检查点(DCP)来构建顶级网络列表。该方法有助于减少顶层合成运行时间,并消除对已完成模块的重新合成。

508

508

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?