目录

flechazo![]() https://www.zhihu.com/people/jiu_sheng

https://www.zhihu.com/people/jiu_sheng

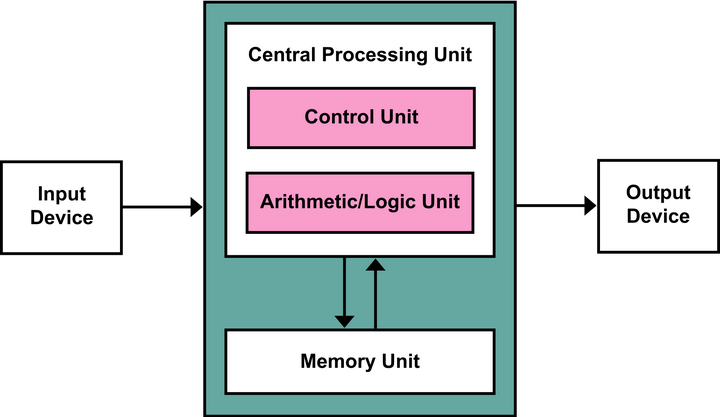

嵌入式操作系统硬件架构的核心是处理器Central Processing Unit,CPU,负责从内存中取出指令,解码确定类型和操作数后再执行该指令。

冯诺依曼结构

添加图片注释,不超过 140 字(可选)

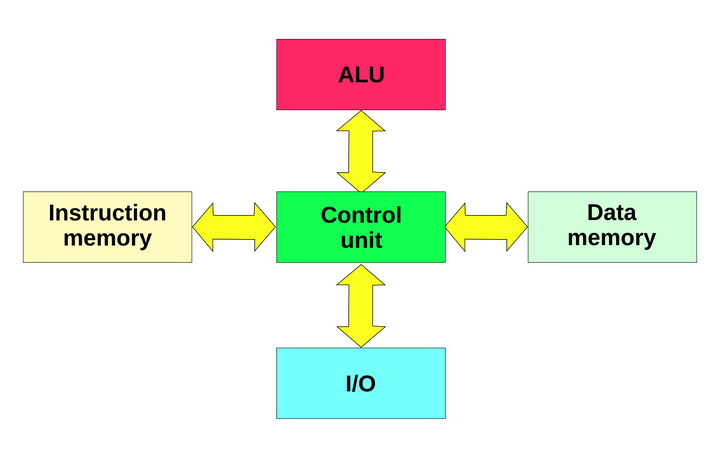

哈佛结构

每个CPU都有其一套可执行的专门指令集。

复杂指令集Complex Instrunction Set Computer , CISC

精简指令集Reduced Instrunction Set Computer , RISC

| 条目 | CISC | RISC |

|---|---|---|

| 价格 | 由硬件完成部分软件功能,硬件复杂性增加,芯片成本高 | 由软件部分完成部分硬件功能,软件复杂性增加,芯片成本低 |

| 性能 | 减少代码尺寸,增加指令的执行周期数 | 使用流水线降低指令的执行周期数,增加代码尺寸 |

| 指令集 | 指令系统复杂,指令数目多大200~3000条 | 只设置使用频度高的一些简单指令,复杂指令的功能由多条简单指令组合而实现 |

| 高级语言支持 | 硬件完成 | 软件完成 |

| 寻址方式 | 较多 | 种类较少 |

| 控制器 | 大多采取微程序控制器实现 | 用硬件实现,采用组合逻辑控制器 |

| 寄存器数量 | 通用寄存器较少 | 大量的通用寄存器 |

在实际使用中,人们发现:典型程序中80%的语句仅使用到指令系统中20%的指令,而且使用频率较高的指令都是简单的基本指令。

复杂指令的设计更为复杂,使得其执行速度受限。

精简指令集计算机RISC,其设计特点是简化指令集,只设置使用频度高的一些指令,复杂指令功能由多条简单指令组合来实现。

在嵌入式系统中,通过访问内存得到的指令或者数据的时间远大于CPU执行指令所花费的时间。因此在CPU内部都有一些用来保存关键变量和临时数据的寄存器。

-

通用寄存器组

-

以Intel 8086CPU为例,其内部包含8个16位通用寄存器

-

通用数据寄存器AX、BX、CX、DX。

-

基址寄存器BX、BP。

-

寄存器间接、变址寻址功能SI、DI。

-

堆栈指针SP

-

运算器

-

Arithmetic&logic Unit ALU算数逻辑单元

-

可以完成各种算数和逻辑运算,同时配合ALU工作的有暂存器。

-

控制器

-

构成CPU的另一个重要部件,主要有一下几种:

-

程序计数器(Program Counter,PC),存放着下一条需要执行指令的内存地址。

-

程序状态字(Program Status Word,PSW),存放着指令执行结果状态及一些特定标志,例如溢出标志OF、进位标志CF等。

-

指令寄存器(Instruction Register,IR),存放当前执行指令。

-

时序部件,用于产生所需时序信号。

随着计算机的发展,现有CPU内部还集成了高速缓存(Cache)、流水线等部件。

一、嵌入式微处理器的结构和类型

1、8位、16位、32位处理器的体系结构特点

-

常用8位处理器的体系结构特点

-

使用8位数据总线的微处理器。可以通过多重内存存取的方式来处理更多的数据。

-

大部分的8位微处理器有16位的地址总线,能访问64KB的地址空间。

-

低成本、可扩充内存及接口设备等特点,目前仍然在嵌入式系统领域得到广泛的应用。

-

8051

-

-

常用16位处理器的体系结构特点

-

内部总线宽度为16的微处理器。

-

目前主要应用于便携式设备、工业控制及智能仪器仪表等。

-

-

常用32位处理器的体系结构特点

-

32位的地址和数据总线,其地址空间达到了4GB。

-

ARM。是一种RISC体系结构的微处理器

-

在每条数据处理指令当中,都控制算术逻辑单元ALU和移位器,以使ALU和移位器获得最大的利用率。

-

自动递增和自动寻址模式,以优化程序中的循环。

-

同时执行Load和Store多条指令,以增加数据吞吐量。

-

所有指令都可以条件执行,以执行吞吐量。

-

-

ARM的数据类型:

-

字(Word):在ARM体系结构中,字的长度为32位,而在8位/16位处理器体系结构中,子的长度一般为16位。

-

半字(Half-Word)

-

字节(Byte):8位

-

-

ARM微处理器支持7种运行模式

-

用户模式(USR)

-

快速中断模式(FIQ)

-

外部中断模式(IRQ)

-

管理模式(SVC)

-

数据访问终止模式(ABT)

-

系统模式(SYS)

-

定义指令中止模式(UND)

-

-

MIPS处理器

-

PowerPC有三个级别

-

Book I用户指令集体系结构

-

Book II虚拟环境体系结构

-

Book III操作环境体系结构

-

2、DSP处理器的体系结构特点

Digital Signal Process (DSP)。数字信号处理器,内部采用程序和数据分开的哈佛结构,具有专门的硬件乘法器,广泛用于流水线操作,提供特殊的指令,可以用来快速地实现各种数字信号的处理算法。有一下特征:

-

在一个指令周期内可完成一次乘法和一次加法。

-

程序和数据空间分开,可以同时访问指令和数据。

-

片内具有快速RAM,通常可通过独立的数据总线在两块中同时访问。

-

具有低开销或无开销循环及跳转的硬件支持。

-

快速的中断处理和硬件I/O支持。

-

具有在单周期内操作的多个硬件地址产生器。

-

可以并行执行多个操作。

-

支持流水线操作,使取指、译码和执行可以重叠执行。

DSP的其他通用功能较弱。功耗较小。

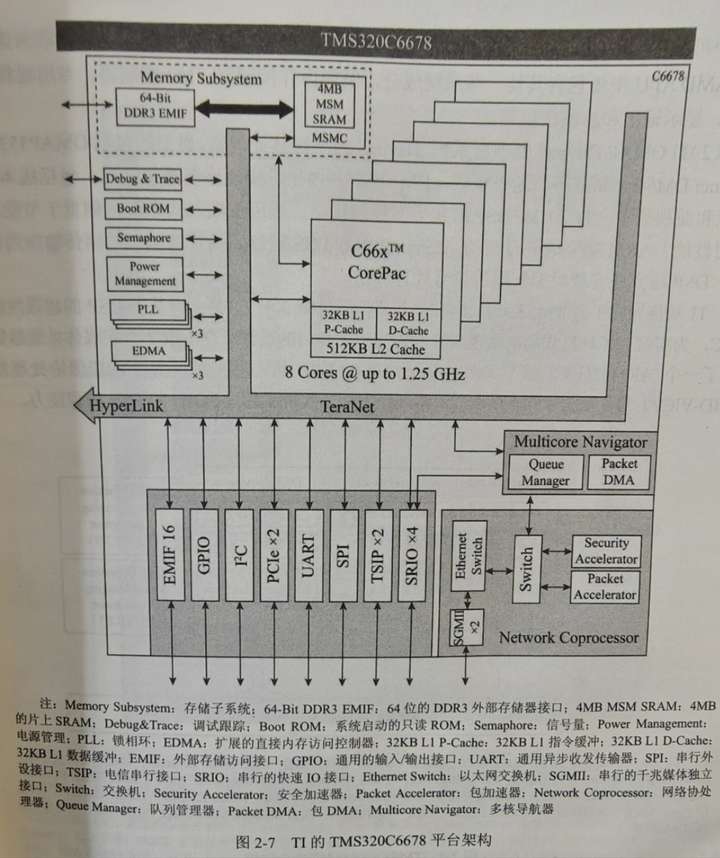

3、多核处理器的体系结构特点

同构多核:内核相同、地位对等。反之为异构多核。

-

同构多核处理器

-

Intel酷睿架构处理器

-

TI keystone架构

-

添加图片注释,不超过 140 字(可选)

-

异构多核处理器

-

AMD独显

-

TI OMAP/Davinci处理器系列

-

添加图片注释,不超过 140 字(可选)

-

Xilinx Zynq处理器

添加图片注释,不超过 140 字(可选)

二、嵌入式微处理器的异常与中断

1、异常

异常是一种形式的异常控制流,它的一部分是由应硬件实现的,一部分由操作系统实现。

异常可分为四类:

| 类别 | 原因 | 异步/同步 | 返回行为 |

|---|---|---|---|

| 中断(interrupt) | 来自I/O设备的信号 | 异步 | 总是返回到下一条指令 |

| 陷阱(trap) | 有意的异常 | 同步 | 总是返回到下一条指令 |

| 故障(fault) | 潜在可恢复的错误 | 同步 | 可能返回到当前指令 |

| 中止(abort) | 不可恢复的错误 | 同步 | 不会返回 |

2、中断

中断是异步的。

-

硬中断和软中断

-

硬中断是由硬件产生的

-

软中断,软中断不会被另一个软中断抢占,可以被硬中断抢占。

-

可屏蔽中断与不可屏蔽中断

-

INTR Interrupt Require

-

NMI Non Maskable Interrupr

-

中断优先级

-

查询优先级

-

执行优先级

-

中断控制器能对中断进行排队管理,同时支持不同优先级的配置,使得高优先级能够中断低优先级中断。

-

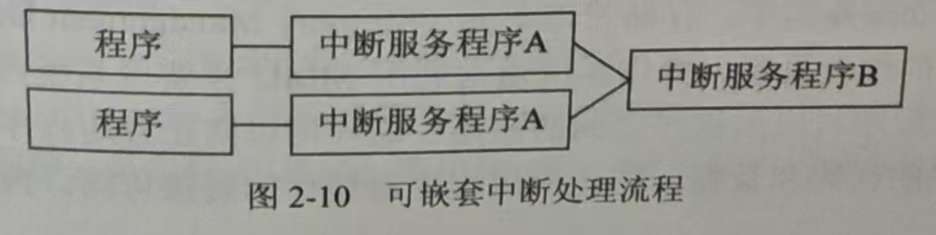

中断嵌套

添加图片注释,不超过 140 字(可选)

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?