目录

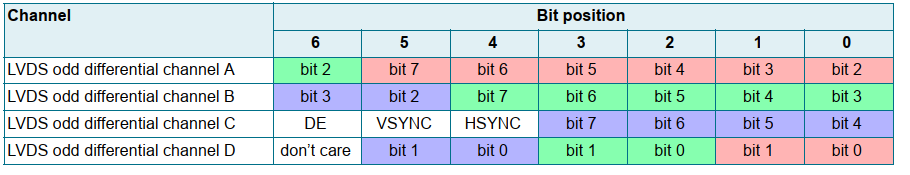

LVDS single bus, 24 bpp, VESA data packing

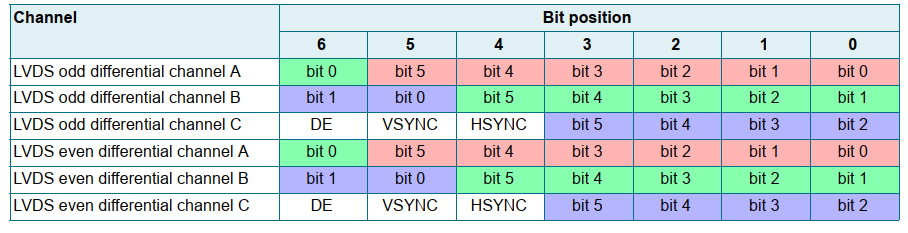

LVDS single bus, 24 bpp, JEIDA data packing

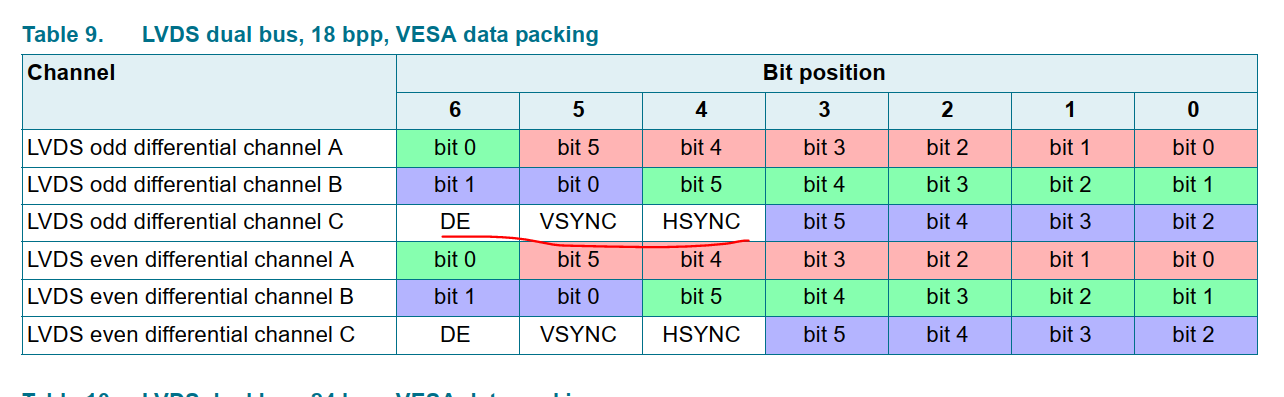

LVDS dual bus, 18 bpp, VESA data packing

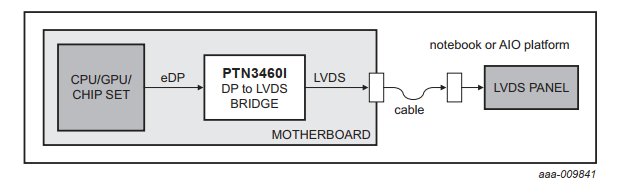

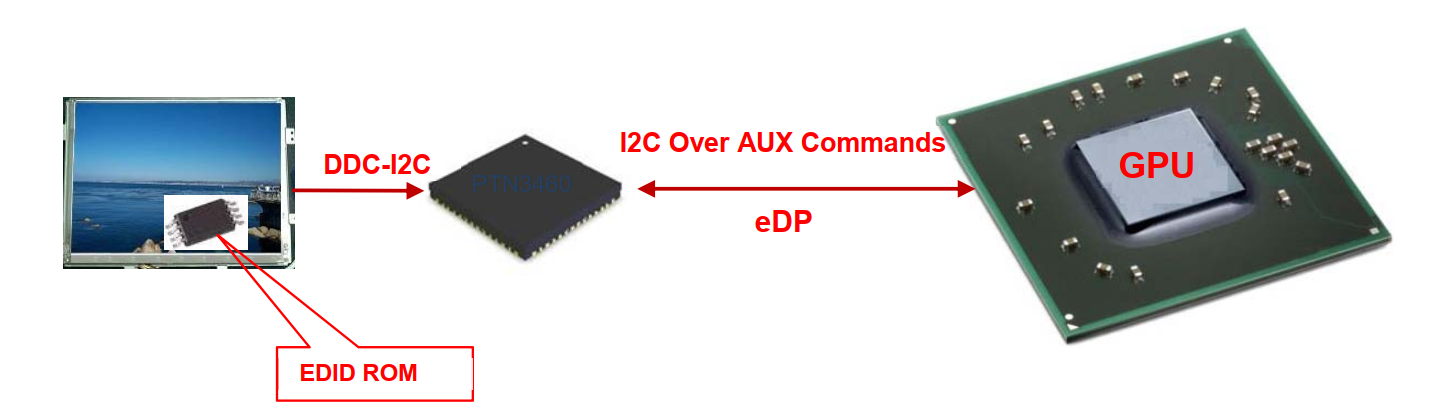

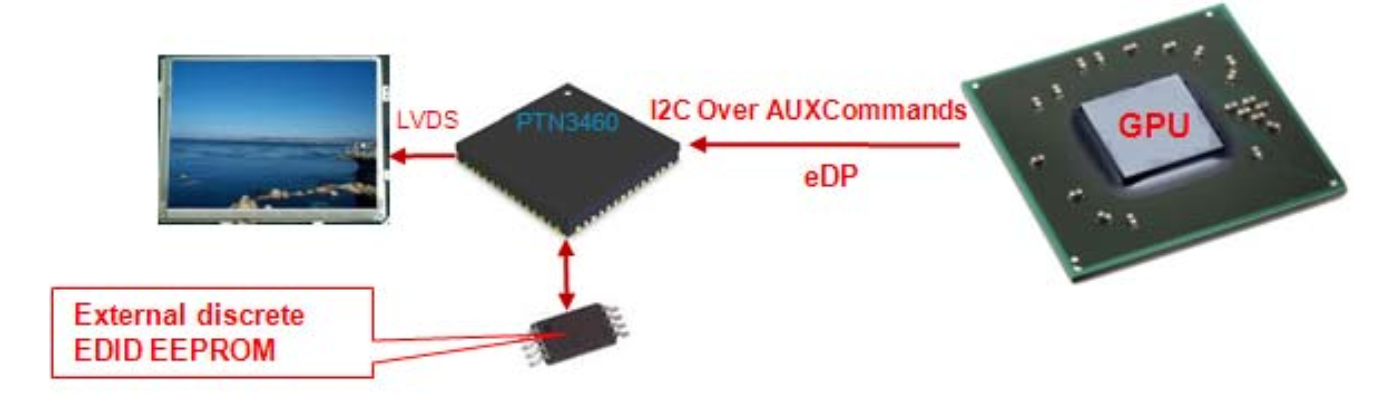

通过edp口输出,经过edp到lvds,而后到lvds屏幕的历程。

EDP控制器的管脚定义

背光控制

eDP_VDDEN

eDP_VDDEN 输出 主 eDP/MIPI 面板电源使能:面板电源控制使能。此信号用于控制面板逻辑电路的直流电压源。

这是面板本身的核心电源开关。它控制供给屏幕主控逻辑芯片、时序控制器(T-CON)、栅极驱动器等核心元件的电力。

eDP_BKLTEN

eDP_BKLTEN 输出 主 eDP/MIPI 背光使能:用于 eDP/MIPI 的面板背光使能控制。此信号用于门控(导通或关断)通向背光电路的电源。

背光电源的开关。它专门控制是否给屏幕背后的LED灯珠(背光)供电

eDP_BKLTCTL

eDP_BKLTCTL 输出 主 eDP/MIPI 面板背光亮度控制:用于 eDP/MIPI 的面板亮度控制。此信号用作 PWM(脉冲宽度调制)时钟输入信号。

背光亮度的调节器。通过PWM来精确控制背光的明暗程度。

PTN3460I管脚定义

配置管脚

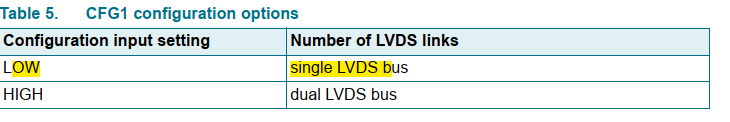

CFG1

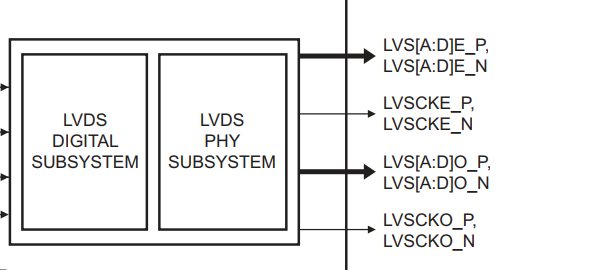

E_P O_P代表奇偶两路LVDS,可以接两个屏,每路可以配置为4lane 24bpp或者3lane 18 bpp。

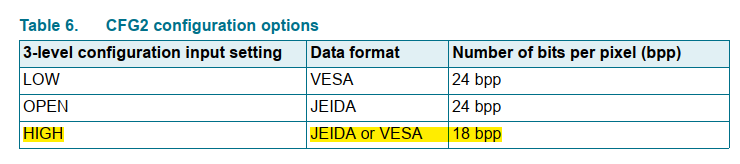

CFG2

此处配置为18bpp ,单LVDS链接。

有时在高低温环境中,采用24bpp会闪屏,可以修改为18bpp。

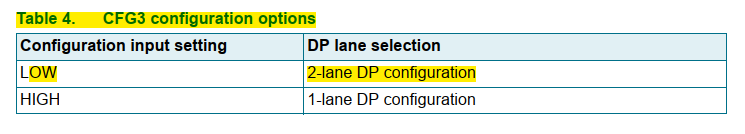

CFG3

此处配置为2 lane DP

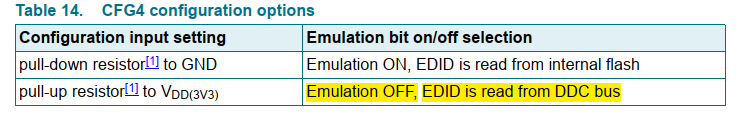

CFG4

这个管脚比较有意思。控制EDID信息的来源。

1)当配置为OFF时,直接从屏获取EDID 信息,图示如下:

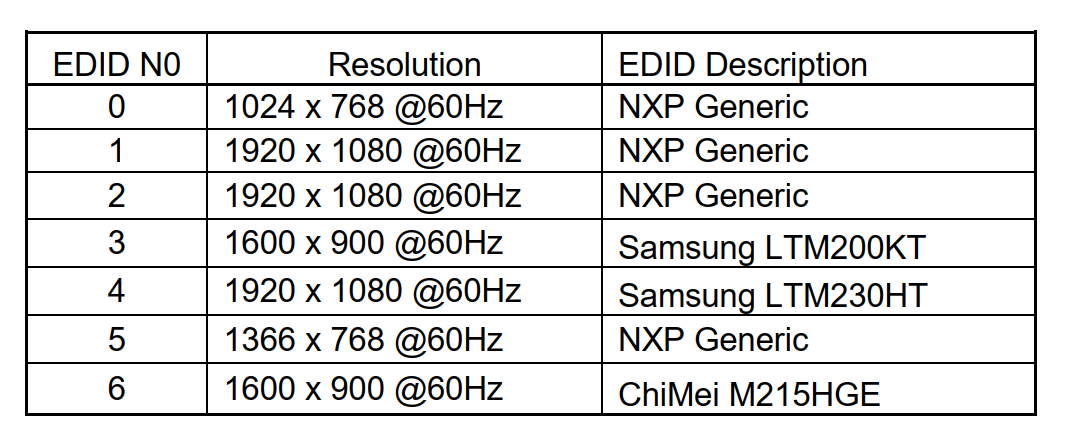

2)假设我们怀疑屏的EDID有问题,我们可以将此配置为ON,即从芯片内部flash获取EDID,内部有7组EDID信息。

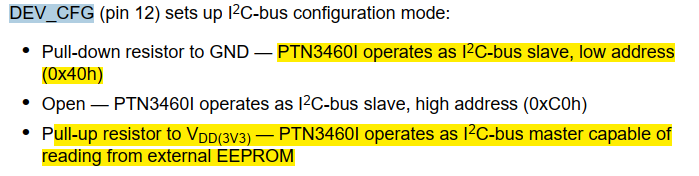

DEV_CFG

此管脚主要配置设备上I2C作为主或者从。

I2C作为主时,芯片初始化时从EEPROM中读取一个EDID和128字节的配置信息。

这种情况下,用户可以将EDID写入到EEPROM中,但只支持一个。可以覆盖上述7个EDID中的第一个。

I2C作为主时,CPU/GPU就不能通过I2C通道访问3460进行配置。

I2C为从时,屏的背光控制,可以由3460控制。通过I2C 写芯片的配置寄存器。此外还可以控制lvds的信号幅度等。

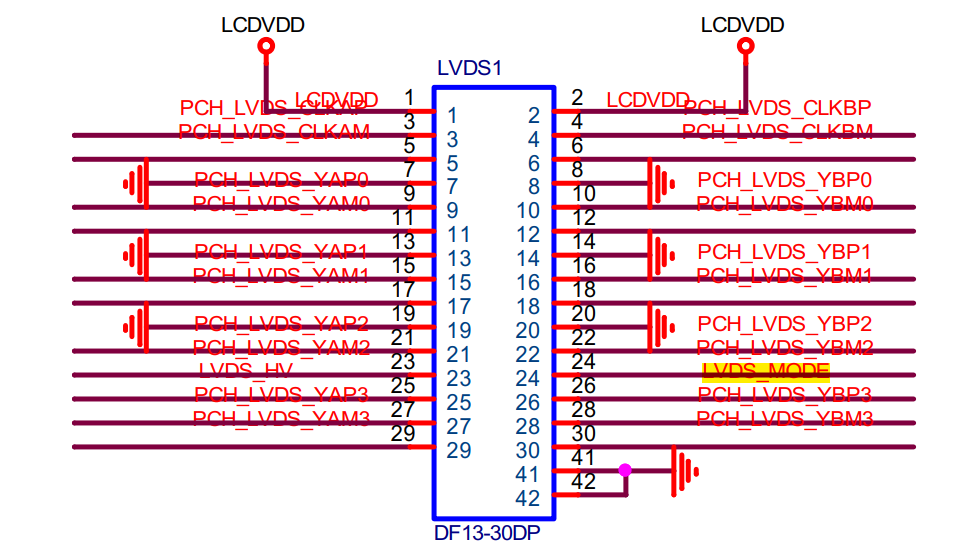

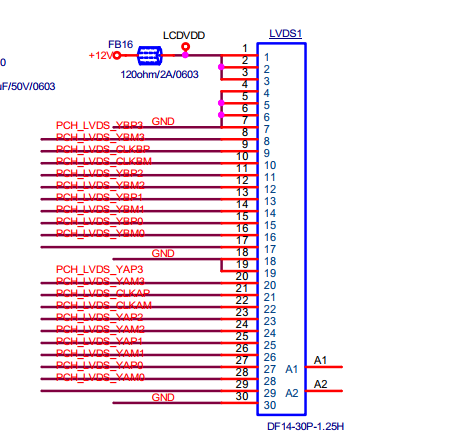

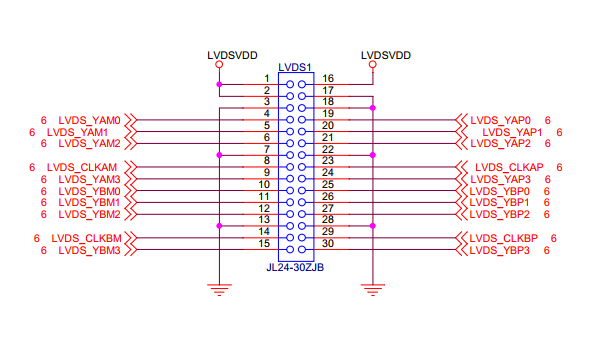

LVDS屏的管脚定义

以两款屏为例 M121GNX2 R1和TCG104XGLPAPNN-AN40-S

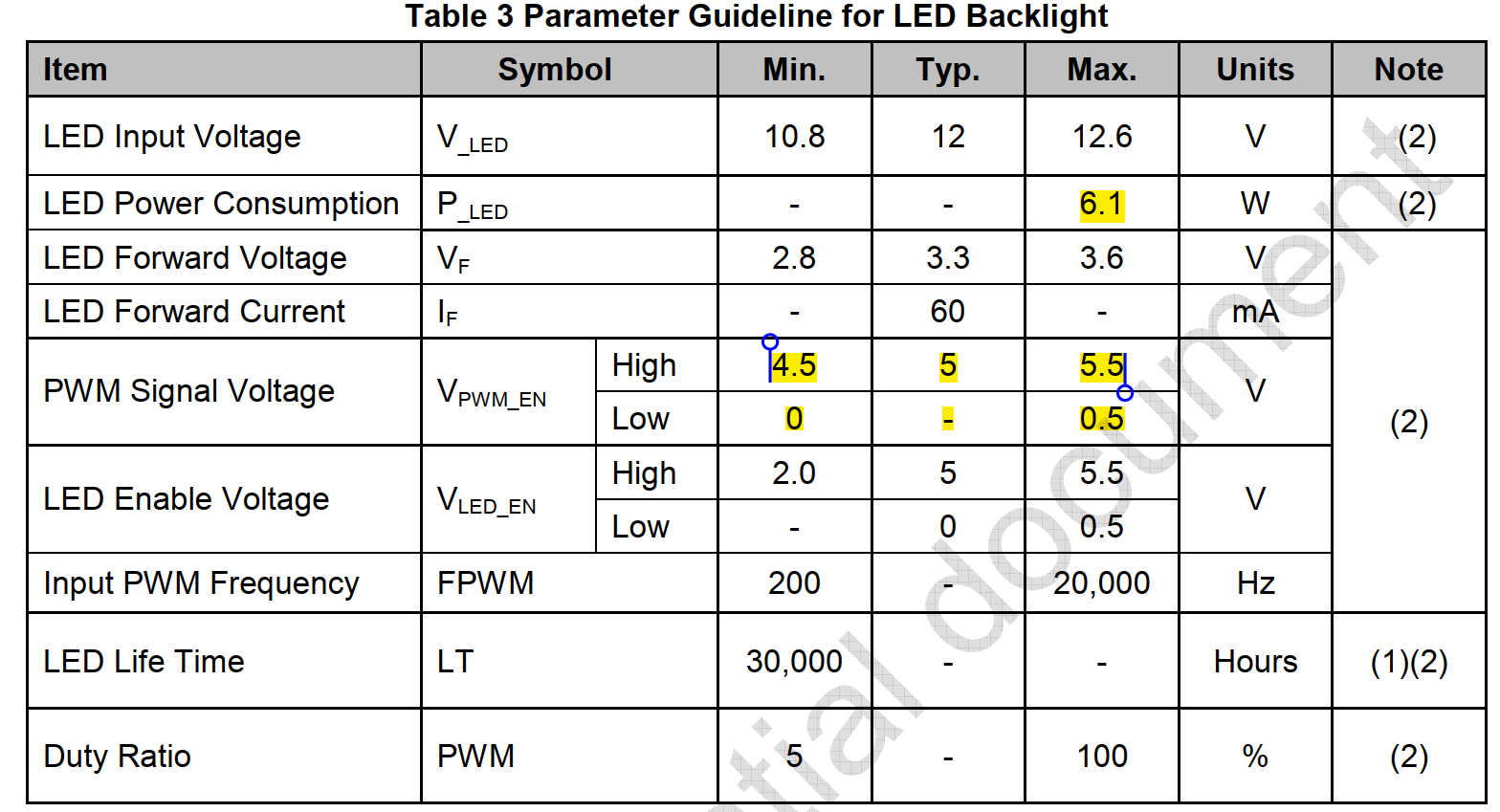

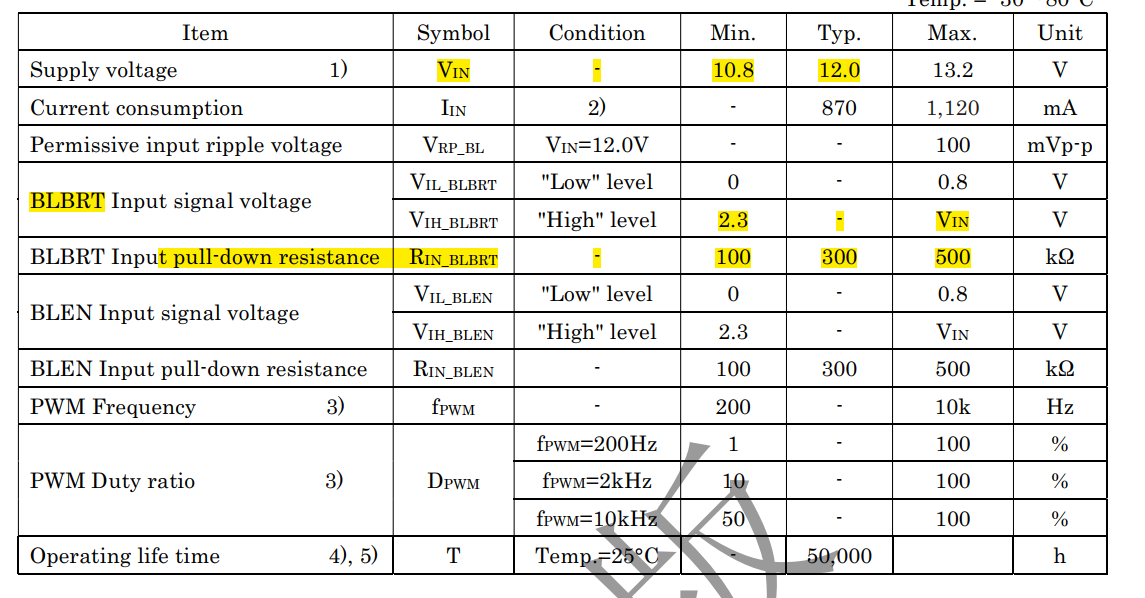

背光控制

注意上述两个PWM的工作电压不同。对于高电平,第一个屏定为4.5-5.5;第二个定义为2.3-Vin。假设GPU侧给出的PWM高电平为3.3,则对于第一个屏幕,其亮度调节功能是缺失的。

mode信号

![]()

控制位数,此处需要和3460I的配置一致。实际上3460I只支持6bit。

数据线接地强制

M121GNX2 R1 没有明确要求

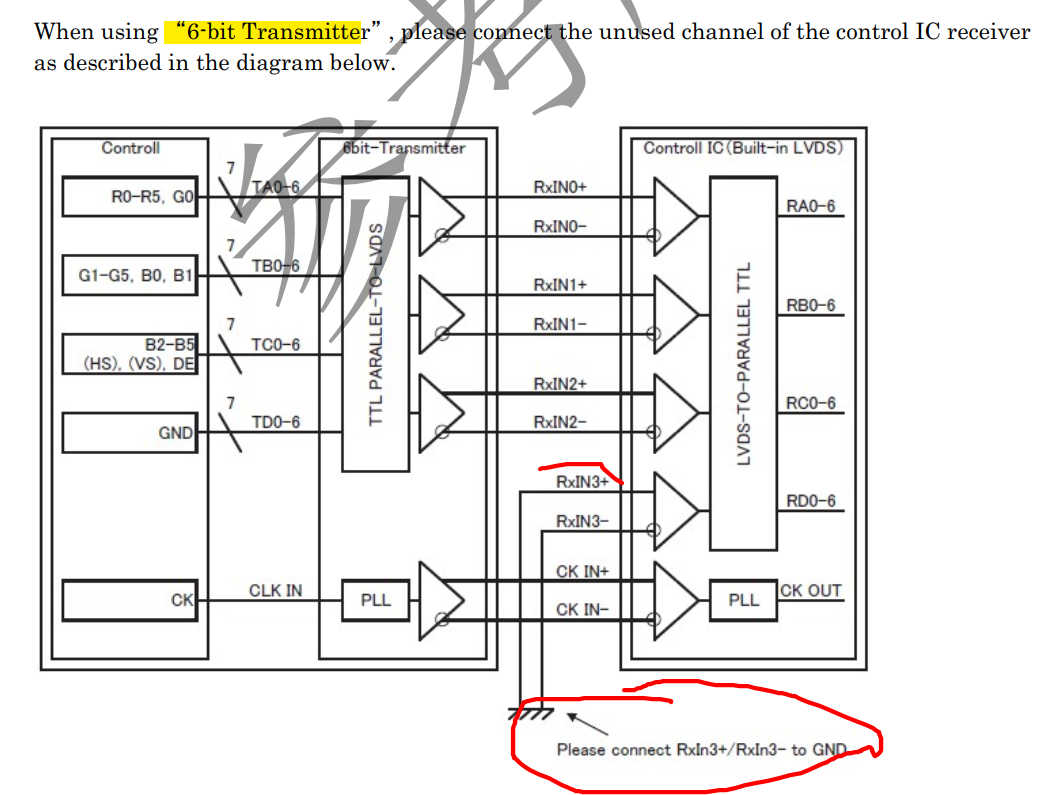

TCG104XGLPAPNN-AN40-S 屏当采用6位模式时,屏链接器的最后一组差分要求接地。

数据格式

两种格式VESA和JEIDA

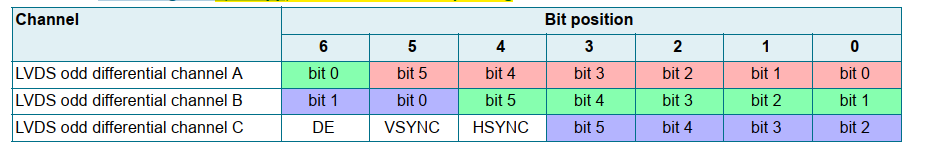

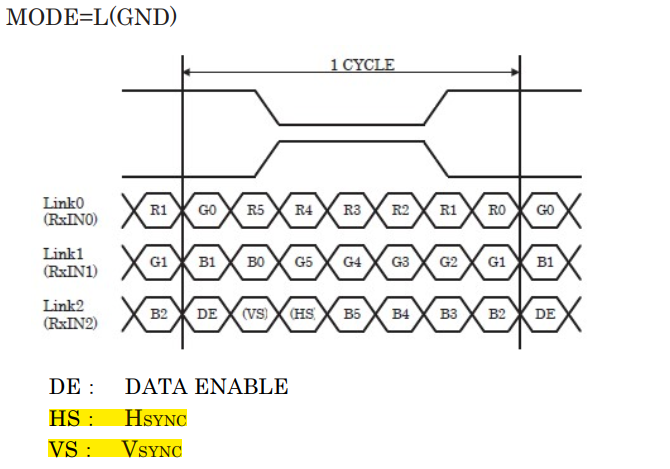

LVDS single bus, 18 bpp

两种数据格式一致

即RGB各6bit,依次顺序传递。而后是同步和数据使能信号

LVDS single bus, 24 bpp, VESA data packing

即8bit数据,每个颜色最后的两位在ch D上传输

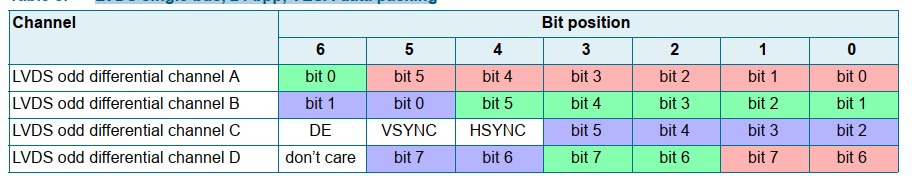

LVDS single bus, 24 bpp, JEIDA data packing

即8bit数据,每个颜色开始的两位在ch D上传输

LVDS dual bus, 18 bpp, VESA data packing

即单通道的双倍扩展,每个通道数据顺序一致。JEIDA与此一致。

屏的数据格式

6bit

屏与3460一致性检查

1)屏链接器,20pin,6bit or 8bit选择在19 pin。要确认此链接器管脚的实际配置。尤其单板设计出的链接器为30pin时

2)3460 CFG2 配置

3) 当为6bit时,屏对最后一组差分数据的链接要求

自己

未知

故障

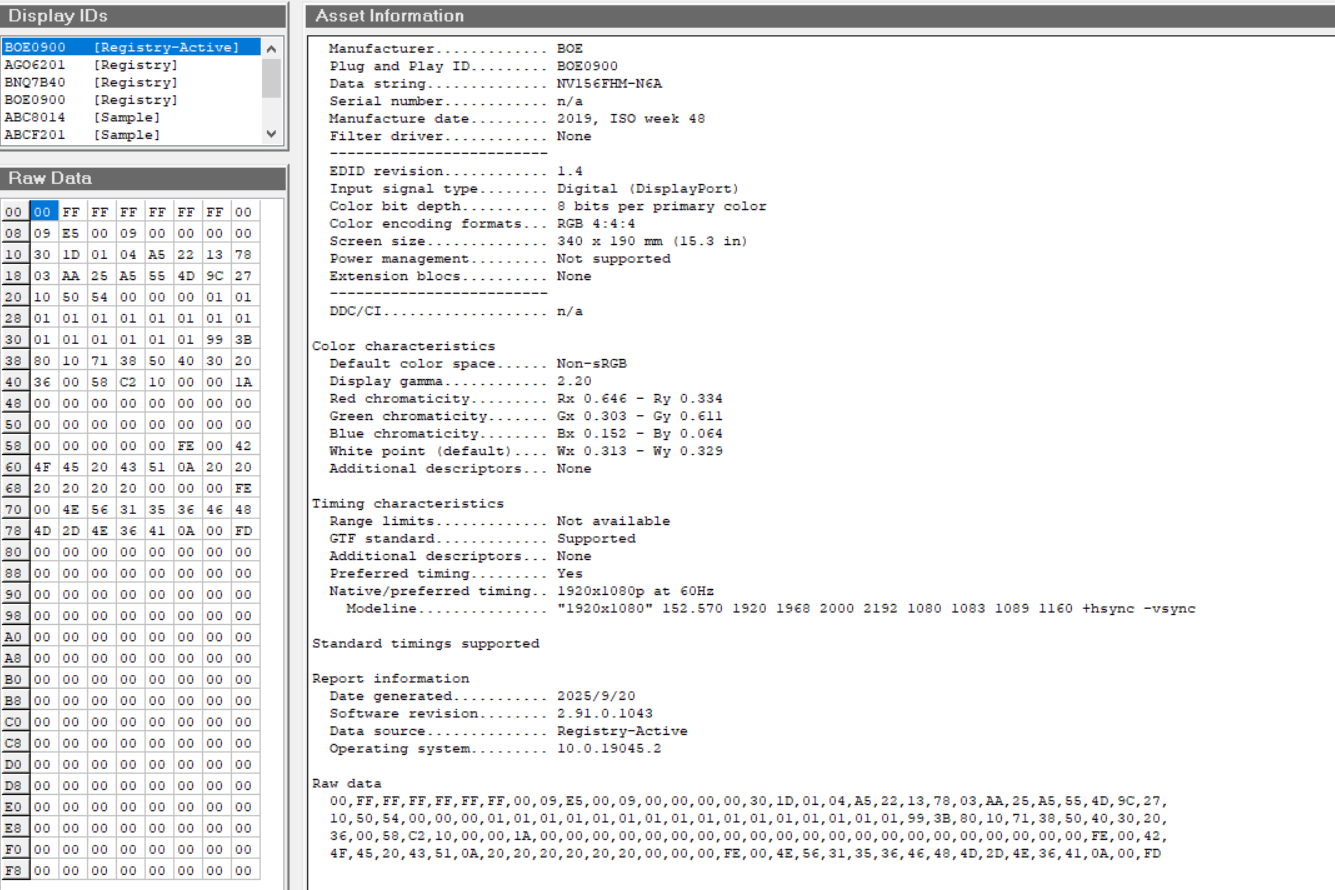

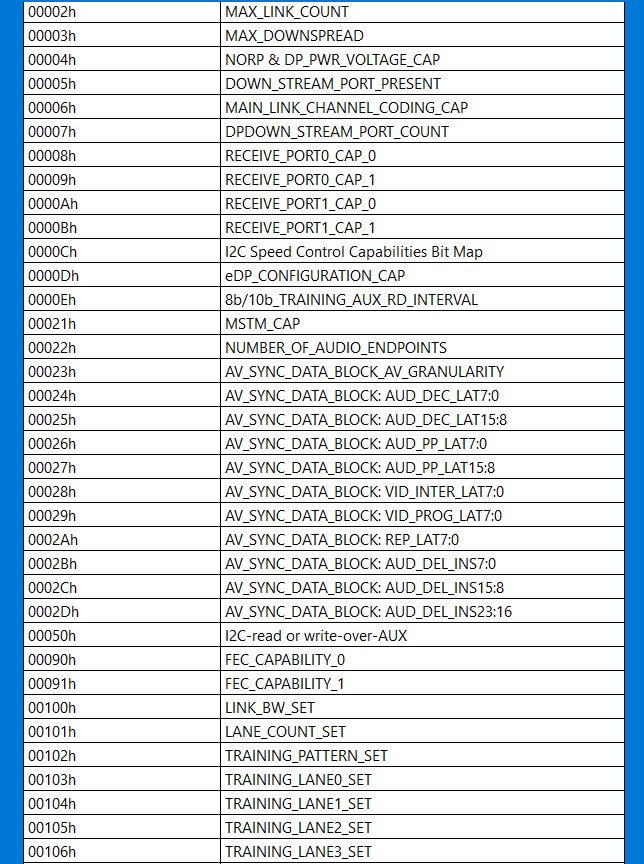

windows获取EDID DPCD的工具

EDID获取-moninfo

https://www.entechtaiwan.com/util/moninfo.shtm

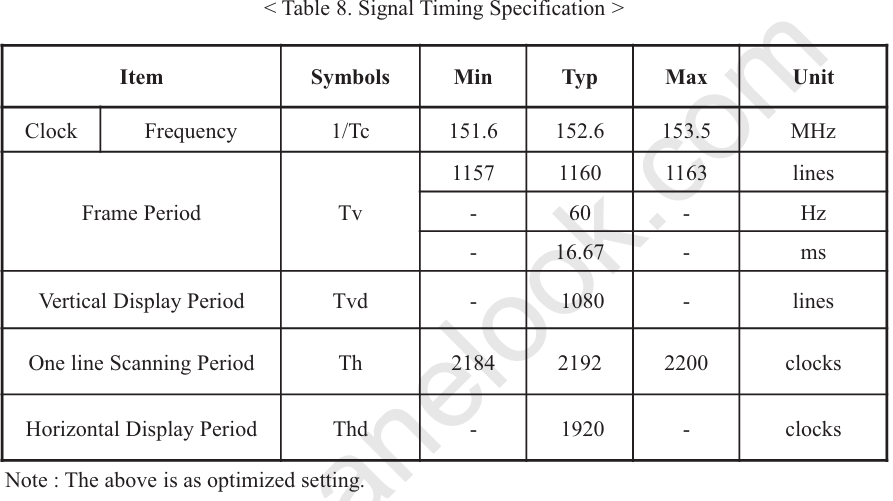

如下是手册资料,并未细分每行。

-

"1920x1080": 该模型行的名称。 -

152.570: 像素时钟(Pixel Clock),单位是MHz(这里是152.570 MHz)。这决定了数据传输的速度。 -

水平时序(Horizontal Timing):

-

1920: 水平有效像素(Hdisp) - 可见图像的水平像素数(即分辨率宽度)。 -

1968: 水平同步开始(Hsync start) - 从一行开始到水平同步脉冲开始之间的像素数。 -

2000: 水平同步结束(Hsync end) - 从一行开始到水平同步脉冲结束之间的像素数。2000 - 1968 = 32,即水平同步脉冲宽度为32像素。 -

2192: 水平总数(Htotal) - 一行的总像素数(包括可见和不可见的消隐期)。2192 - 1920 = 272,即水平消隐区域总共为272像素

-

|<--------------- 一行总时间 (2192 pixels) --------------->| | | |<- 可见图像 ->|<-- 水平消隐期 (272 pixels) ----------->| | (1920 px) | | | | |<-后沿->|<--同步脉冲->|<- 前沿 ---->| | | (48 px) | (32 px) | (192 px) | | | (1968-1920) |(2000-1968)| (2192-2000)|

-

起点 (0): 开始绘制像素1。

-

点 (1920): 可见像素绘制完毕,开始水平后沿(Blank)。

-

点 (1968): 后沿结束,水平同步脉冲开始 (

+hsync变为高电平)。 -

点 (2000): 同步脉冲结束 (

+hsync恢复低电平),开始水平前沿(Blank)。 -

点 (2192): 前沿结束,整行结束,电子枪移动到下一行的最左边,开始绘制新的一行。

-

垂直时序(Vertical Timing):

-

1080: 垂直有效行数(Vdisp) - 可见图像的垂直行数(即分辨率高度)。 -

1083: 垂直同步开始(Vsync start) - 从一帧开始到垂直同步脉冲开始之间的行数。 -

1089: 垂直同步结束(Vsync end) - 从一帧开始到垂直同步脉冲结束之间的行数。1089 - 1083 = 6,即垂直同步脉冲宽度为6行。 -

1160: 垂直总数(Vtotal) - 一帧的总行数(包括可见和不可见的消隐期)。1160 - 1080 = 80,即垂直消隐区域总共为80行。

-

|<------------------- 一帧总时间 (1160 lines) ------------------>| | | |<- 可见图像 ->|<--- 垂直消隐期 (80 lines) ---------------->| | (1080 lines) | | | | |<-后沿->|<-同步脉冲->|<- ---- 前沿 ---- ->| | | (3 ln) | (6 ln) | (71 ln) | | |(1083-1080)|(1089-1083)| (1160-1089) |

-

起点 (0): 开始绘制第1行。

-

点 (1080): 所有可见行绘制完毕,开始垂直后沿(Blank)。

-

点 (1083): 后沿结束,垂直同步脉冲开始 (

-vsync变为低电平)。 -

点 (1089): 同步脉冲结束 (

-vsync恢复高电平),开始垂直前沿(Blank)。 -

点 (1160): 前沿结束,整帧结束,电子枪移动到屏幕左上角,开始绘制新的一帧。

DPCD DPAUXTranslatorTool

依赖 windowsdesktop-runtime-6.0.36-win-x64

总结

1)背光的控制即可来自GPU/CPU; 也可以来自3460,来自3460要单独做兼容性的I2C控制。

各个屏的背光控制工作电压有差异,很容易造成不兼容设计。

2)EDID即可以来自3460,也可以来自屏幕。来自3460时,有默认值,也可以由EEPROM进行配置。 此处我们可以修改管脚,采用3460的EDID进行验证。

3)数据位宽,即6bit还是8bit。 屏幕有管脚配置,需要确认此管脚的电平状态。

4) 数据差分线的链接。有些屏,在采用6bit时,需要将最后一组差分线接地。

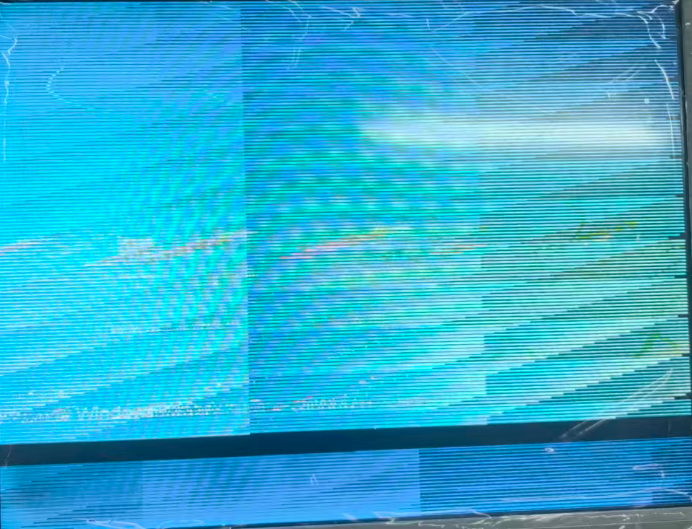

如果 3) 4) 没有按照设计要求做,在屏幕获取数据时,是否会异常呢?例如mode管脚悬空,导致有时候为低 ,有时为高,而3460一直按照6bit输出,这样当屏感知为8bit时,会读取到无效数据显示。

windows 通用VGA的驱动不支持背光调节。而intel 的驱动支持背光。intel的驱动除了背光,是否还会主动配置3460?

参考

AN11128 PTN3460 Programming Guide

PTN3460 Product data sheet

3570

3570

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?