实验要求:编写一个4-16的译码器,编译,和3-8译码器对比资源开销,看RTL View

3_8译码器(已知代码)

// module decoder3_8, 4 input priority encoder with zero input check

module decoder3_8(

IN , // input

OUT ); // output

input [2:0] IN;

output[7:0] OUT;

reg [7:0] OUT;

// get the OUT

always @ (IN)

begin ,

case(IN)

3'b000: OUT = 8'b0000_0001;

3'b001: OUT = 8'b0000_0010;

3'b010: OUT = 8'b0000_0100;

3'b011: OUT = 8'b0000_1000;

3'b100: OUT = 8'b0001_0000;

3'b101: OUT = 8'b0010_0000;

3'b110: OUT = 8'b0100_0000;

3'b111: OUT = 8'b1000_0000;

// full case 不需要写default,否则一定要有default

endcase

end

endmodule

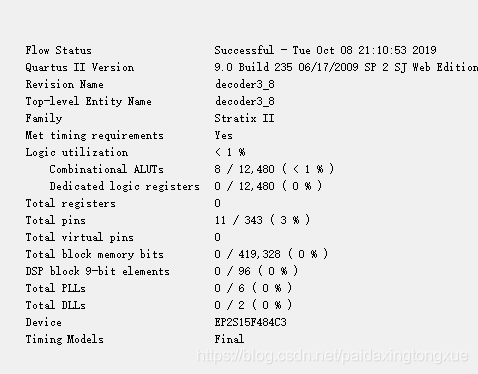

3_8译码器资源消耗图

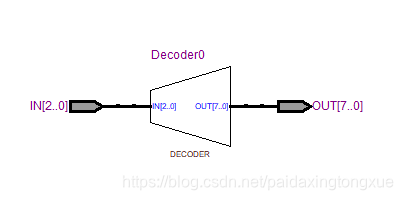

3_8译码器RTL View

4_16译码器(仿写3_8译码器代码)

module decoder4_16(IN,OUT);

input [3:0] IN;

output[15:0] OUT;

reg [15:0] OUT;

always @ (IN)

begin

case(IN)

3'b0000: OUT = 8'b0000_0000_0000_0001;

3'b0001: OUT = 8'b0000_0000_0000_0010;

3'b0010: OUT = 8'b0000_0000_0000_0100;

3'b0011: OUT = 8'b0000_0000_0000_1000;

3'b0100: OUT = 8'b0000_0000_0001_0000;

3'b0101: OUT = 8'b0000_0000_0010_0000;

3'b0110: OUT = 8'b0000_0000_0100_0000;

3'b0111: OUT = 8'b0000_0000_1000_0000;

3'b1000: OUT = 8'b0000_0001_0000_0000;

3'b1001: OUT = 8'b0000_0010_0000_0000;

3'b1010: OUT = 8'b0000_0100_0000_0000;

3'b1011: OUT = 8'b0000_1000_0000_0000;

3'b1100: OUT = 8'b0001_0000_0000_0000;

3'b1101: OUT = 8'b0010_0000_0000_0000;

3'b0110: OUT = 8'b0100_0000_0000_0000;

3'b0111: OUT = 8'b1000_0000_0000_0000;

endcase

end

endmodule

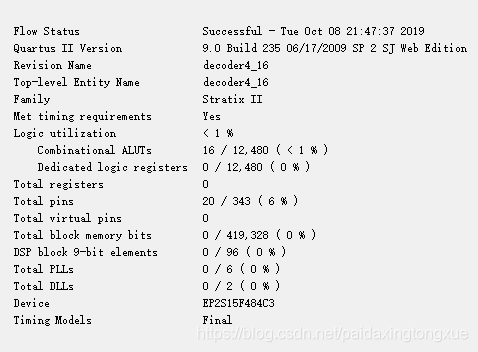

4_16译码器资源消耗图

将两者的资源消耗图做对比会发现4-16译码器的资源消耗约是3-8译码器的2倍。

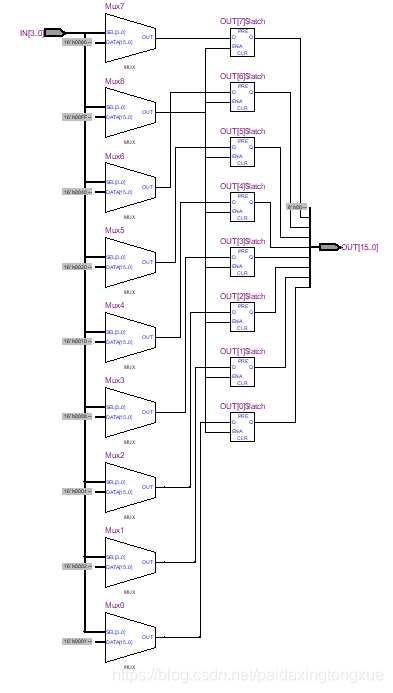

4_16译码器RTL View

本文详细介绍了如何设计一个4-16的译码器,并通过与3-8译码器的资源消耗对比,揭示了译码器规模扩大带来的资源需求增加。通过Verilog代码实现,展示了不同规模译码器的设计方法。

本文详细介绍了如何设计一个4-16的译码器,并通过与3-8译码器的资源消耗对比,揭示了译码器规模扩大带来的资源需求增加。通过Verilog代码实现,展示了不同规模译码器的设计方法。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?