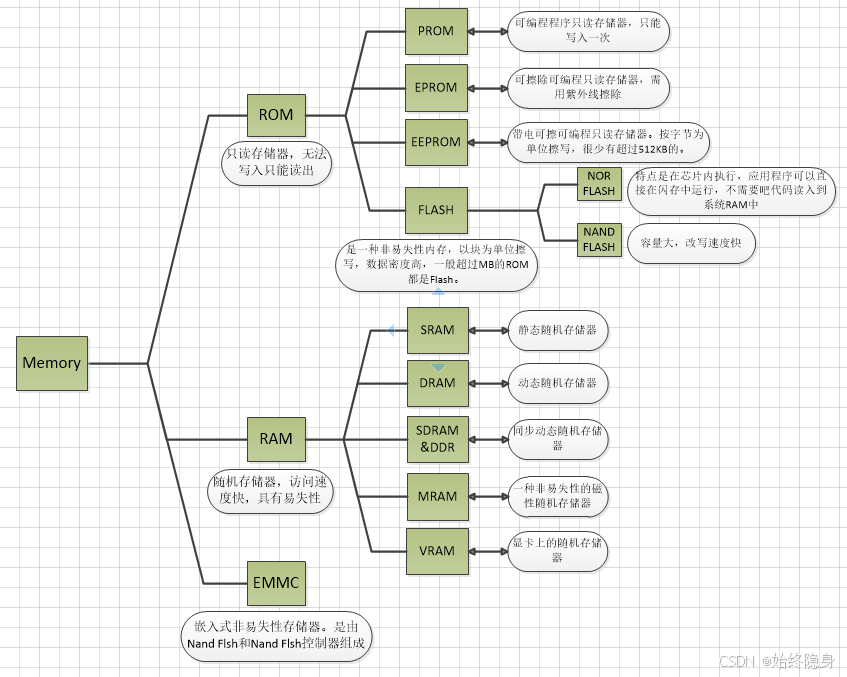

一、Memory的分类

Memory的分类

二、ROM

1、简介

只读存储器(Read-Only Memory,ROM)以非破坏性读出方式工作,只能读出无法写入信息。信息一旦写入后就固定下来,即使切断电源,信息也不会丢失,所以又称为固定存储器。ROM所存数据通常是装入整机前写入的,整机工作过程中只能读出,不像随机存储器能快速方便地改写存储内容。ROM所存数据稳定 ,断电后所存数据也不会改变,并且结构较简单,使用方便,因而常用于存储各种固定程序和数据。除少数种类的只读存储器(如字符发生器)可通用之外,不同种类的只读存储器功能不同。为ROM应用广泛,诸如Apple II或IBM PC XT/AT等早期个人电脑的开机程序(操作系统)或是其他各种微电脑系统中的轫体(Firmware),所使用的硬件都是ROM。

ROM主要由地址译码器、存储器、读出线和读出放大器等部分组成。ROM是按地址寻址的存储器,由CPU给出要访问的存储单元地址ROM的地址译码器是与门的组合,输出是全部地址输入的最小项(全译码)。

2、工作过程

ROM的工作过程,CPU经地址总线送来要访问的存储单元地址,地址译码器根据输入地址码选择某条字线,然后由它驱动该字线的各位线,读出该字的各存储位元所存储的二进制代码,送入读出线输出,再经数据线送至CPU。

3、分类

(1)MROM:掩膜编程的只读存储器;由厂家再制作工艺过程中将数据写入,存储内容固定,掉点后数据仍存在,可靠性高,制作成本低,但是这种存储器一旦由生产厂家制造完毕,用户就无法修改。

(2)PROM:可编程只读存储器;允许用户通过专用的设备(编程器)一次性写入自己所需要的信息,其一般可编程一次,需要用电和光照的方法来编写与存放的程序和信息,但仅仅只能编写一次,第一次写入的信息就被永久性地保存起来。

(3)EPROM:可编程可擦除只读存储器;是一种以读为主的可写可读的存储器,一种便于用户根据需要来写入,并能把已写入的内容擦去后再改写的ROM,其存储的信息可以由用户自行加电编写,也可以利用紫外线光源或脉冲电流等方法先将原存的信息擦除,然后用写入器重新写入新的信息。 EPROM比MROM和PROM更方便、灵活、经济实惠。但是EPROM采用MOS管,速度较慢。

(4)EEPROM:电可擦可编程只读存储器;是一种随时可写入而无须擦除原先内容的存储器,其写操作比读操作时间要长得多,EEPROM把不易丢失数据和修改灵活的优点组合起来,修改时只需使用普通的控制、地址和数据总线。

(5)Flash:快擦除读写存储器;是一种高密度、非易失性的读/写半导体存储器;它既有EEPROM的特点,又有RAM的特点,是一种全新的存储结构,俗称快闪存储器。

(6)OTPROM:一次编程只读内存;编程写入之后就不再抹除。

三、RAM

1、简介

随机存储器也叫主存是与CPU直接交换数据的内部存储器。它可以随时读写(刷新时除外),而且速度很快,通常作为操作系统或其他正在运行中的程序的临时数据存储介质。RAM工作时可以随时从任何一个指定的地址写入(存入)或读出(取出)信息。它与ROM最大的区别是数据的易失性,即一旦断电后所存储的数据将随之丢失。RAM在计算机中用来暂时存储程序、数据和中间结果。

RAM有存储矩阵、地址译码器、读/写控制器、输入/输出、片选控制等组成。RAM既可以向指定单元存入信息又可以从指定单元读出信息。

RAM的应用场景:RAM在计算机和数字系统中用于暂时存储程序、数据和中间结果。由于其高速访问的特性,RAM常用于需要快速读写操作的场景,如操作程序、图形处理、游戏等。

2、特点

(1)随机存取:指当存储器中的数据被读取或写入时,所需要的时间与这段信息所在的位置或所写入的位置无关。相应的,读取或写入顺序访问存储设备中的信息时,其所需要的时间与位置就会有关系。它主要用来存放操作系统、各种应用程序、数据等。当RAM处于正常工作时,可以从RAM中读出数据,也可以往RAM中写入数据。

(2)易失性:当电源关闭时,RAM不能保留数据。如果需要保存数据,就必须把它们写入一个长期的存储设备中(例如硬盘)。RAM的工作特点是通电后,随时可在任意位置单元存取数据信息,断电后内部信息也随之消失。

(3)需要刷新:现代随机存取存储器依赖电容器存储数据。电容器充满电后代表1,未充电的代表0。由于电容器或多或少有漏电的情形,若不作特别处理,数据会渐渐随时间流失。刷新是指定期读取电容器的状态,然后按照原来的状态重新为电容器充电,弥补流失了的电荷。需要刷新正好解释了随机存储器的易失性。

(4) 对静电敏感:正如其他精细的集成电路,随机存取存储器对环境的静电荷非常敏感。静电会干扰存储器内电容器的电荷,引致数据流失,甚至烧坏电路。故此接触随机存取存储器前,应先用手触摸金属接地。

(5)访问速度:现代的随机存取存储器几乎是所有访问设备中写入和读取速度最快的,存取延迟和其他涉及机械运作的存储设备相比,也显得微不足道。

3、分类

(1)SRAM:静态存储单元是在静态触发器的基础上附加门控管而构成的。它是靠触发器的自保功能存储数据的。SRAM存放的信息在不停电的情况下能长时间保留,状态稳定,不需要外加刷新电路,从而简化了外部电路设计。优点是速度快、使用简单、不需要刷新、静态功耗低,常用作Cache。但是缺点是元件数多、集成度低、运行功耗大。常用的SRAM的有:6116(2K*8位),6264(8K*8位),62256(32K*8位),2114(1K*4位)。

(2)DRAM:动态随机存储器。利用电容存储电荷的原理保存信息,电路简单,急程度高。在大容量存储器中普遍使用。但缺点是需要刷新逻辑电路,且刷新操作时不能进行正常读/写操作。

DRAM的刷新操作不同于存储器读/写操作,主要表现在以下几点:

- 刷新地址由刷新地址计数器产生,不是由地址总线提供。

- DRAM基本存储电路可按行同时刷新,所以刷新只需要行地址,不需要列地址。

- 刷新操作时存储器芯片的数据线呈高阻状态,即片内数据线与外部数据线完全隔离。

四、FLASH

1、FLASH

Flash存储器,是内存的一种,是一种非易失性内存。

Flash存储器又称闪存,它结合了ROM和RAM的长处,不仅具备电子可擦除可编程(EEPROM)的性能,还不会断电丢失数据同时可以快速读取数据(NVRAM 的优势),U 盘和MP3里用的就是这种存储器。

Flash可以对称为块的存储器单元进行擦写和再编程。任何Flash器件的写入操作只能在空或者已擦除的单元内进行。所以大多数情况下,在进行写入操作之前需先进行擦除。目前一般情况下,上了MB的ROM都是Flash。

Flash的内部存储是MOSFET,里面有个悬浮门,是真正存储数据的单元。数据在Flash内存单元中是以电荷形式存储的。而数据的表示,以所存储的电荷的电压是否超过一个特定的阈值Vth来表示,因此,Flash的存储单元的默认值,不是0(其他常见的存储设备,比如硬盘灯,默认值为0),而是1,而如果将电荷释放掉,电压降低到一定程度,表述数字0。

目前常用的Flash芯片有NOR和NAND两种规格。

2、NOR FLASH

Nor Flash是一种非易失性闪存技术。特点是在芯片内执行,这样应用程序可以直接在Flash闪存内运行,不必再把代码督导系统RAM中。NOR的传输速率很高,在1~4MB的小容量时具有很高的成本效益,但是很低的写入和擦除速度大大的影响了它的性能。

NOR常用1~32MB,随机访问,常见的容量有:128KB、256KB、1MB、2MB。

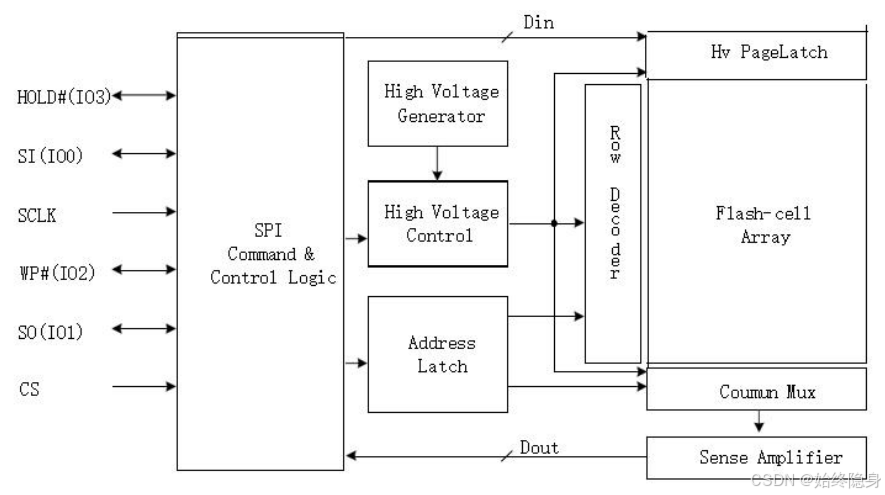

某NOR FLASH的芯片功能框图

3、NAND FLASH

NAND在嵌入式系统中通常用于存储处理器的代码数据和用户数据,如果说内存是PC的内存条,则NAND就是PC的硬盘。NAND结构能提供极高的单元密度,可以达到高存储密度,并且写入和擦除速度也很快。应用NAND的困难在于Flash的管理及需要特殊的系统接口。

NAND的内部采用非线性宏单元模式,为固态大容量内存的实现提供了廉价有效的解决方式。NAND的数据线与地址线复用,不能利用地址线随机寻址,读取不能按页来读取,内部电路简单,数据密度大,体积小,成本低。大容量的Flash一般都是NAND型。

主要用于大容量数据存储,如固态硬盘(SSD)和USB闪存驱动器。

NAND常用16~512MB,顺序访问,常见的容量有:1GB、2GB、3GB。

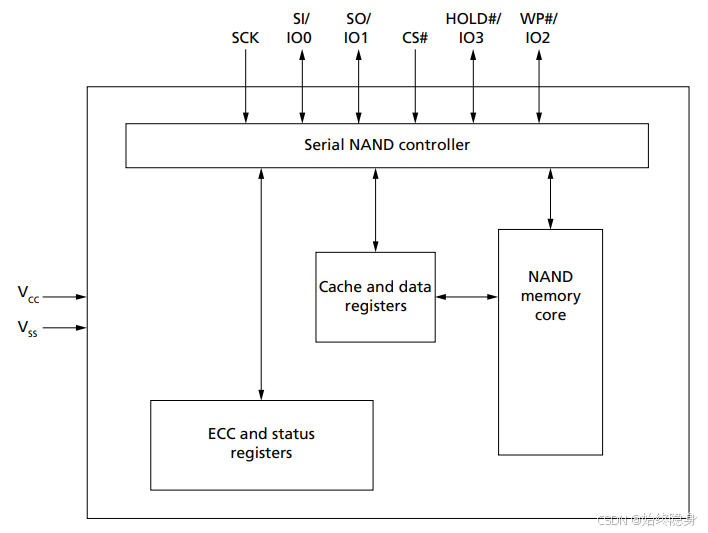

某NAND FLASH的芯片功能框图

4、NOR和NAND的区别

(1)NOR的读速度比NAND稍快一些。

(2)NAND的写入速度比NOR快很多。

(3)NAND的4ms擦除速度远比NOR的5s快。

(4)大多数写入操作需要先进行擦除操作。

(5)NAND的擦除单元更小,相应的擦除电路更少。

(6)NAND的实际应用方式比NOR复杂

(7)NOR可以直接使用,并在上面直接运行代码,而NAND需要I/O接口,因此使用时需要驱动。

(8)NOR带有SRAM接口,有足够的地址引脚来寻址,可以很容易地存取其内部的每一个字节。

(9)NAND器件使用复杂的I/O接口来串行地存取数据,各个产品或厂商的方式可能各不相同。8个引脚用来传送控制、地址和数据信息。

(10)NAND的读和写操作采用512字节的块,这一点有点像硬盘管理此类操作,很自然地,基于Nand的存储器就可以取代硬盘或其他块设备。NOR的特点是芯片内执行,这样应用程序可以直接在FLASH闪存内运行,不必再把代码读到系统RAM系统中。

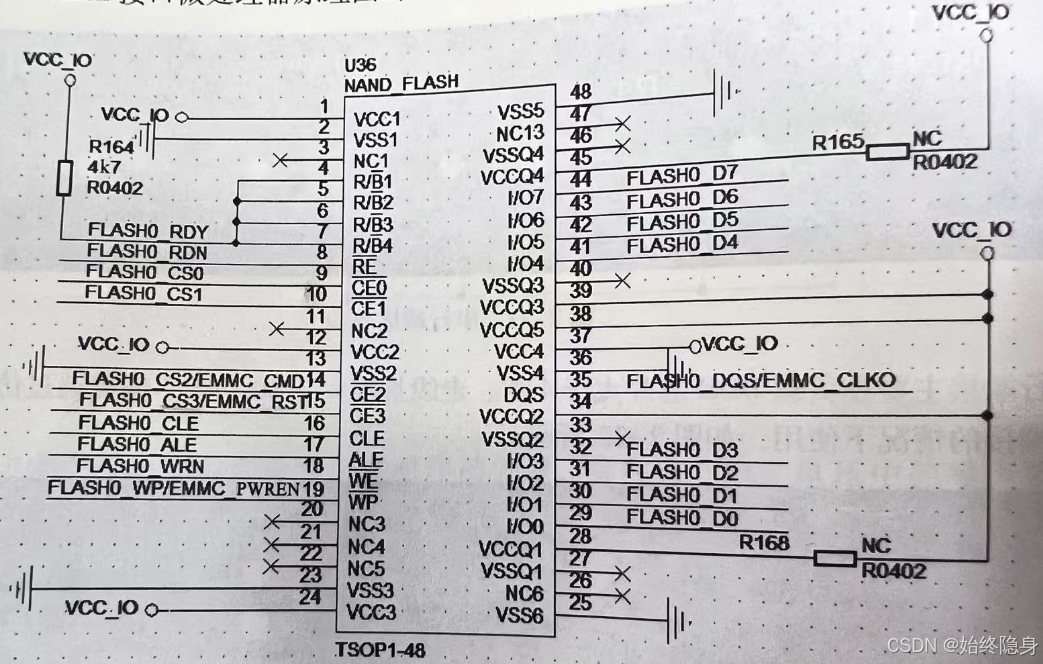

5、电路原理和引脚定义

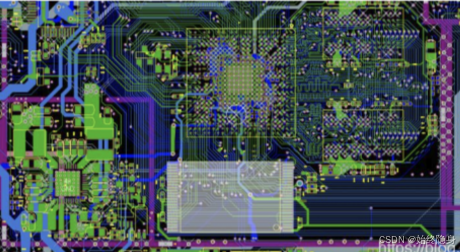

5.1、FLASH的电路参考设计

5.2、FLASH的引脚定义

(1)I/O 0~I/O 7:用于输入地址/数据/命令,输出数据,有可能是16位,但高8位只用于数据。

(2)CLE:命令锁存使能,在输入命令之前,要现在模式寄存器中设置CLE使能。

(3)ALE:地址锁存使能,在输入地址之前,要现在模式寄存器中设置ALE使能。

(4)CE#:芯片使能,在操作Nand Flash之前,要先选中此芯片,才能操作。

(5)RE#:读使能,在读取数据之前,要先使CE#有效。

(6)WE#:写使能,在写取数据之前,要先使WE#有效。

(7)WP#:写保护。

(8)R/B#:就绪/忙,主要用于在发送完编程/擦除命令后,检测这些操作是否完成;“忙”表示编程/擦除操作仍在进行中;“就绪”表示操作完成。

(9)VCC:电源电压。

(10)VSS:接地。

(11)NC:未定义,未连接。

备注:在数据手册中常会看到,对于一个引脚定义,有些字母上面带一个横杠,那是说明此引脚/信号是低电平有效,如RE头上有一个横线,那就说明此RE是低电平有效。此外,为了书写方便,在字母后面加“#”也表示低电平有效,如CE#。如果字母头上什么都没有,就默认高电平有效。

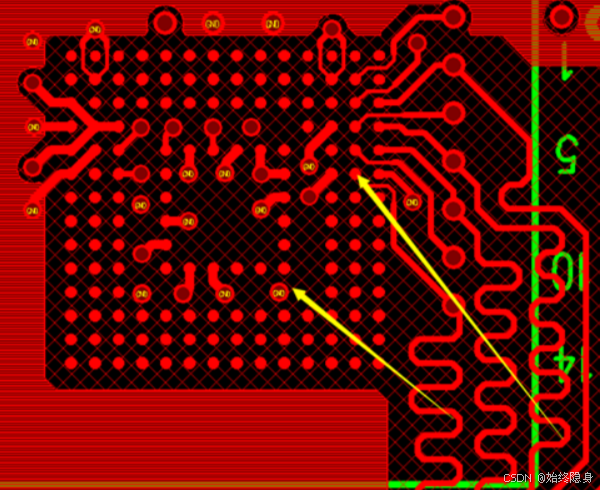

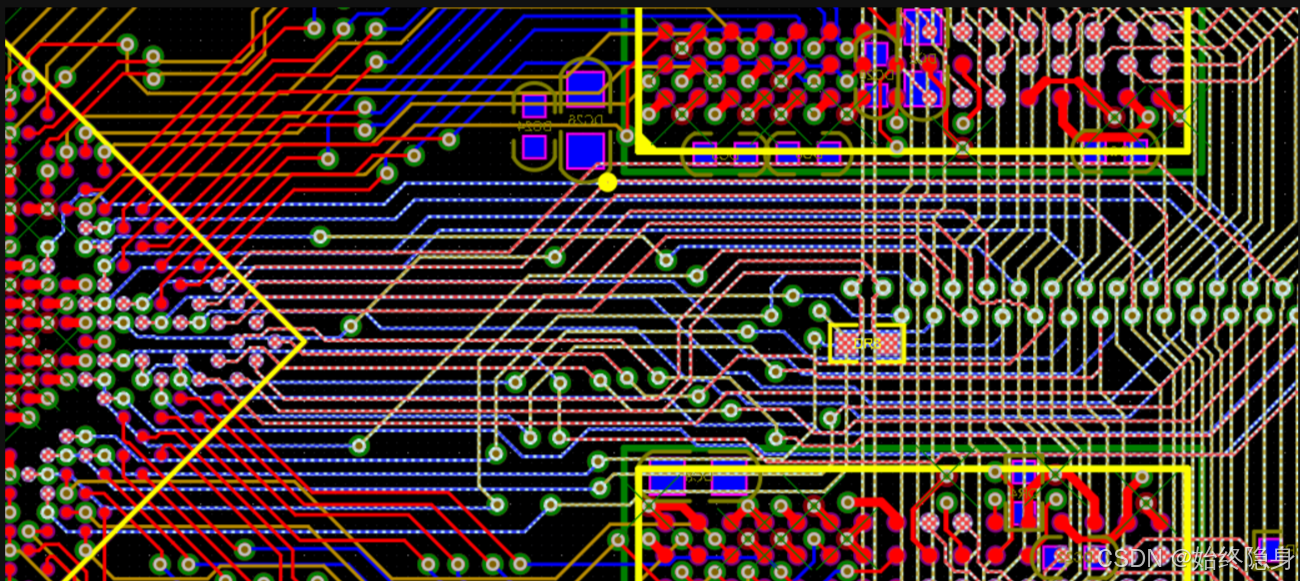

6、FLASH的PCB布局布线要求

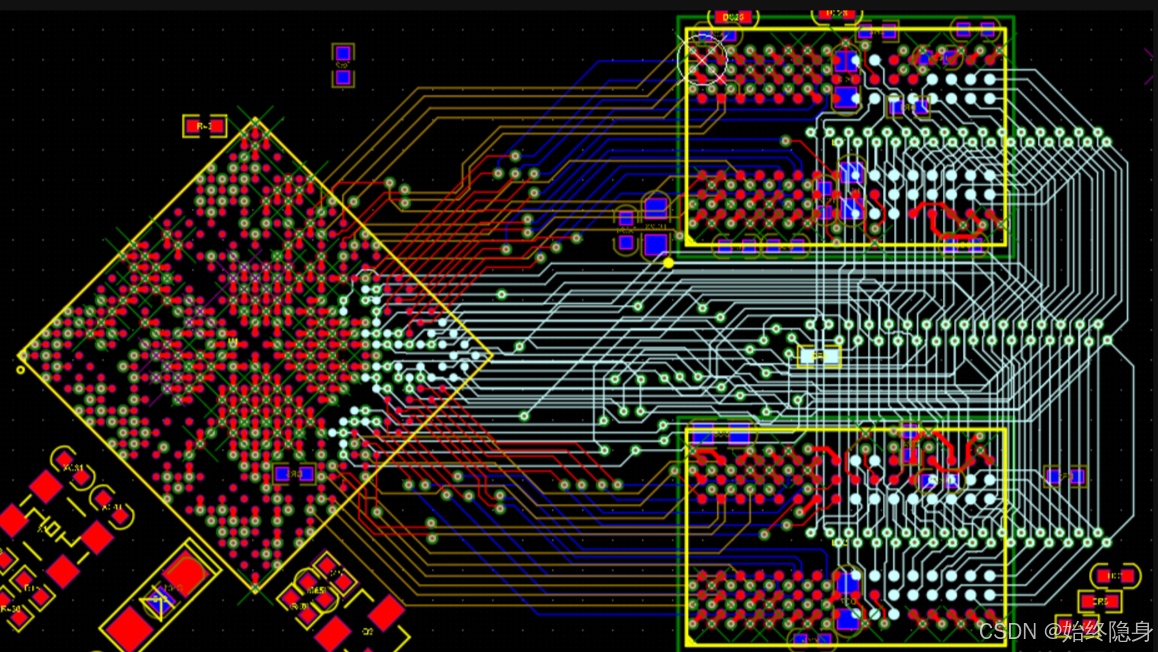

(1)NAND应尽量靠近主控摆放。

(2)去耦电容均需要靠近NAND摆放。

(3)RE、WE、DQS信号串接电阻靠近主控放置,串阻与主控连接走线距离≤300mil;

(4)NAND 与主控走线间走线≤2000mil。

(5)走线阻抗 50 欧。

(6)线间距≥2 倍线宽。

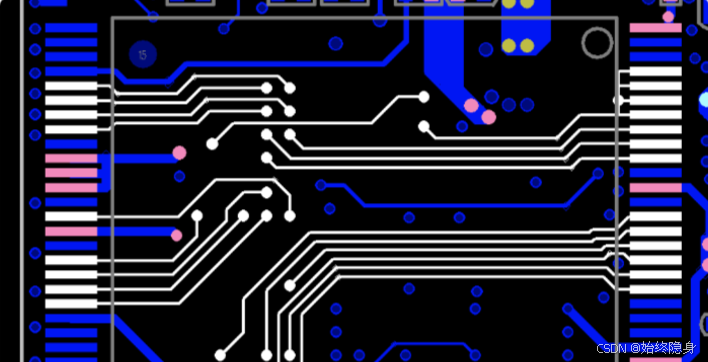

(7)D0~D7、 RE、 WE 相对于 DQS 做等长,控制≤300mil。

(8)D0~D7 上使用过孔的数量尽量相同,如果打孔,在孔的就近位置打一个换层的回流地孔。

(9)务必保证走线参考平面完整。

(10)走线尽量避开高频信号。

(11)VCC/VCCQ 线宽不小于 12mil,或直接使用敷铜代替电源走线;电源线上如有过孔,则过孔数量不少于 2 个,避免过孔限流影响供电。

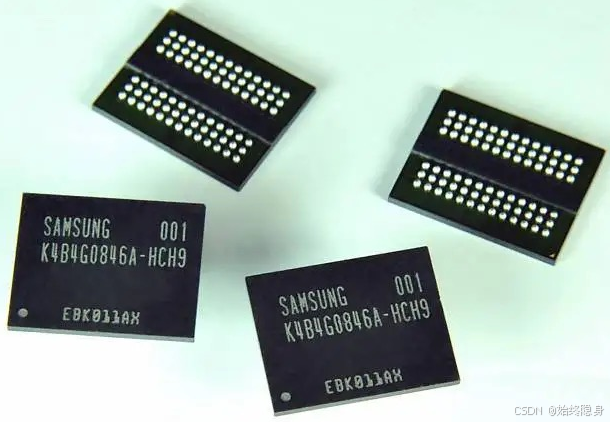

五、EMMC

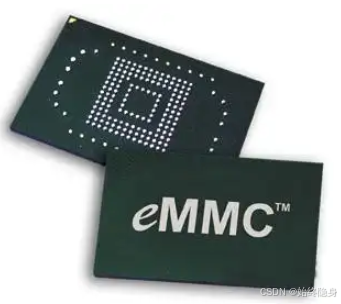

1、简介

eMMC是一种嵌入式非易失性的存储器系统,由Nand Flash和Nand Flash控制器组成,以BGA的方式封装子啊一款chip上。它的明显优势是在封装中集成了一个闪存控制器,它采用了JEDEC标准的BGA封装,并采用统一闪存接口管理闪存。

eMMC在内部集成了Flash Controller,包 括了协议、擦写均衡、坏块管理、ECC检验、电流管理、时钟管理、数据存取、掉电保护等功能。eMMC的读写速度比Nand Flash的读写速度快很多,eMMC的读写速度可高达每秒50MB到100MB以上。eMMC具有快速、可升级的性能,同时其接口电压可以是1.8V或者3.3V。eMMC的存储容量大,市场上32GB、64GB容量都是常见的。其常见的封装有BGA153、BGA169、BGA100。

括了协议、擦写均衡、坏块管理、ECC检验、电流管理、时钟管理、数据存取、掉电保护等功能。eMMC的读写速度比Nand Flash的读写速度快很多,eMMC的读写速度可高达每秒50MB到100MB以上。eMMC具有快速、可升级的性能,同时其接口电压可以是1.8V或者3.3V。eMMC的存储容量大,市场上32GB、64GB容量都是常见的。其常见的封装有BGA153、BGA169、BGA100。

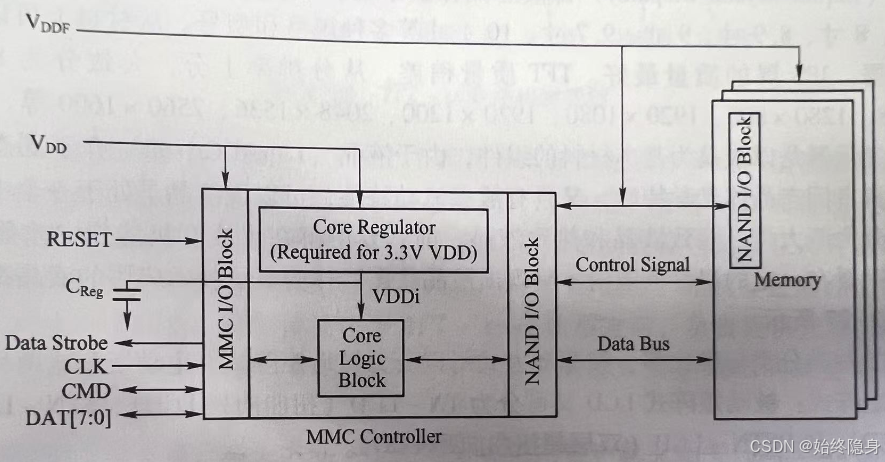

三星某型号eMMC内部结构图

未来发展趋势:随着技术的进步,eMMC也在不断演进。未来的eMMC标准可能会进一步提高读写速度和容量,以适应更高性能的需求。同时,其他存储技术UFS和NVMe也在不断发展,可能会对eMMC的市场份额产生影响

2、电路原理和引脚定义

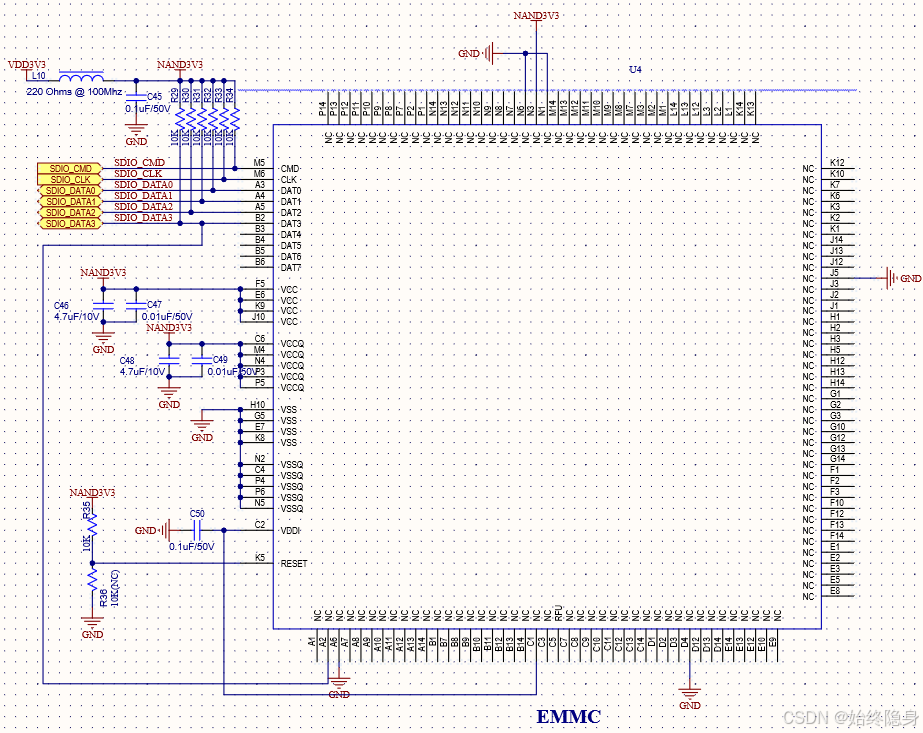

2.1、接口电路图

eMMC接口电路参考图

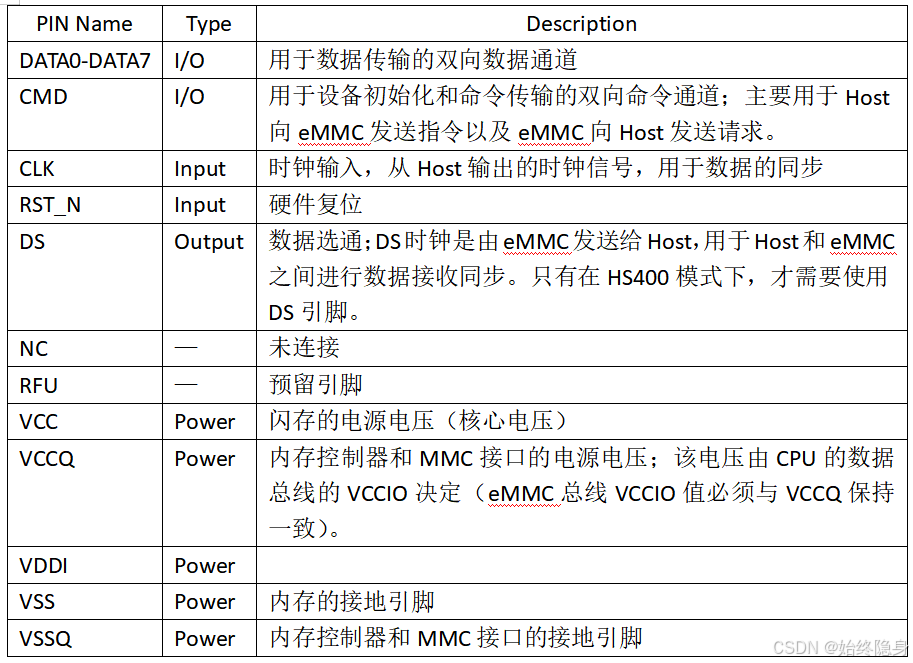

2.2、引脚定义

备注:

(1)eMMC 上的两个电源:VCC和VCCQ;VCC要求上电时间小于35ms。VCCQ的上电时间小于25ms,两者的下电时间尽量同步。

(2)eMMC LCK需要串联一个几十欧姆(如33Ω)的电阻,已实现阻抗匹配。

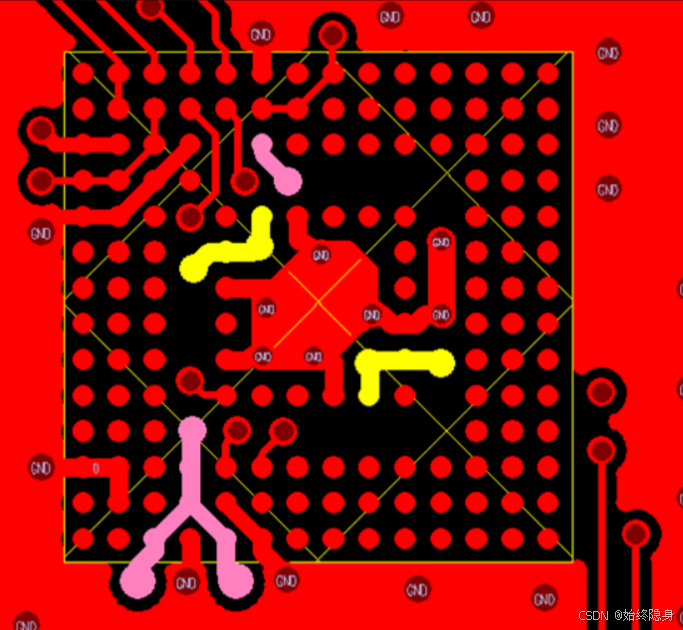

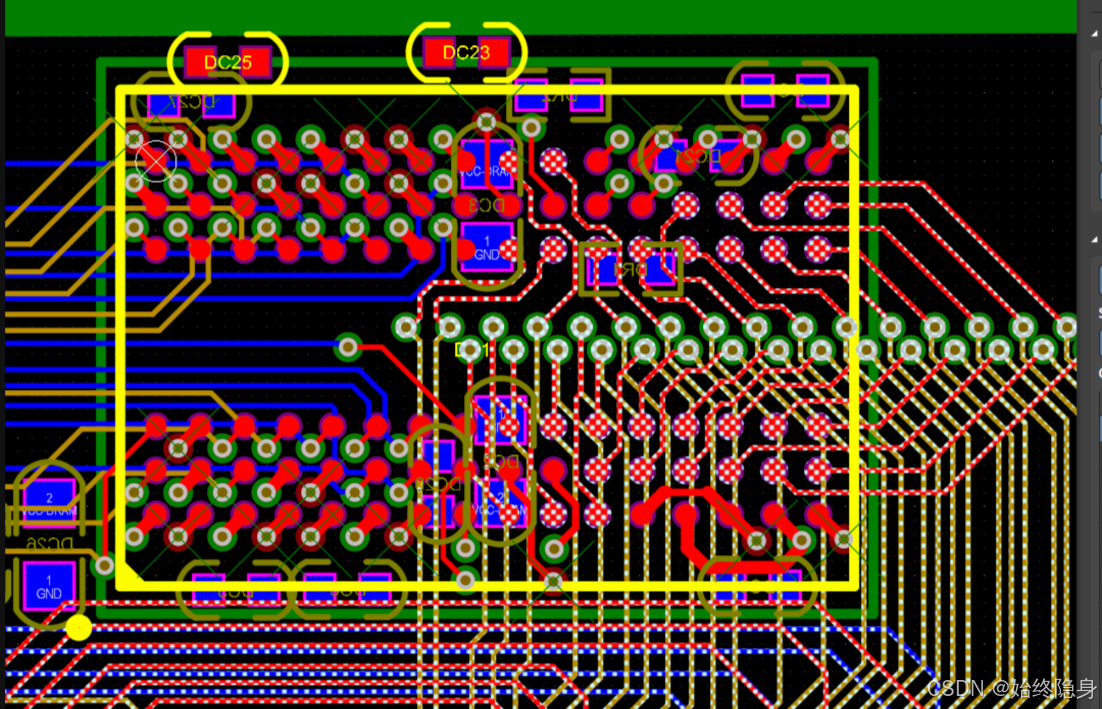

3、eMMC的PCB布局布线要求

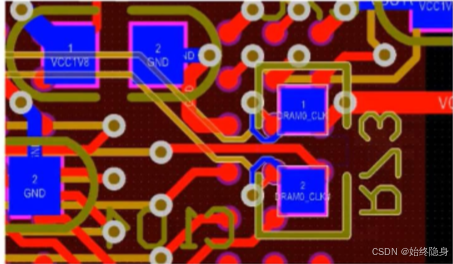

(1)eMMC控制器在放置时钟信号的下拉电阻时要靠近管脚放置;时钟信号需要包地处理,地线每隔200mil打一个地过孔。

CLK电路包地示意图

(2)eMMC的数据信号、时钟信号和控制信号需要控制50ohm阻抗。

(3)eMMC个电源管脚的滤波电容靠近对应的管脚放置,尽量保证一个管脚一个。

滤波电容摆放示意图

(4)时钟、数据、CMD信号需要做蛇形等长,误差小于120mil。走线的总长度不要超过3500mil,否则会导致高速模式下频率跑不高。

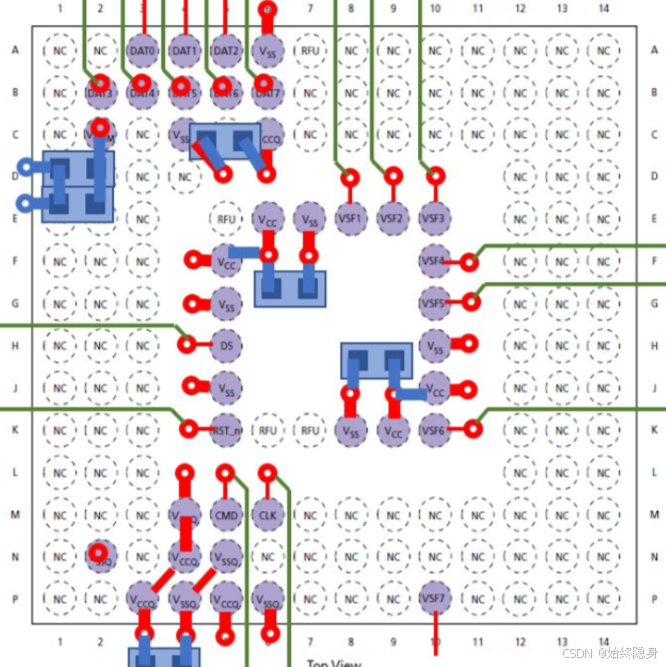

(5)eMMC芯片封装为0.5pitch的bga封装,有很多空的管脚,走线可采用经过不用的EMMC引脚走线的方式出线,降低对PCB制板间距的要求。

(6)eMMC所有信号少换层打孔,过孔数量尽量不要超过两个,eMMC信号换层前后,参考层建议都为地平面,在信号过孔 30mil(过孔和过孔的中心间距)范围内建议添加地回流过孔,改善信号回流路径,地过孔需要把信号换层前后地参考平面连接起来。

(7)eMMC BGA焊盘削盘,将焊盘适当缩小,以增加出线空间,这样就可以做到3.5mil的线宽出线。

(8)eMMC芯片下方在覆铜时,焊盘部分要增加覆铜禁布区域,避免铜皮分布不均影响散热,导致贴片虚焊。

禁布区域示意图

(9)emmc Flash走线要求整组包地。

(10)EMMC的两个电源3.3V、1.8V需要进行铺铜。

六、DDR(SDRAM)

1、SDRAM

同步动态随机内存(SDRAM)是有一个同步接口的动态随机存取内存(DRAM)。通常DRAM是有一个异步接口,这样它可以随时响应控制输入的变化。而SDRAM有一个同步接口,在响应控制输入前会等待一个时钟信号,这样就能和计算机的系统总线同步。时钟被用来驱动一个有限状态机,对进入的指令进行管线操作。这使得SDRAM与没有同步接口的异步DRAM相比,可以有一个更复杂的操作模式。

管线意味着芯片可以在处理完之前的指令前,接受一个新的指令。在一个写入的管线中,写入命令在令一个指令执行完之后可以执行,而不需要等待数据写入存储队列的时间。在一个读取的流水线中,需要的数据在读取指令发出之后固定数量的时钟频率后到达,而这个等待的过程可以发出其它附加指令,这种延迟被称为等待时间,在为计算机购买内存时是一个很重要的参数。

SDRAM在计算机中被广泛应用,从最初的SDRAM到之后一代的DDR(或称DDR1),然后是DDR2和DDR3进入大众市场,2015年开始DDR4进入消费市场。

2、DDR

双倍频率动态随机存储器(DDR),是内存的一种。DDR内存是SDRAM内存的基础上发展而来的。

内存又可以叫做主存。是CPU能直接寻址的存储空间。内存的特点是访问数据的速率快。内存是电脑中的主要部件,它是相对于外村而言的。我们平常使用的程序,如Windows操作系统、打字软件、游戏软件等,一般都是安装在硬盘等外存上的,但仅此是不能使用其功能的,必须把它调入内存中运行,才能真正使用其功能,我们平时输入一段文字,或玩一个游戏,其实都是在内存中进行的。就好比在一个书房里,存放书籍的书架和书柜相当于电脑的外存,而我们工作的办公桌就是内存。通常我们把要永久保存的、大量的数据存储在外存上,而把一些临时的或少量的数据和程序放在内存上,当然内存的质量会直接影响电脑的运行速度。

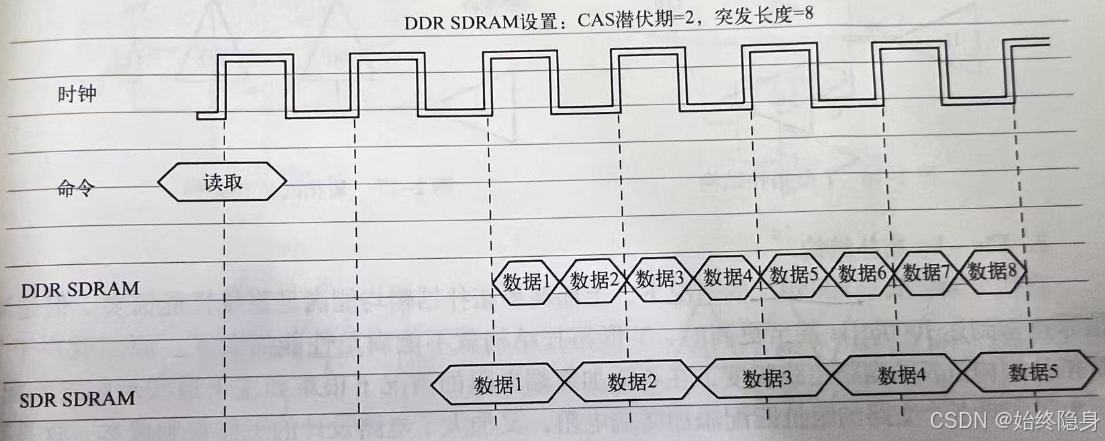

2.1、工作原理

SDRAM在一个时钟周期内只传输一次数据,它是在时钟的上升沿进行数据传输;而DDR则实在一个时钟周期内传输两次数据,它能够在时钟的上升沿和下降沿各传输一次数据,因此称为双倍速率同步动态随机存储器。DDR内存可以在与SDRAM相同的总线频率下达到更高的数据传输率。

2.2、性能特点

与SDRAM相比:DDR运用了更先进的同步电路,使指定地址、数据的传送和输出主要步骤既独立执行又保持与CPU同步;DDR使用了DLL(延时锁定回路提供一个数据滤波信号)技术,存储控制器可使用这个数据滤波信号来精确定位数据,每16次输出一次,并重新同步来自不同存储器模块的数据。DDR本质上不需要提高时钟频率就能加倍提高SDRAM的速度,它允许在时钟脉冲的上升沿和下降沿读出数据,因而其速度是SDRAM的两倍。

从外形体积上DDR和SDRAM相比差别不大,他们具有同样的尺寸和同样的针脚距离。但DDR为184针脚,比SDRAM多出来16个引脚,主要包括了新的控制、时钟、电源和接地等信号。DDR内存采用的是支出2.5V电压的SSTL2标准,而不是SDRAM使用的3.3V电压的LVTTL标准。

很多人经常将DDR和内存的双通道、三通道技术相混淆,事实上这是两组毫无关系的概念,DDR是一种内存的设计技术;而多通道内存技术是一种在主板上实现的并行内存访问技术,与使用的内存类型没有关系。两个通道可以使用不同速率或访问时序的内存。

2.3、DDR存储器的电气特性验证

JEDEC电子工程设计发展联合协会已经明确规定存储设备的详细测试要求,需要对抖定时和电气信号质量进行验证。

测试参数:时钟抖动、建立和保持时间、信号的过冲、信号的下冲、速度电压等。

2.4、DDR2、DDR3、DDR4、DDR5的区别

(1)DDR2:工作电压:1.8V I/O接口电压:SSTL_1.8V(1.8V)

总线频率:200/266/333/400MHZ

核心频率:100/133/166/200MHZ

数据传输速率:400/533/667/800MHZ

预取:4bit 突发长度:4/8

(2)DDR3:工作电压:1.5V I/O接口电压:SSTL_1.5V(1.5V)

总线频率:400/533/667/800MHZ ~ 1066MHZ

核心频率:100/133/166/200MHZ ~ 266MHZ

数据传输速率:800/1066/1333/1600MHZ ~ 2133Mbps

预取:8bit 突发长度:4/8

(3)DDR4:工作电压:1.2V

预取:8bit

总线时钟:800 ~ 1200MHZ

内部收益率:200 ~ 300MHZ

传输速率:1600 ~ 5067Mbps 最高速率大约可以达到52.6GB/s

单个内存条的最大容量一般为16GB活32GB,每个内存模块的带宽较低。

(4)DDR5:工作电压:1.1V

预取:16bit

传输速率:起始速率约为4800MHZ,理论上可达到8400MHZ甚至更高。最高 传输速率大约可达到67.2GB/s

带宽:单一内存模块的带宽比DDR4高达约50%,更适合数据密度集型应用, 如高性能计算、游戏和内容创作。

容量支持:单条内存条的容量可扩展到64GB甚至更高,适合需要超大内存的 应用场景,如服务器、工作站等。

ECC支持(错误校验码):内置ECC支持(针对内部数据传输),提高数据传 输的可靠性,减少内存错误,这对服务器和工作站非常重要。

延迟:延迟相对于DDR4较高,但高频率和带宽的优势通常会 弥补这一点,特 别是在需要处理大量数据的场景下。

随着DDR的更新换代,总线的时钟频率越来越高,并且传输速率也越来越快,工作电 压也越来越低,逐渐朝着低功耗、高速率的方向发展,这也为了DDR的布线布局带来了较高 要求的阻抗匹配。

平板电脑DDR芯片的数据总线有8位、16位、32位三种。如果是8位的芯片,则64位的数 据总线需要8颗DDR3芯片。

2.5、DDR芯片引脚介绍

(1)CK,CK#:差分时钟信号。所有控制和地址输入信号在CK的上升沿和CK#的下降沿交叉处被采样,输出数据选通(DQS,DQS#)参考与CK和CK#的交叉。

(2)CKE:时钟使能。

(3)CS#:片选信号,为输入信号,低电平有效。

(4)RAS#:行地址选通信号。

(5)CAS#:列地址选通信号。

(6)WE#:写使能信号,为输入信号,低电平有效。

(7)BA{0~2}:BANK地址信号,为输入信号。

(8)BQM{0~1}:数据掩码,为输入/输出双向信号,其方向与数据总线方向相同,高电平有效。

(9)ODT:终结电阻。用于提高信号的传输性能,类似终端电阻,可以降低干扰,改善信号传输波形。所谓的终结,就是让信号被电路的终端吸收掉,而不会在电路上形成反射,主要由一排终结电阻构成,可有效减小反射/信噪比,ODT就是将电阻移植到了芯片内部。

(10)ZQ:外接一个240Ω的低公差参考电阻,内接自动接准器,目的是提高数据总线的信号传输质量,从而提高传输速度。

(11)REST:复位,低电平有效。该信号主要提供两方面的功能,其一是可以简化内存芯片上电后的初始化过程;其二是内存系统一旦进入未知或不可控状态后可以直接重启而无需断电重启。

(12)DQ{0~15}:数据信号,为输入/输出双向信号。

(13)A{0~15}:地址信号,为输入信号。

(14)DQS,DQS#:数据选通信号,数据可以通过DQS的上升沿与下降沿传输。在读模式时,DQS由存储器发给CPU,DQS与数据边沿对齐。在写模式时,DQS由CPU发给存储器,DQS与数据中间对齐。

(15)VERF CA/VERF DQ:基准电压等于VDD电压的一半,VERF CA表示命令和地址部分的电路所需的基准电压。VERF DQ表示数据部分的电路所需的基准电压。

(16)VDD:主要给芯片内部地址/控制信号接口及主要控制逻辑电路提供电源。

(17)VDDQ:主要给数据及锁存信号接口及逻辑电路提供电源。

(18)VDLL:主要给内存芯片内部的DLL(延迟锁相环电路)提供电源。DLL电路主要用于控制内存芯片数据输出(也就是写操作)时的数据信号和锁存信号的时序。同样,出于信号完整性和抗干扰的考虑,地址引脚也分成几类。

(19)VSS:主要给芯片内部地址/控制信号接口及主要控制逻辑电路提供地回路连接。

(20)VSSQ:主要给数据及锁存信号接口及逻辑电路提供地回路连接。

(21)VSSDL:主要给内存芯片内部的DLL提供地回路。

2.6、 DDR存储阵列

DDR3的内部是一个存储阵列,将数据“填”进去,可以将它想象成一张表格。和表格的检索原理一样,先指定一个行(Row),再指定一个列(Column),就可以准确地找到所需要的单元格,这就是内存芯片寻址的基本原理。对于内存,这个单元表格可称为存储单元,那么这个表格(存储阵列)就是逻辑Bank。如图所示,这是一个NXN的阵列,B代表Bank地址编号,C代表列地址编号,R代表行地址编号。如果寻址命令是B1、R2、C6,就能确定地址是图中黑格的位置。目前DDR3内存芯片基本都是8个Bank设计,也就是说一共有8个这样的“表格”。寻址的流程就是先指定B安康地址,再指定行地址,然后指定列地址,最终确定寻址单元。

DDR内部Bank示意图

2.7、DDR的差分时钟

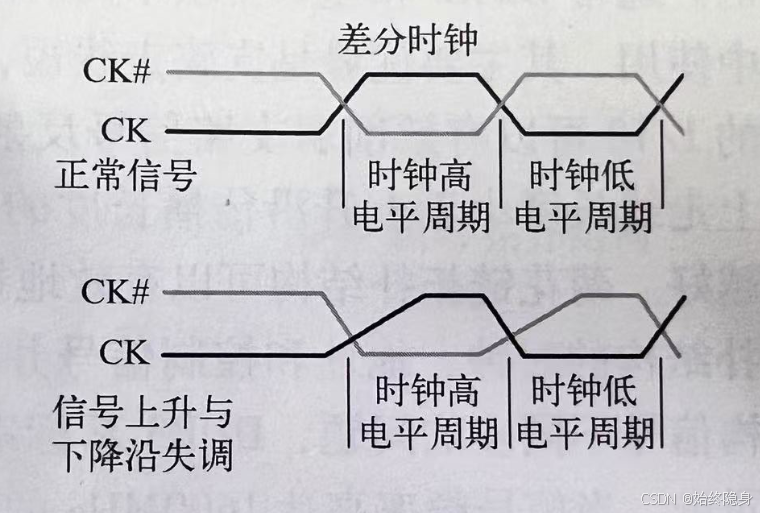

差分时钟是DDR的一个必要设计。但是CK#的作用并不能理解为第二个触发时钟(可以在讲述DDR原理时简单地这么比喻),而是起到触发时钟校准的作用。由于数据是在CK的上/下沿触发的, 造成传输周期缩短了一半,因此必须保证传输周期的稳定性,以确保正确传输数据,这就要求对CK的上/下沿间距有精确的控制。但因为温度、电阻性能的改变的原因,CK上/下沿间距可能发生变化,此时与其相反相的CK#就起到了纠正作用(CK是上升快、下降慢,CK#则是上升慢、下降快)。而由于上/下沿触发的原因,也使CL为1.5和2.5成为可能,并容易实现。如图1所示为差分时钟工作原理。如图2所示为差分时钟的作用。

图1 差分时钟工作原理

图2 差分时钟的作用

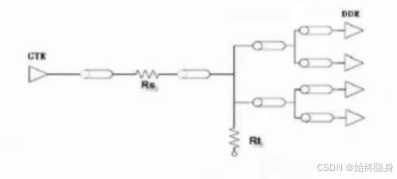

2.8、DDR的拓扑结构

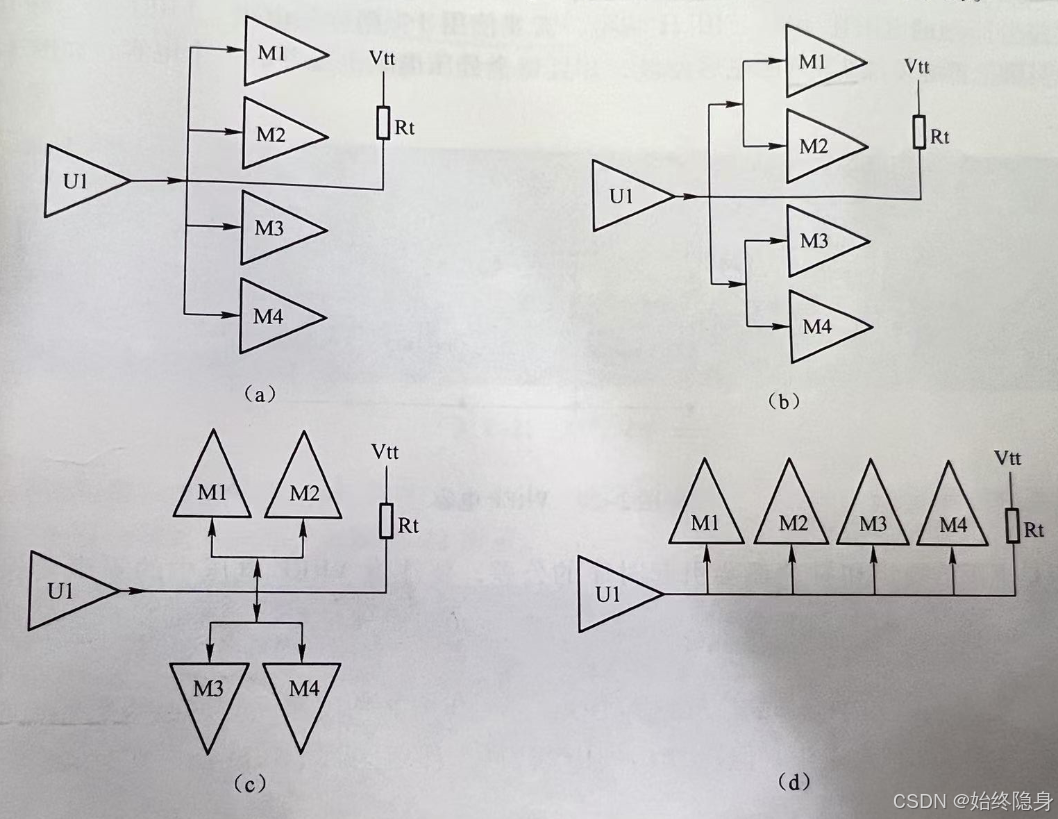

在DDR的PCB设计中,一般需要考虑等长和拓扑结构。等长比较好处理,给出一定的等长精度通常是PCB设计师能够完成的。但对于不同速率的DDR,选择合适的拓扑结构非常关键,在DDR布线中经常使用的有T形拓扑结构和菊花链、Fly-by拓扑结构。

(1)T形拓扑结构

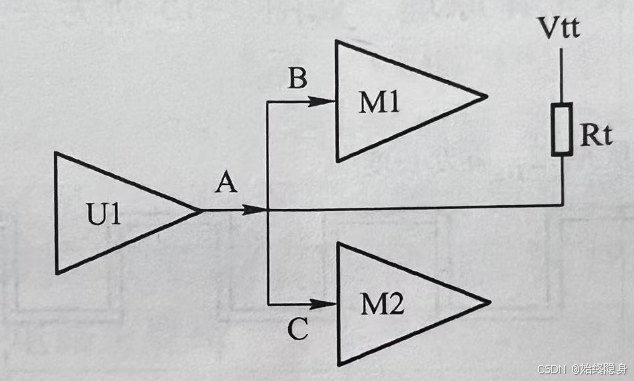

T形拓扑结构也称为星形拓扑结构。星形拓扑结构每个分支的接收端负载和走线长度尽量保持一致,这就保证了每个分支接收端负载同时收到信号,每条分支上一般都需要终端电阻,终端电阻的阻值应和连线的特征阻抗相匹配。星形拓扑结构可以有效地避免时钟、地址和控制信号的不同步问题。

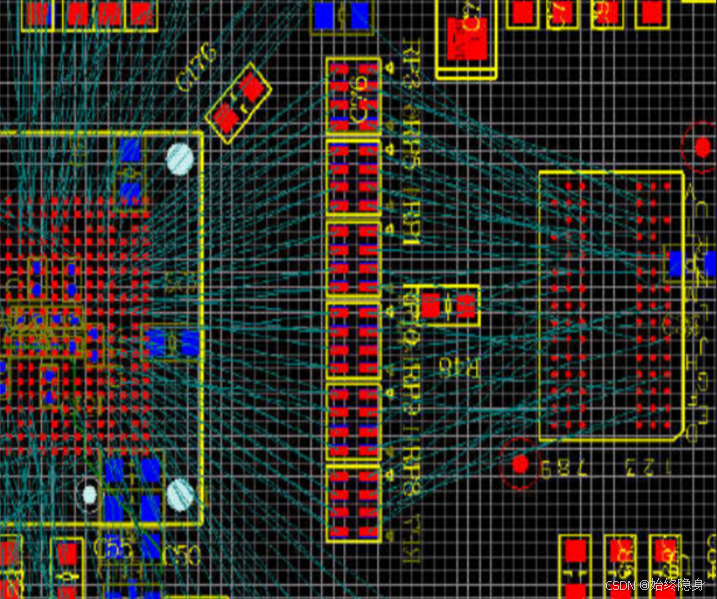

2片DDR的T形拓扑结构

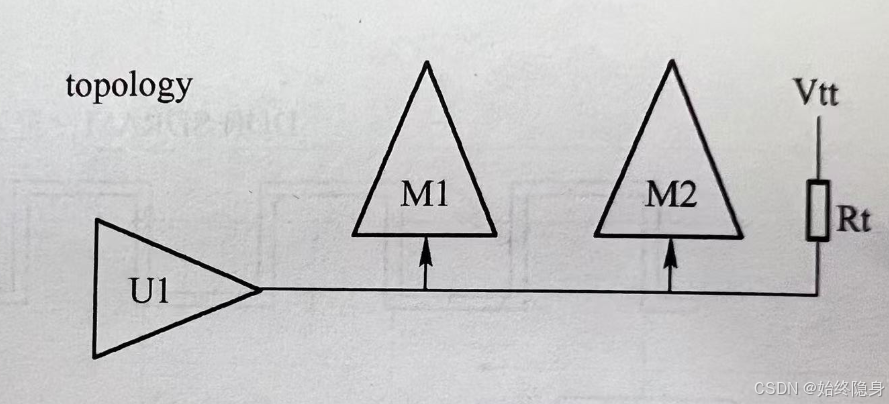

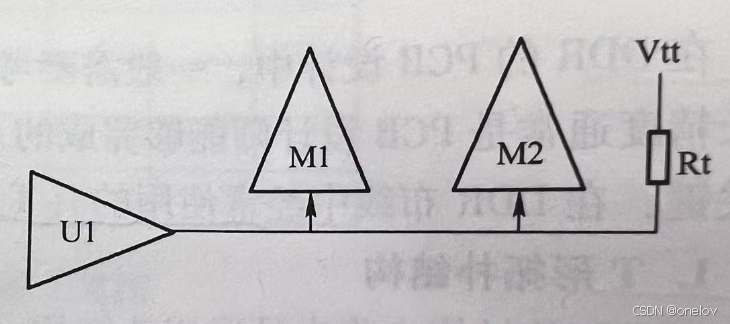

(2)菊花链拓扑结构

菊花链拓扑结构和T形拓扑结构不同,菊花链拓扑结构没有保持驱动端到各个负载的走线长度尽量一致,而是确保各个驱动端到信号主干道的长度尽量短。菊花链拓扑结构走线的特点是,牺牲了时钟、地址和控制信号的同步,尽可能降低各负载分支走线长度,避免分支信号对主干信号的反射干扰。

2片DDR的菊花链拓扑结构

(3) Fly-by拓扑结构

在信号频率低于800MHZ的情况下,上面两种拓扑结构均能满足系统性能需要。但是当信号频率到达1000MHZ甚至更高时,T形拓扑结构就不能满足性能需要了。原因就在于T形拓扑结构过长的支路走线长度,在不添加终端电阻的情况下很难和主干道实现阻抗匹配,而为了实现各个支路的阻抗匹配添加终端电阻,又加大了电路设计的工作量和成本,这是我们不愿看到的。因此高速信号使用T性拓扑结构,特别是Stub>4的时候,支路信号对主干信号的反射干扰是很严重的。通常DDR2和速率要求不高的DDR3使用T形拓扑结构。菊花链拓扑结构主要在DDR3中使用,其主要优势是支路走线短,一般认为菊花链支路走线长度小于信号上升沿传播长度的1/10可以有效削弱支路信号反射对主干信号的影响。实际设计中希望这个长度越短越好。菊花链拓扑结构可以有效的抑制支路的反射信号,但相对于T形拓扑结构,菊花链拓扑结构的时钟、地址和控制信号并不能同时到达不同的DDR芯片。为了解决菊花链拓扑结构信号不同步的问题,DDR3新标准中加入了时间补偿技术,通过DDR3内部调整实现信号同步。当信号频率高达1600MHZ的时候,T形拓扑结构已经无能为力,只有菊花链或其衍生的拓扑结构能满足这样的性能需求。一般DDR都会使用Fly-by拓扑结构。Fly-by拓扑结构要求支路布线长度Stub=0,Fly-by具有更好的信号完整性。

2片DDR的Fly-by拓扑结构

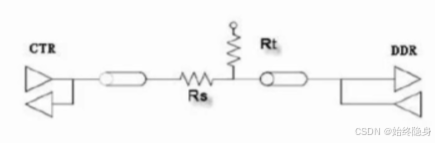

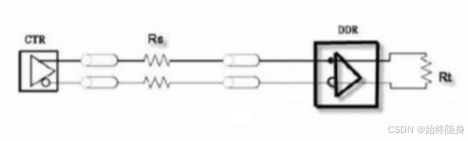

在菊花链拓扑的实际应用中,为了抑制Stub过长和分支太多对主干信号的反射干扰,以及加强主干信号的驱动能力,一般在末端预留端接电阻电路。末端下拉电阻会增大I/O口驱动功耗,所以采用末端上拉电阻的方式进行端接。计算信号驱动部分的戴维南等效电压作为上拉电压Vtt,Rt为驱动部分的等效电阻,通常上拉电压取值为I/O驱动电压的一半,即Vtt=Vddr/2.

对于超过两片的DDR来说,通常根据器件的摆放方式选择相应的拓扑结构。下图显示了针对不同摆放方式而特殊设计的拓扑结构,在这些拓扑结构中,只有A和D是最适合4层板的PCB设计。然而,对于DDR2-800,所列的这些拓扑结构都能满足其波形的完整性,而在DDR3的设计中,特别是在1600Mbps时,则只有D是满足设计要求的。

2.9、DDR的电源设计

(1)主电源VDD和VDDQ

主电源的要求是VDDQ=VDD,VDDQ是给I/O缓冲供电的电源,VDD是给芯片供电的工作电压,但一般都把VDDQ和VDD合成一个电源使用。有的芯片还有VDDL,它是给DLL供电的,和VDD使用用一个电源即可。

设计电源时,需要考虑电压、电流是否满足要求,以及电源的上电顺序和电源的商店时单调性等。电源电压一般要求在±5%以内。电流需要根据使用的芯片及芯片个数等进行计算。由于DDR的电流一般都比较大,所以在PCB设计时,若有一个完整的电源平面敷到引脚上,是最理想的状态,并且在电源入口加大电容储能,每个引脚上加10 ~ 100nF的小电容滤波。

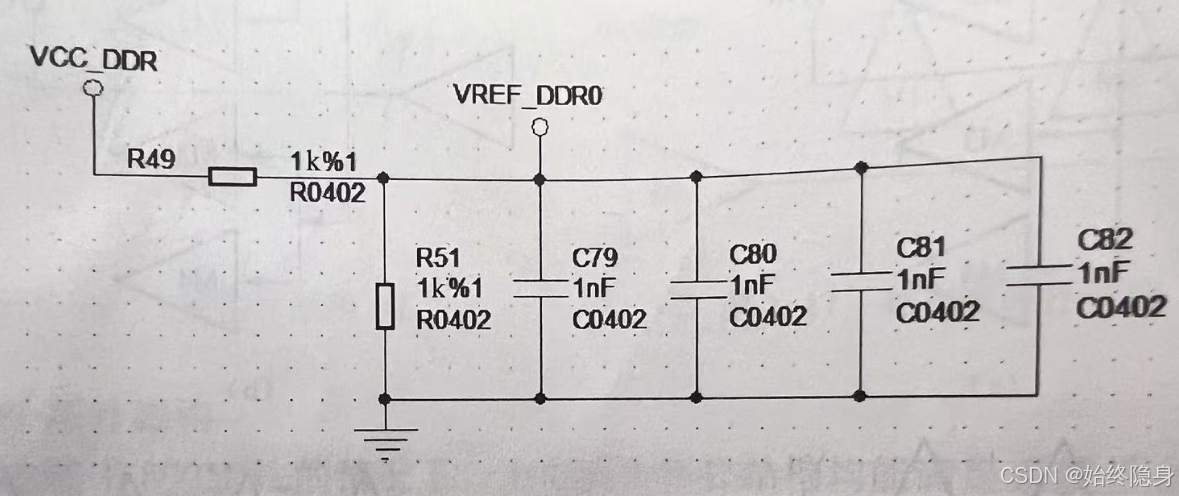

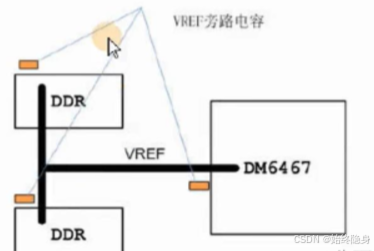

(2)参考电压Vref

对于内存系统工作非常重要的参考电压信号Vref在DDR3系统中将分为两个信号:一个是为命令和地址信号服务的Vrefca;另一个是为数据总线服务的Vrefdq。

参考电压Vref要求跟随CDDQ,并且Vref=VDDQ/2,所以可以使用电源芯片提供,也可以采用电阻分压的方式得到。由于Vref一般电流较小,在几mA到几十mA的数量级,所以用电阻分压的方式,既节约成本,又能在布局上比较灵活,放置的离Vref尽量近,紧密跟随VDDQ电压。需要注意分压用的电阻在100 ~ 10KΩ均可,需使用1%精度的电阻。Vref参考电压的每个引脚上都需加10nF的电容滤波,并且每个分压电阻上也并联一个电容。

Vref电压的原理示意图

但是电源的噪声和抖动都会引起时序的公差,要注意Vref电压中的噪声要保持在±25mV,Vref和Vtt不要在同一层走线,如果不可避免,要保证充足的间距,建议在150mil以上。

在DDR3设计中,Vrefca、Vrefdq和DDR2中的Vref功能相同,可以使用外置的分压电阻或电源控制芯片来产生,但在DDR4中Vrefca保留,而Vrefdq在芯片设计中已经取消,改为有芯片内部产生。

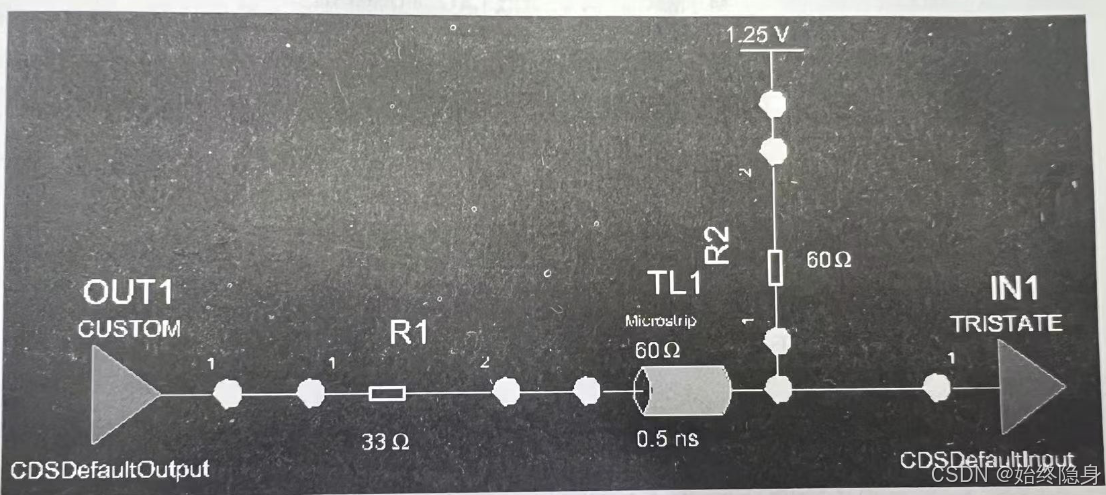

(3)用于匹配的电压Vtt

Vtt其实与Vref的电平是一样的,对DDR2来说就是0.9V,到那时Vref消耗的电流很小,可以通过一个电阻网络从1.8V转出来;而Vtt是端接使用的,电流比较大,能达到百mA级,需要用单独的电源芯片生成。

Vtt为匹配电阻上拉到的电流,Vtt=VDDQ/2(DDR2和DDR3),DDR4中Vtt等于VDDQ。DDR的设计中,当DDR芯片为2片或1片的情况下,总线上需要的电流不是很大,一般不需要进行Vtt端接。

一般DDR芯片为4片或以上的情况下,地址线和数据线的负重比较重,这时需要使用Vtt芯片来产生Vtt电压。如果使用Vtt,则Vtt的电流要求比较大(2 ~ 3.5A),所以需要走线使用铜皮敷过去,并且Vtt要求电流既可以提供电流又可以灌电流(吸电流)。一般情况下可以使用专门为DDR设计的产生Vtt的电源芯片来满足要求。而且,每个拉到Vtt的电阻旁一般放一个10 ~ 100nF的电容,整个Vtt电路上需要有uF级大电容进行储能。

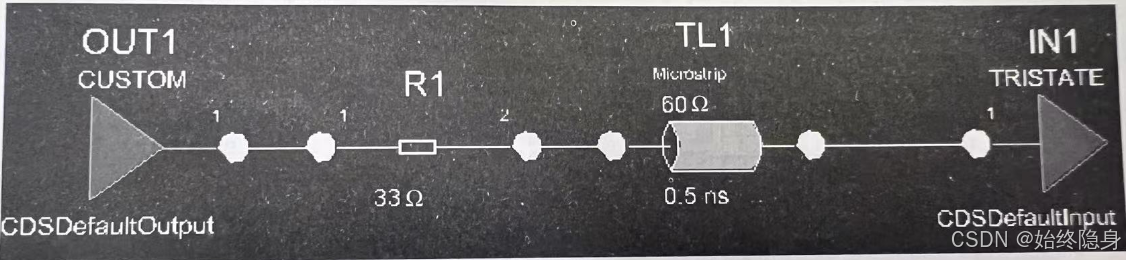

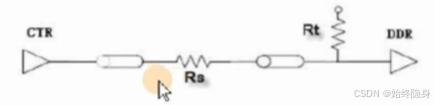

2.10、DDR端接技术

(1)串行端接主要用在负载DDR芯片不大于4片的情况下。对于双向数据线来说,串行端接电阻要放置在走线的中间,用来抑制振铃、过冲和下冲。对于单向的地址线、控制线来说,串行端接电阻要放在中间或信号的发生端控制器处。串行端接中,电阻的取值范围一般在10 ~ 33Ω。当然串行端接中电阻的阻值和信号反射及振铃有关,可以通过信号仿真获得电阻值。

()并行端接主要在负载或芯片大于4片,走线长度大于2000mil,或通过仿真验证需要并行端接的情况下使用。

2.11、DDR的PCB布局布线要求

DDR布局要求

(1)一片DDR

一片DDR时,点对点布局,留出一定的绕线空间。

(2)两片DDR

两片DDR时,相对于CPU对应DDR引脚的中心位置对称,留出一定的绕线空间,同时注意串接电阻、并联电阻的位置。

中间有排阻时,DDR相对于中心距离:800~1000mil;

中间无排阻时,DDR相对于中心距离:600~800mil;

要合理的规划走线布局结构,

(3)四片DDR及以上

四片或八片DDR时,一般凉凉顶底对贴。

- 数据线串接电阻一般放在DDR与控制器中间,并联电阻靠近串接电阻放置,可放于其背面,具体位置可由仿真决定。

- DM信号是数据线的掩码,一般都是点对点的单向传输,要求串接电阻放在控制器端,并联电阻放在DDR端。

- 地址线、控制线、时钟线都是单向传输,且一般都是点到多点的拓扑结构。要求串接电阻靠近控制器端,多个DDR间使用远端分支,分支尽量短且等长;并联电阻放在DDR端第一个T点处,长度不超过500mil;走菊花链拓扑的,并联电阻放在最后一个DDR后面,长度不超过500mil。

- 差分时钟信号是单向传输,串接电阻靠近控制器端,点到点的终端匹配电阻尽量靠近DDR,或放在DDR之后;点到多点,可以使用地址线的拓扑结构,终端匹配电阻放在第一个T点处。

- VREF的退耦电容必须靠近DDR和CPU管脚。

- VTT电压用在信号线上拉电阻上电流大,电压低,需表层铺铜连接,宽度大于150mil,每4个上拉电阻一个排阻至少对应一个高频退耦电容,且应均匀放置,同时附近应当均匀放置几个Bulk电容,至少末端应有一个Bulk电容(如4.7uF、100~200uF),若VTT走内层,兼容数目应更多。

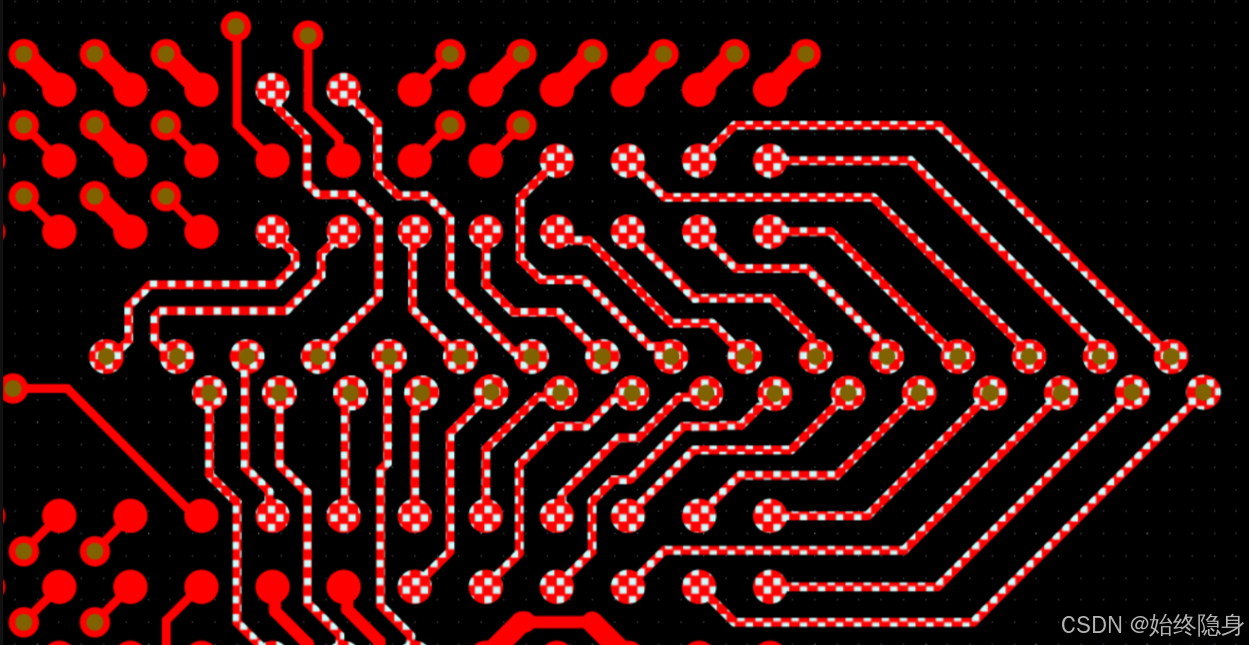

DR的PCB走线原则

(1)特性阻抗:单端50Ω,差分100Ω

(2)数据线没10根尽量走在同一层(D0~D7,LDM,LDQS),(D8~D15,UDM,UDQS)

(3)信号线的间距满足3W原则,数据线、地址(控制)线、时钟线之间的距离保持在20mil以上或至少3W。

(4)空间允许的情况下,应该在它们走线之间加一根地线进行隔离。地线宽度推荐为15~30mil。

(5)VREF电源走线先经过电容再进入管脚,VREF电源走线线宽推荐不小于20mil,与同层其他信号线间距20mil以上。

(6)所有信号线不得跨分割,且有完整的参考频平面,换层时,如果改变了参考层,要注意考虑增加回流地过孔或退耦电容。

(7)两片以上的DDR布线拓扑结构优选远端分支,T点的过孔打在两片DDR中间。

(8)所有DDR信号距离相应参考平面边沿至少30~40mil。任何非DDR部分的信号不得以DDR电源为参考。

(9)菊花链需要得到仿真验证或芯片Layout Guide要求(一般主控支持读写平衡的才支持菊花链)。

DR走线等长规则

(1)数据线以DQS为基准等长,地址线、控制线、时钟线以时钟线为基准等长。

(2)数据线最大长度尽量不要超过2500mil,组内长度误差范围控制在±25mil,DQS与时钟线长度误差控制在±250mil,单片DDR的最大误差不超过1000mil。

(3) 地址线误差范围控制在±100mil,DQS、时钟差分对内误差范围控制在±5mil,设计阻抗时,使对内间距不超过2倍线宽。信号线实际长度应当包括器件管脚的长度,尽量取得器件管脚长度。

在处理DDR的时候需要注意的问题

(1)需要保证DDR信号有完整的参考平面。

(2)DDR的等长要符合数据手册上面的要求,在空间充足的情况下把误差尽量做小一点。

(3)等长的时候需要满足3W原则。

(4)与DDR无关的信号与电源不可以跨越DDR的区域。

(5)等长尽量不要在BGA里面绕线。

(6)重要信号,如差分在空间允许的情况下做包地处理。

(7)任何非DDR部分的信号,不得以DDR电源作为参考平面。

(8)所有DDR信号与参考平面的边缘要保持40mil左右的间距。

(9)DDR做完之后给DDR区域打上一圈地过孔。

(10)所有DDR信号需要严格按照数据手册上面的阻抗要求来进行设计。

(11)DDR部分在布局的时候应该做到远离干扰源。

2860

2860