简介

数字音频通信有I2S、PCM、AC97等。嵌入式音频领域通常使用I2S总线通信。I2S的全称是 Inter-IC Sound,中文翻译为“电路里的声音”。为了尽量不占用CPU资源,经常搭配DMA搬运数据。本文介绍I2S的开发和调试的经验。

系统结构

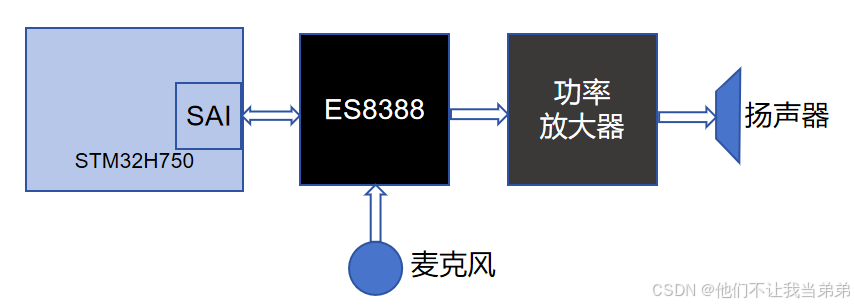

-

硬件

本文使用正点原子的开发板,使用STM32H750作为系统主控,ES8388为音频编解码芯片。ES8388具有编码和解码功能,可同时编码(模拟信号->数字信号)MCU发送的音频数据,输出到扬声器,又能解码(数字信号->模拟信号)麦克风数据,输入到MCU内。

图:系统结构

ES8388 是一款高性能、低功耗、高性价比的立体声多媒体数字信号编解码器。

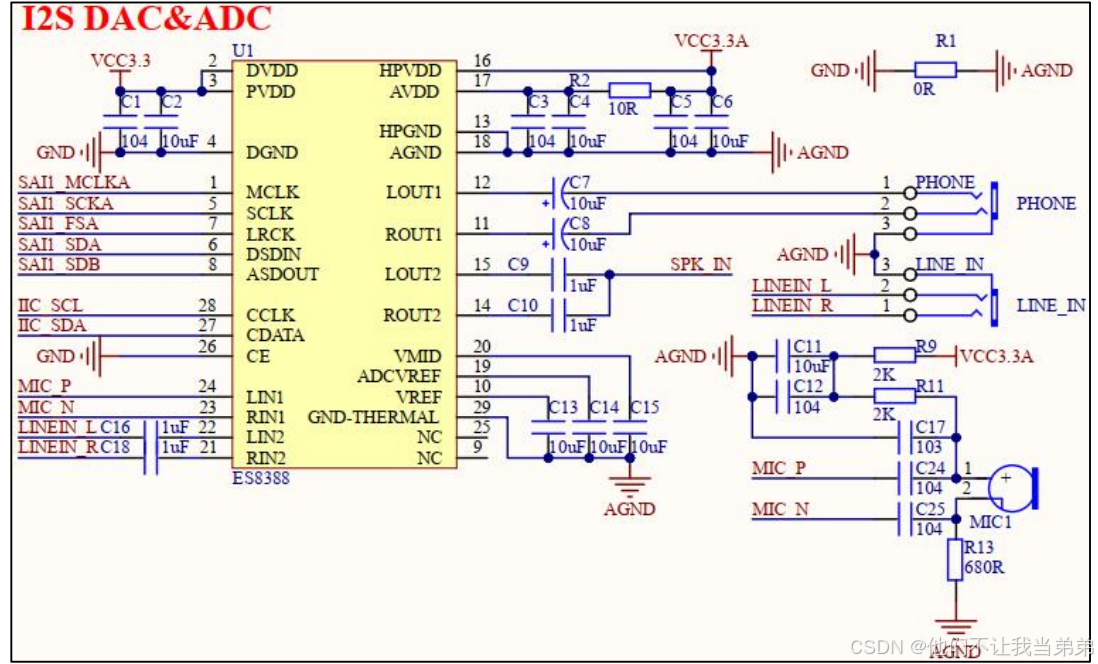

图:《北极星硬件参考手册 V1.1》ES8388原理图

I2S协议标准

在统一的I2S硬件接口下,出现了多种不同的数据格式,可分为左对齐(MSB)标准、右对齐(LSB)标准、I2S Philips标准、AC97(Audio Coder97)。

一帧数据包含两个左右声道,WS表示左右声道。单帧一个声道内有16/24/32位数据,数据按照CK时钟频率发送。由于信号在命名上有多种,本文以WS表示声道,CK表示位时钟,Channel表示一帧里的一个声道,Frame表示一帧数据,MCLK表示提供给编解码器的主时钟。

-

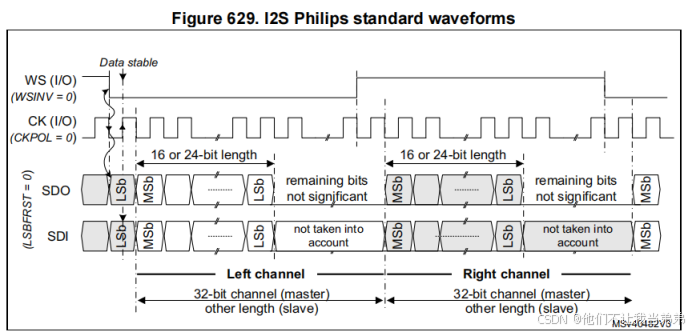

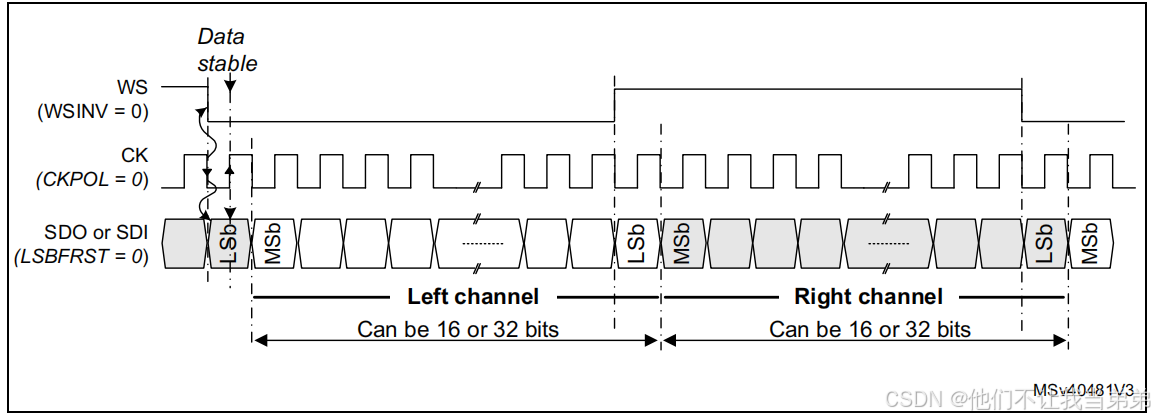

I2S Philips标准

In this standard, the WS signal toggles one CK clock cycle before the first bit (MSb in I2S Philips standard) is available. A falling edge transition of WS indicates that the next data transfered is the left channel, and a rising edge transition indicates that the next data transfered is the right channel.

I2S Philips标准总结:

1: 数据按顺序从WS跳变后的CK第二个时钟发送。

2:在WS低电平表示左声道。

-

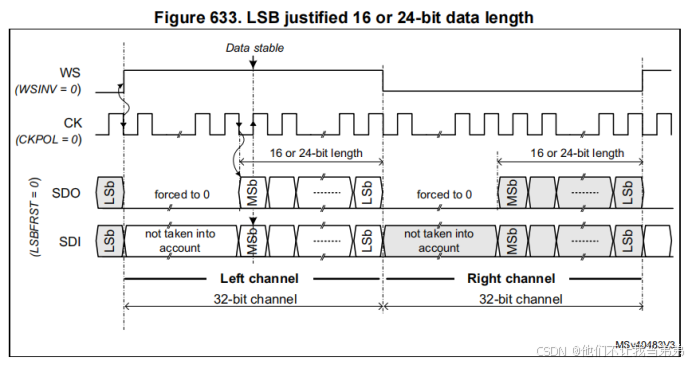

LSB justified 标准

LSB右对齐标准,声道数据往右边对齐。

LSB justified 标准总结:

1:数据按顺序从WS跳变后的第N个CK时钟后发送,发送到最后一个数据位刚好是声道数据结尾。

2:在WS高电平表示左声道。

软件配置

-

SAI接口

SAI接口SAI(Serial Audio Interface)是一种用于音频数据传输的串行接口,使用相较于STM32的SPI/I2S接口开发更为简便,且支持的音频格式更多。一个SAI模块支持两路数据流,通常一路用来录音,一路用来播放声音。

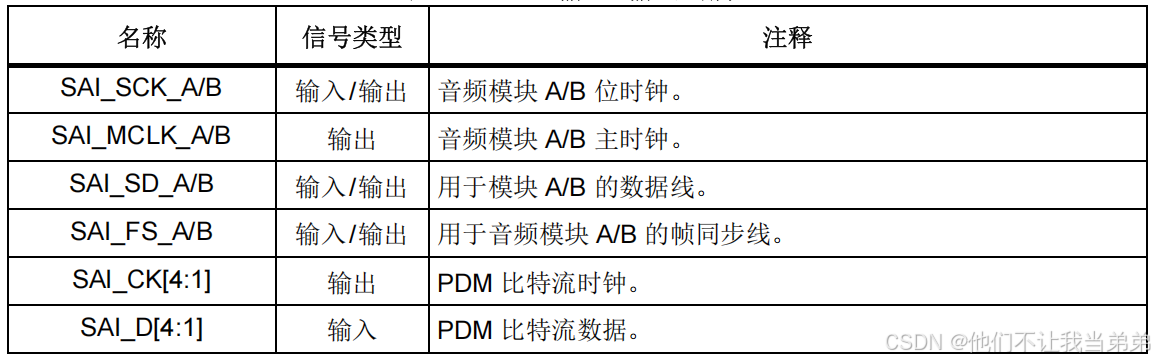

表:SAI引脚定义

-

SAI和I2S管脚对应表

管脚的叫法也有很多种,注意分辨。位时钟可能叫BCK、CK、SCLK,声道时钟可能叫LRCK、LCK、WS。

图:飞利浦I2S标准时序

表:管脚对应表

| SAI | I2S | 意义 |

| SAI_SCK | BCLK/CK | 位时钟 |

| SAI_MCLK | MCLK | 系统时钟 |

| SAI_SD |

MOSI/MISO/ SDO/SDI | 数据 |

| SAI_FS | LRCK/WS | 声道时钟 |

-

主从关系

两端设备可配置主从模式,主设备提供时钟信号。设备一端配置接收模式,另一端配置成发送模式,接收模式和发送模式和主从关系无关。

-

IO配置

IO根据主从关系配置,设计的时候注意输入输出口名称定义,芯片输入口可能定义为SDI/MOSI/MISO,要注意定义!!!

- 主机端的时钟信号(MCLK、CK、WS)配置成输出和上拉,需要提供较强的驱动力。

- 从机端的时钟信号(MCLK、CK、WS)配置成输入模式。

- 发送端的输出口配置成输出和上拉,接收端的输入口配置成输入。

-

速率计算

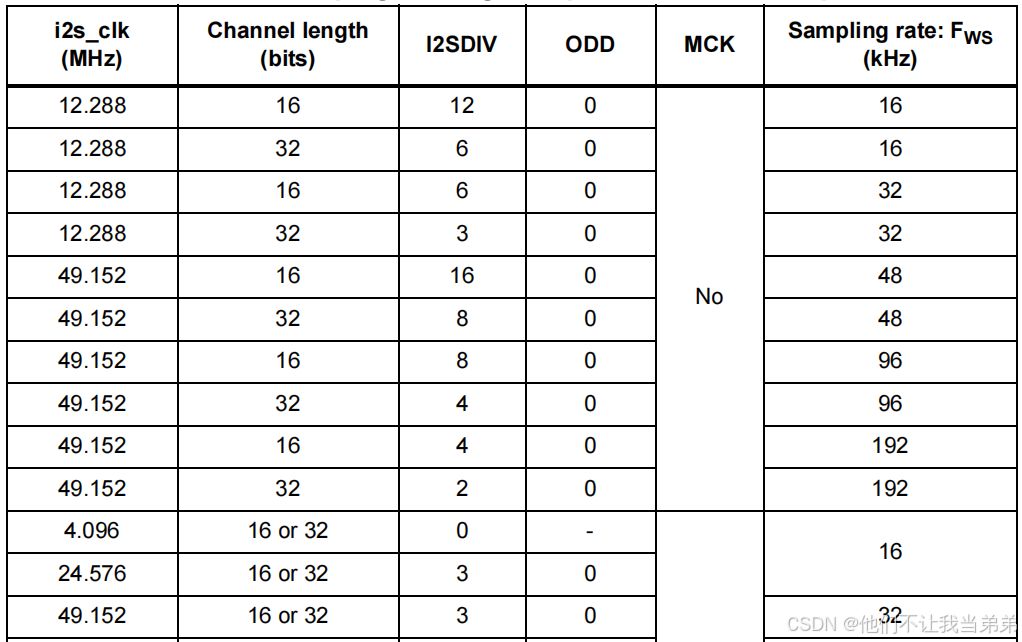

I2S传输涉及到三个时钟信号MCLK、CK、WS。硬核I2S配置MCLK即可,模拟I2S需要关注更多细节。

通常情况下:1*MCLK=4*CK=256*WS。如下图可以看到MCLK和WS的对应关系,和每声道有效数据位(16/32)有关。

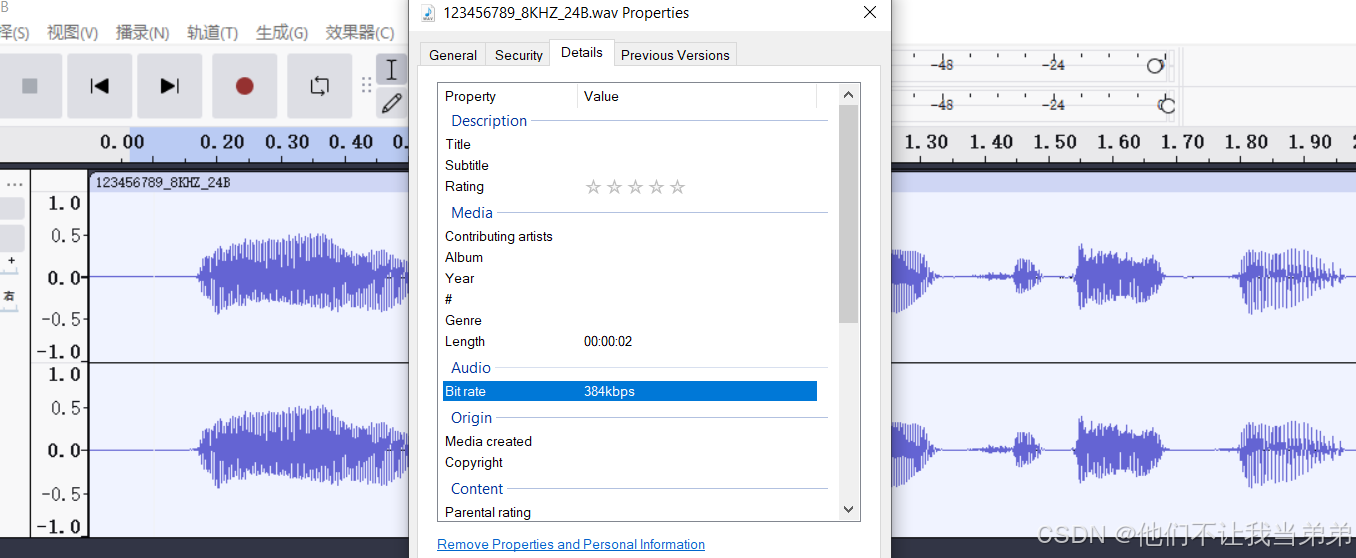

调试中需要输入外部音源,用来做播放测试。因此读懂采样率、码率、声道数量、有效数据位,是必要的。如下图,这个音频是手动创建的一个音频,2声道,采样率8KHZ,单声道有效数据24位,采样率就是声道的频率。

码率计算=声道数* 采样率 * 单声道有效数据=2 * 8KHZ * 24b = 384kbps。

DMA传输

在STM32H750平台上,DMA1一次性最大可以传输64KB个字节。假设传输64K数据,仅使用CPU的情况下,采样率8KHZ,码率384kbps的数据,需要占用CPU时间(64k*8b)/(384kbps) = 1.3秒。而采用DMA技术,传输时间同样需要1.3秒,而在传输期间,可以挂起音频数据传输线程,执行其他任务,等待DMA传输完成的中断。

音频传输和存储器类的数据传输不同,音频数据不允许有传输的间隔,如果出现传输间隔会造成声音”卡顿“的现象。因此采用”乒乓操作“来传输数据,也就是DMA传输第一个块的数据,预先拷贝第二块数据到指定缓存内,每次传输前数据都处于准备好的状态,代价就是声音稍显“迟滞”和额外的内存消耗,“迟滞”通常不会被人耳察觉到。

表:DMA配置

| 传输方向 | 内存到外设 |

| 传输数据大小 | 16KB |

| 突发模式 | 关闭 |

| 循环模式 | 开启 |

| 中断模式 | 传输完成中断 |

| 数据宽度 | 32位 |

调试中遇到的问题

声音卡顿

原因和解决办法如DMA传输章节中提到,音频数据不允许有传输的间隔,如果出现传输间隔会造成声音”卡顿“的现象。

电磁噪音

编解码芯片对时钟的要求高,对于高频信号(MCLK),应采取适当措施保证信号质量,如缩短走线,远离高频信号等。如果使用杜邦线连接更要注意。

1281

1281

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?