TI的SERDES芯片,图片来自官方数据手册,下载地址TLK2711 数据表(PDF) - Texas Instruments。

1.主要特点:

(1)线速率1.6~2.7Gbps,支持背板、铜线和光纤转换器接口;

(2)采用2.5V供电,低功耗;

(3)可编程预加重控制;

(4)片内8B/10b编解码;

(5)内部自测(BIST);

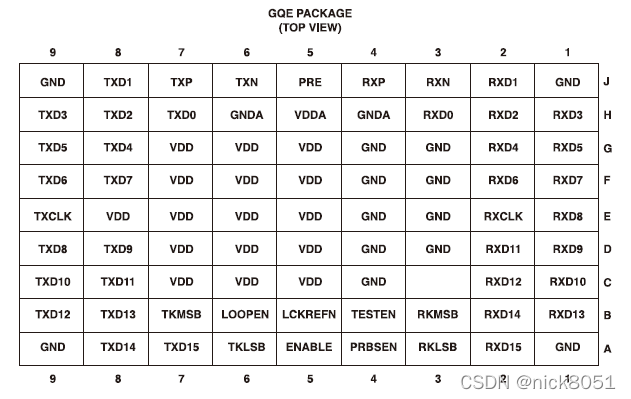

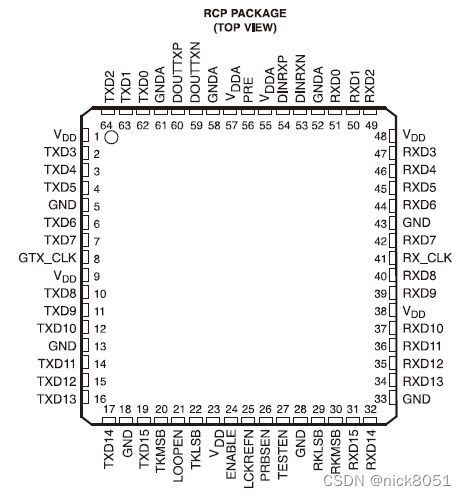

2.封装与引脚

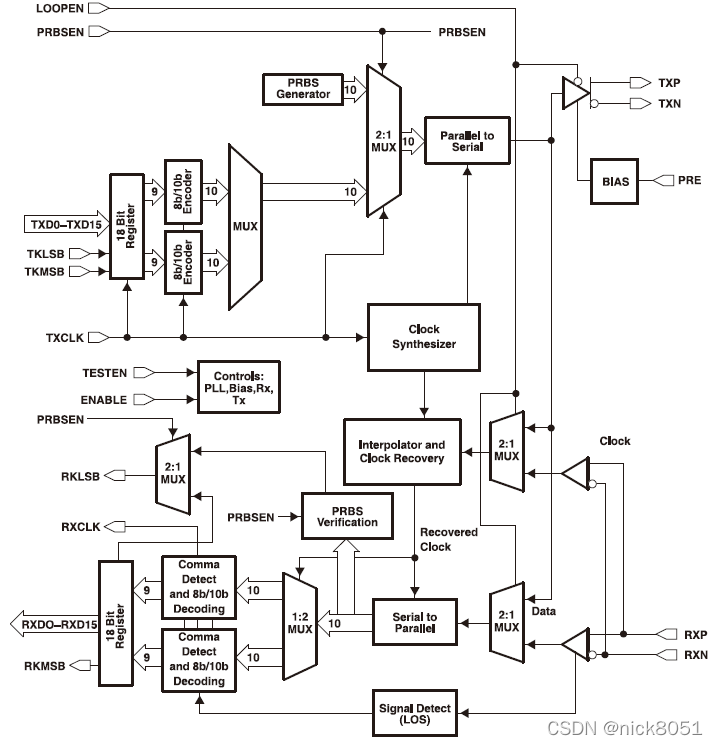

3.内部结构

4.引脚说明

(1)LCKREFN:高电平下RXCLK与接收数据绑定。低电平下RXD、RXCLK、RKLSB、RKMSB为高阻态,单工发送时用。

(2)LOOPEN:回环使能,高电平有效。

(3)PRE:预加重,远距离传输时对信号作补偿。

(4)PRBSEN:伪随机二进制序列测试使能,高电平有效,PRBS测试通过时RKLSB会置高。

(5)RKLSB:K码标志,表示RXD0-7上收到K码;PRBSEN开启时代表测试通过。

(6)RKMSB:K码标志,表示RXD8-15上收到K码。

(7)RXCLK:恢复时钟,和RXD同步,频率是串行时钟的20分之一。

(8)RXD、TXD:16位数据总线。

(9)RKLSB、RKMSB:发送端的K码。

(10)TXCLK:参考时钟,频率80MHz-135MHz;在时钟上升沿对TXD采样。

5.注意事项

(1)空闲时需要发送K码以保证恢复时钟;

(2)理论上TXCLK需要和TXD相位相差180度,实际条件下可能不是180度最佳,需要考虑数据线和时钟线在FPGA内部的延时;

本文介绍了TI的TLK2711A SERDES芯片,该芯片支持1.6至2.7Gbps的数据速率,适用于背板、铜线和光纤接口。其特性包括2.5V供电、低功耗、可编程预加重控制、8B/10b编解码以及内部BIST功能。内容涵盖了芯片的封装、引脚说明、内部结构和使用注意事项,如发送K码以保持恢复时钟稳定,以及考虑FPGA内部延时对相位匹配的影响。

本文介绍了TI的TLK2711A SERDES芯片,该芯片支持1.6至2.7Gbps的数据速率,适用于背板、铜线和光纤接口。其特性包括2.5V供电、低功耗、可编程预加重控制、8B/10b编解码以及内部BIST功能。内容涵盖了芯片的封装、引脚说明、内部结构和使用注意事项,如发送K码以保持恢复时钟稳定,以及考虑FPGA内部延时对相位匹配的影响。

1880

1880

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?