1.软件概述

>>NS-LCR测试仪程控软件用于测量BNT基陶瓷材料、金属样块、变压器、电阻等的阻抗、电容值和损耗值,可以根据设置的时间间隔和频率点进行相应测试,实现整体测试过程的自动化。

2.软件特点

>> 系统为LCR表提供包括TCP/LAN/以太网、USB、GPIB、TTL、RS232、RS485、蓝牙的连接方式;

>>测试的时间间隔和频率点可手动设置;

>>测量的、电容、损耗等数据实时采集显示、自动保存本地,并可以在系统上实时可视化显示;

>>测量数据可通过改变X轴和Y轴内容绘制不同形式的趋势图;

>>系统实时显示测试设备已经运行的总时间;

>>用户可通过选择不同的测试仪器完成对产品的测试;

>>系统中测试参数的配置可根据测试项目的不同进行相应的设置;

>>用户可根据不同被测产品选择不同的测试项目;

>>产品测试信息可实时编辑,所有测试数据均保存至本地,方便随时查询;

>>自动生成测试报告,用户可根据需要定制报告模板;

>>操作简单,节约人力资源,提高了测试效率;

>>软件提供可扩展接口,支持其它仪器仪表的自动化测试接口接入。

3.兼容仪器

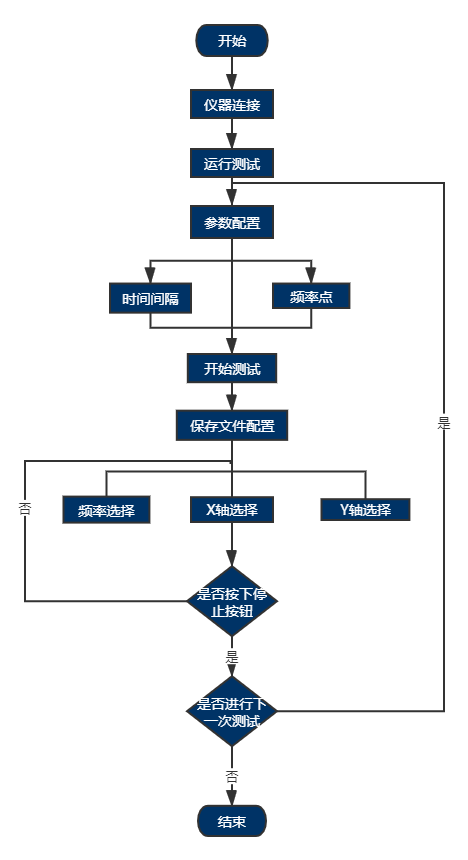

4.软件流程图

5.软件界面

看完纳米软件对于LCR测试仪程控软件

的介绍,是不是想马上去体验看看呢?索取产品资料,申请免费试用19991855753同微信

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?