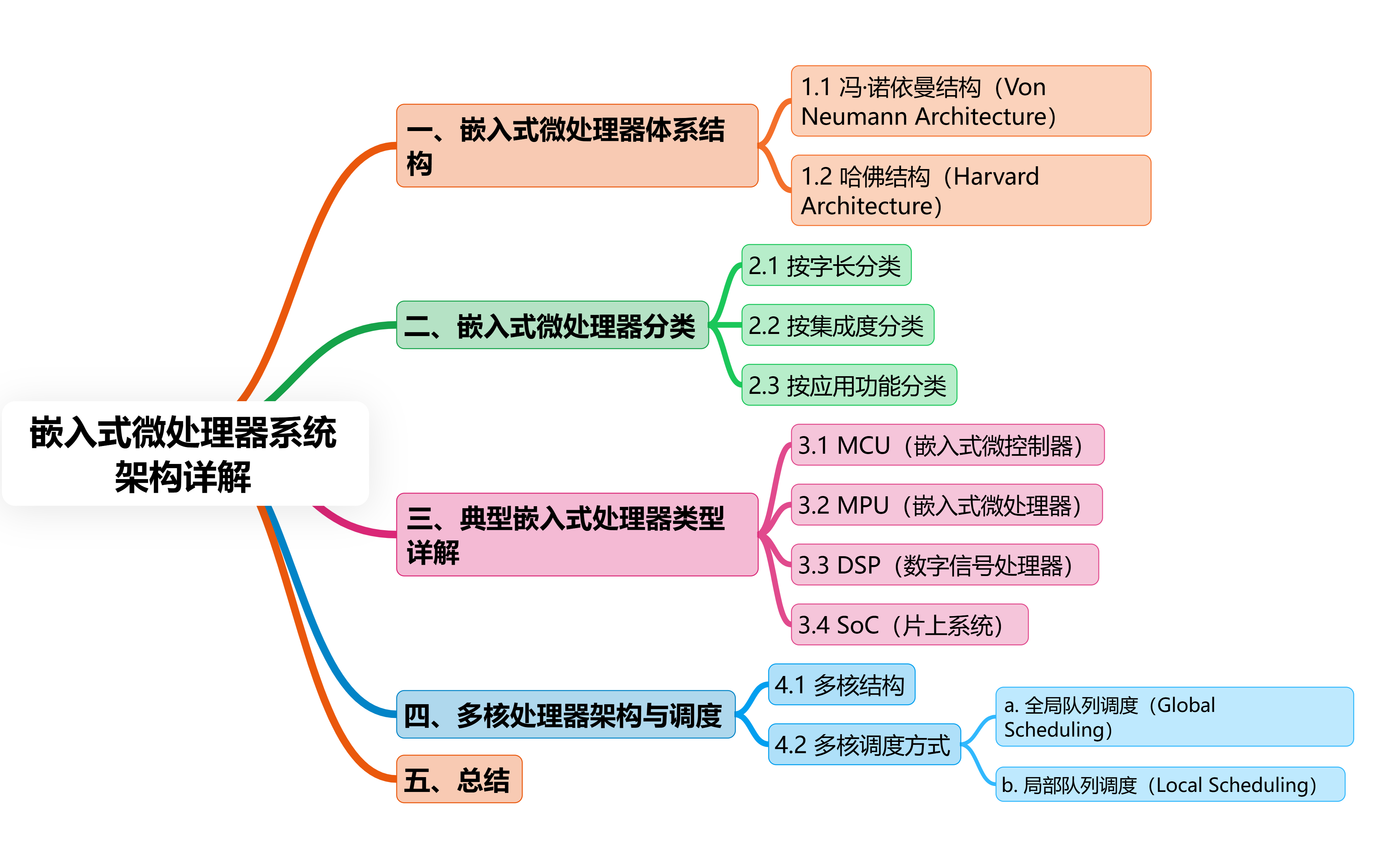

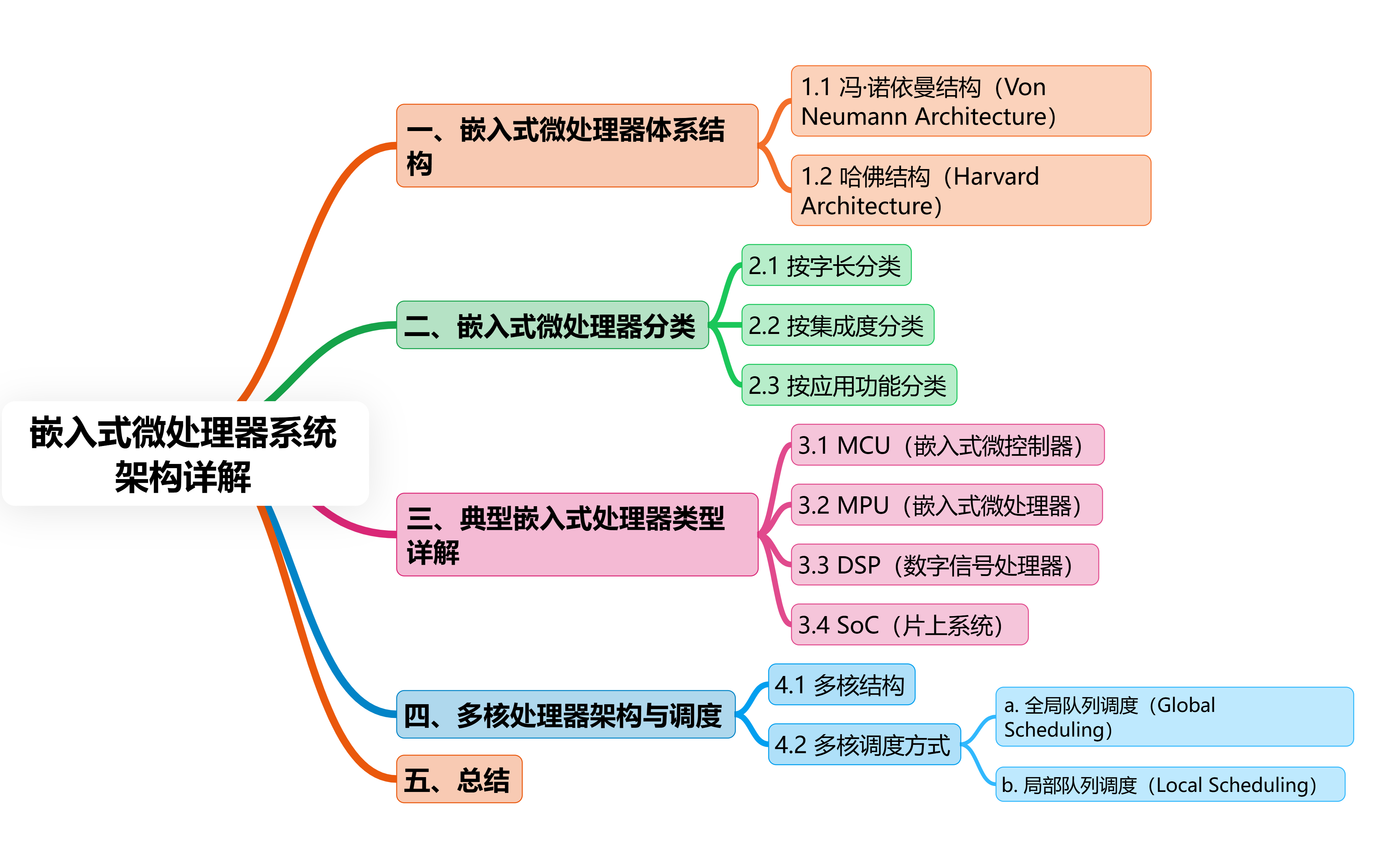

目录

1.1 冯·诺依曼结构(Von Neumann Architecture)

1.2 哈佛结构(Harvard Architecture)

一、嵌入式微处理器体系结构

1.1 冯·诺依曼结构(Von Neumann Architecture)

冯·诺依曼结构是传统计算机体系结构,又称普林斯顿结构,其特点为:

-

程序和

嵌入式微处理器架构与分类详解

嵌入式微处理器架构与分类详解

目录

1.1 冯·诺依曼结构(Von Neumann Architecture)

1.2 哈佛结构(Harvard Architecture)

冯·诺依曼结构是传统计算机体系结构,又称普林斯顿结构,其特点为:

程序和

2258

2258

2566

2566

4536

4536

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?