存储器

存储器概述

存储器分类

按存储介质分类

1.半导体存储器:集成度高、体积小、功耗低、存取时间段。

2.磁表面存储器:磁头、载磁体。

3.光盘存储器:激光、磁光材料。

按存储方式分类

1.随机存储器(RAM):随机存取、可读可写、组成主存的主要器件。

2.只读存储器(ROM):在程序执行过程中只读。

3.顺序存储器:串行访问存储器,与存储位置有关。

4.直接存储器:部分串行访问,直接定位到读写数据块,在读写数据块时按顺序进行,例如:磁盘。

5.相联存储器:按内容访存。

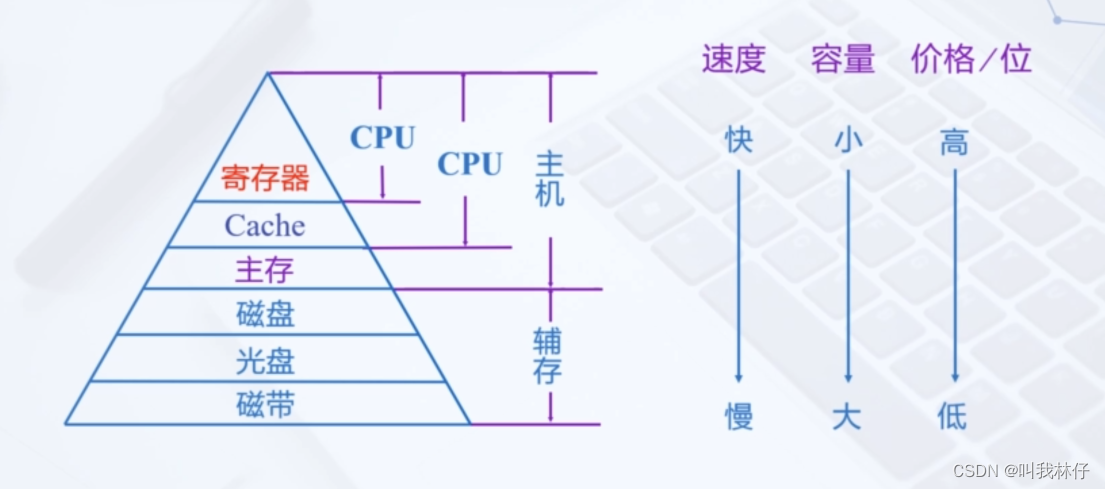

按在计算机中的作用分类

主存储器:直接和CPU交换信息,速度快、容量小、价格高

- RAM(随机存储器):静态RAM、动态RAM

- ROM(静态存储器):MROM、PROM、EPROM、EEPROM

辅助存储器:不能直接和CPU交换信息,速度慢、容量大、价格低。

高速缓冲存储器(Cache):

闪速存储器(flash memory):

存储器的层次结构

存储系统三个主要性能指标的关系

为了是存储器达到最高效果,往往把不同的存储器,按一定层次结构进行组合。

寄存器速度最快容量最小价格最高,通常位于CPU(中央处理器)内部,存放将要运行的程序或数据。

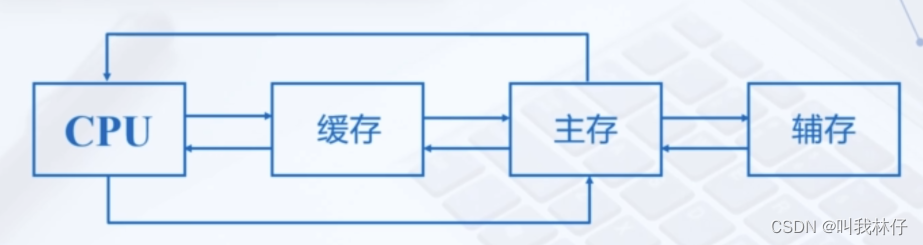

寄存器通过缓存Cache于主存进行信息交换,主存和辅存也可进行信息交互。

逻辑图如下:

通过缓存我们就可以将主存内容调入缓存,CPU直接访问缓存,就可以使速度接近缓存容量和价格接近主存。

主存和辅存,辅存内容调入主存,CPU访问主存速度接近主存容量和价格接近辅存。

主存储器

主存的基本组成

- 存储体

- 地址译码驱动器

- 度/写电路

- 控制电路

数据在存储器中的存放

- 编制方式:字节编址

- 多字节数据在内存的地址安排分为:大端方案、小端方案。

- 多字节数据在存储器中的存放:满足边界对准原则。

大端方案:

最高有效字节在最前面的方式称为大端法,例如假设变量x类型为int型,位于地址0x100的地方,其16进制值为0x12345678,地址范围为0x100到0x103字节。

| 0x100 | 1x101 | 1x102 | 1x103 |

|---|---|---|---|

| 12 | 34 | 56 | 78 |

小端方案:

最低有效字节在最前面的方式成为小端法,这正好和大端法相反,仍然用大端法中举的例子说明:

| 0x100 | 1x101 | 1x102 | 1x103 |

|---|---|---|---|

| 78 | 56 | 34 | 12 |

边界对准原则:

要想理解边界对准原则首先要知道:字、字节、位三者之间的关系:现代计算机的字长通常为16位(2个字节)、32位(4个字节)、64位(8个字节)。,1字节=8位。位表示二进制位。位是计算机内部数据储存的最小单位,11010100是一个8位二进制数。一个二进制位只可以表示0和1两种状态;两个二进制位可以表示00、01、10、11四种状态;三位二进制数可表示八种状态。

边界对齐通俗的定义就是K字节大小的数据必须存储在K的整数倍的地址上。

尽量减少访问次数。

主存的技术指标

存储容量

-

主存存放二进制代码的总位数

存储容量 = 存储单元个数 x 存储字长 -

容量可用字节/字的总数来表示

某机容量位64K x 16

表示有64K个存储单元,每个存储单元字长为16位

用字节总数表示容量:(64K x 16) / 8 = 128KB

存储速度

- 存取时间

存储器的访问时间分为读出时间和写入时间

包括CPU发出读命令,从主存存储单元获取数据并返还给数据总线,接到写命令,将数据总线上的数据写入到选中存储单元的时间。 - 存取周期

连续两次独立的存储器操作

(读或写)所需的最小间隔时间包括读周期和写周期

存储带宽

- 单位时间内存储器存取的信息量。单位:位/秒(bps),字节/秒(Bps)

例1:存取周期位500ns,每个存取周期访问16位,则他的带宽:16/500ns = 32M位/秒。

例2:存取频率位2MHZ,每个存取周期访问16位,则它的带宽:2M x 16 = 32M位/秒

半导体存储芯片

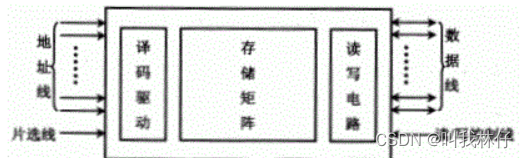

半导体存储芯片的基本结构

半导体存储芯片由译码驱动电路、存储矩阵、读写电路、地址线、数据线、控制线、片选线组成。其中,译码驱动电路、存储矩阵、读写电路属于核心结构。

存储矩阵用来存储0/1代码,地址线、数据线主要用来连接CPU和外部设备。现在假设CPU或者外部设备给出地址,表示要存/取的数据在存储矩阵的哪个存储单元中,然后经过译码驱动电路,选择对应的存储单元,从而完成存/取数据。

地址线是单向的,由CPU指向存储器,或者由I/O设备的控制器指向存储器。数据线是双向的。由地址线和数据线可以计算出芯片的容量

例如:

| 地址线(单向) | 数据线(双向) | 芯片容量 |

|---|---|---|

| 10 | 4 | 1K x 4位 |

| 14 | 1 | 16K x 1位 |

片选线,也叫做芯片选择信号,指出这次存/取操作给出的地址是不是这个存储芯片的地址。半导体存储芯片的片选线一般有两种标识方式

两者都是低电平有效

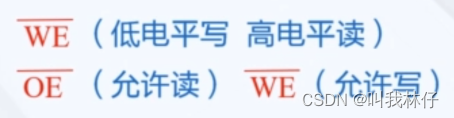

读写控制线

有的芯片只有WE引脚,低电平表示写,高电平读;有的芯片同时具有OE(读信号)、WE(写信号)都是低电平有效。

半导体存储芯片的译码驱动方式

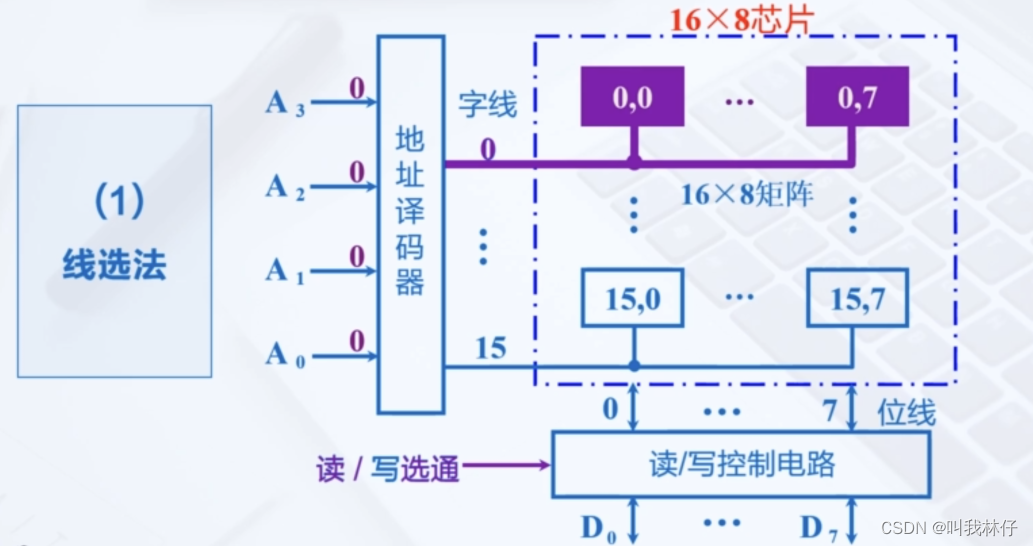

- 线选法

在上图中,有A0-A3的4位地址,那么24表示有16个存储单元,那么每个存储单元可以存储多少位?图中给出的数据线是从D0-D7,一共8位。综合起来,就表示这是一个16K×8的存储器。

假设地址译码器给出的地址是全0,进行译码过后,只有0这根线是有效的,其他的都是无效的。现在进行的是读操作,那么就会控制读/写控制电路打开,使得数据可以从存储矩阵输出到数据总线上。只有给定的单元才可以进行输出。

也就是说

现在假设有1M×8的存储芯片,地址线有20根,经过译码器译码后就有1M条线,每给出一个地址,1M条线中,只有一条有效。而1M条线,就是1000000条线,做在芯片中将会非常密集,这么高的集成度很难做到。

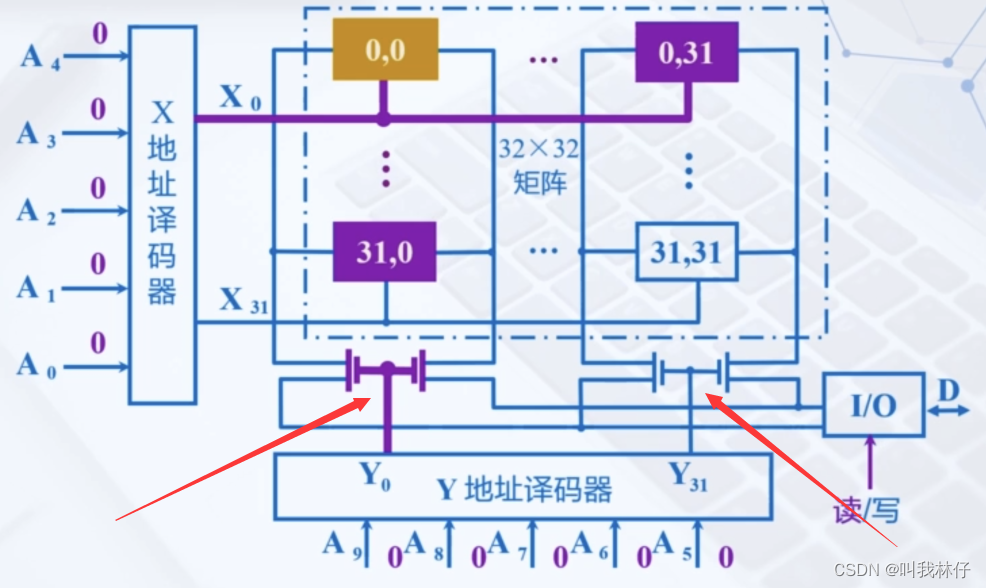

- 重合法

在线性法中,存储单元的布局方法是一个线性的数组;而在重合法中,存储单元的布局方法是二维的数组。

在重合法中,将地址分成了两部分,一部分是X,另一部分是Y,也可以叫做行列地址。行列地址分别进行译码,只能有一根线是有效的。具体工作过程:

假设给出的行列地址都是全0,行列地址进行译码后只有(0.0)这条线是有效的。只有这条线上的存储单元被选中。那么这时候,Y0这条线上的开关就会打开,数据就会通过这个开关进行数据输出。在这个过程当中,X0上的除了Y0上的存储单元的数据会进行输入以外,其他的存储单元上的数据一样会进行输出,但是,当数据经过Y31线上的开关时,由于这条线是无效的,数据会被拦截,所以,数据就输出不了,所以数据没有到数据线去。那么Y0上的除了X0的存储单元的数据会进行输入以外,其他的存储单元上的数据一样会进行输出,同样的道理,就不另外解释了。

静态RAM基本单元电路

静态RAM(SRAM,即static RAM)

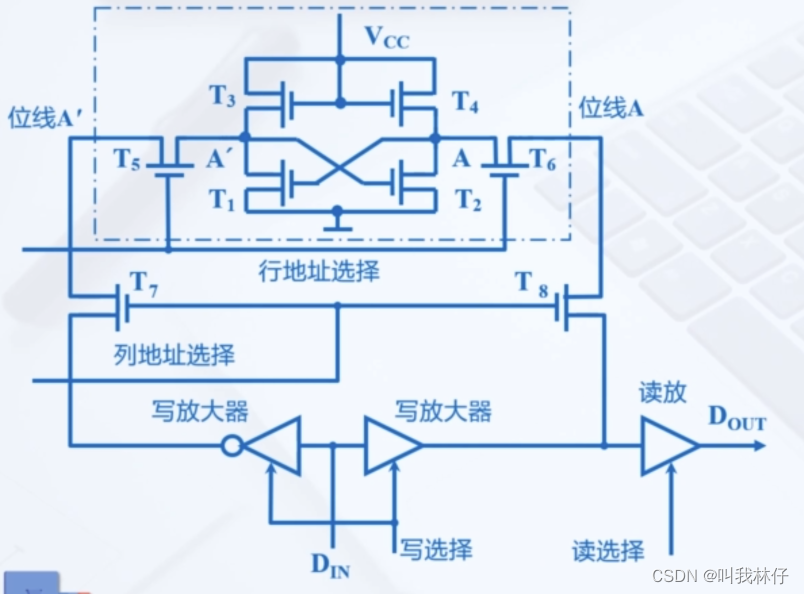

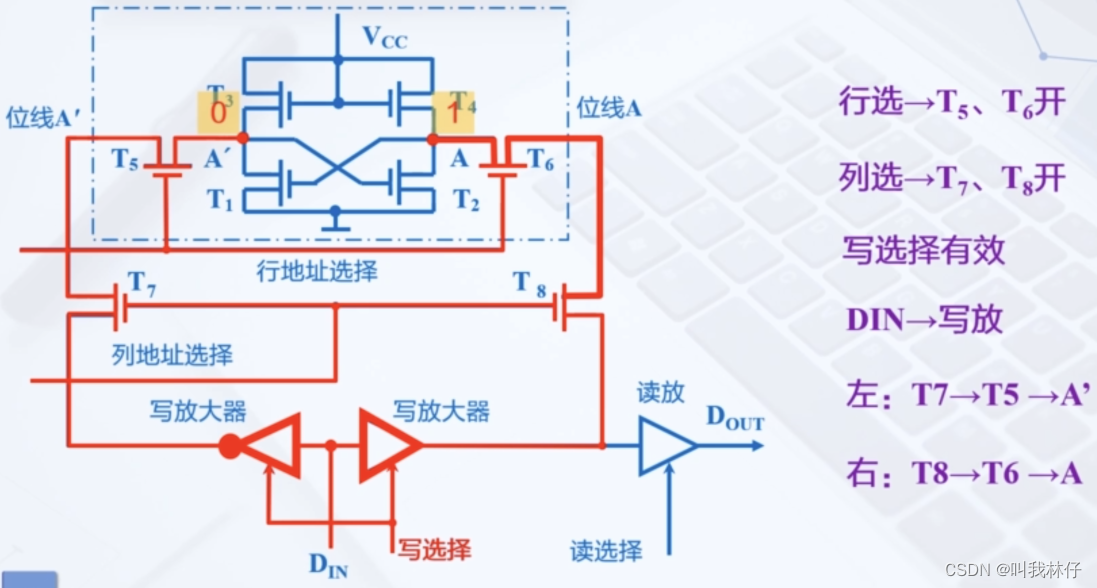

如图是一个由6个MOS管组成的基本单元电路。图中T1-T4是一个由MOS管组成的触发器基本电路,解决了用什么样的电路存放0,1。T5-T6犹如一个开关,受行地址选择信号控制,起到译码驱动作用。由T1~T6这6个MOS管共同构成一个基本单元电路。

T7,T8受列地址选择控制,分别与位线A’和A相连,它们并不包含在基本单元电路内,而是芯片内同一列的各个基本单元电路所共有的如下图:

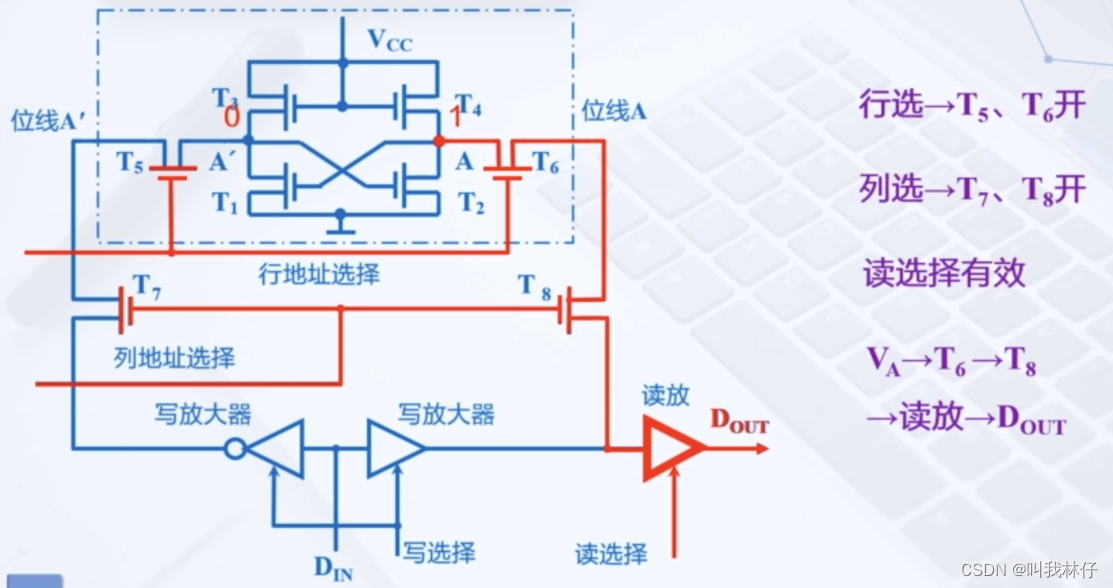

- 读操作

假设触发器已存有“1"信号,即A点为高电平。当需读出时,只要使行、列地址选择信号均有效,则T5,T6,T7,T8均导通,A点高电平通过T6后,再由位线A通过T8,作为读出放大器的输人信号,在读选择有效时,将“1”信号读出

由于静态RAM是用触发器工作原理存储信息,因此即使信息读出后,它仍保持其原状态,不需要再生。但电源掉电时,原存信息丢失,故它属易失性半导体存储器。 - 写操作

写入时不论触发器原状态如何,只要将写人代码送至图的D(IN)端,在写选择有效时,经俩个写放大器,使两端输出为相反电平。当行、例地址选择有效时,使T5、T6、T7、T8导通,并将A与A’点置成完全相反的电平。这样,就把欲写入的信息写入到该基本单元电路中。如欲写入1,即D(IN)=1,经两个写放大器使位线A为高电平,位线A’为低电平,结果使A点为高,A’点为低,即写入了“1”信息。

写入时不论触发器原状态如何,只要将写人代码送至图的D(IN)端,在写选择有效时,经俩个写放大器,使两端输出为相反电平。当行、例地址选择有效时,使T5、T6、T7、T8导通,并将A与A’点置成完全相反的电平。这样,就把欲写入的信息写入到该基本单元电路中。如欲写入1,即D(IN)=1,经两个写放大器使位线A为高电平,位线A’为低电平,结果使A点为高,A’点为低,即写入了“1”信息。

动态RAM

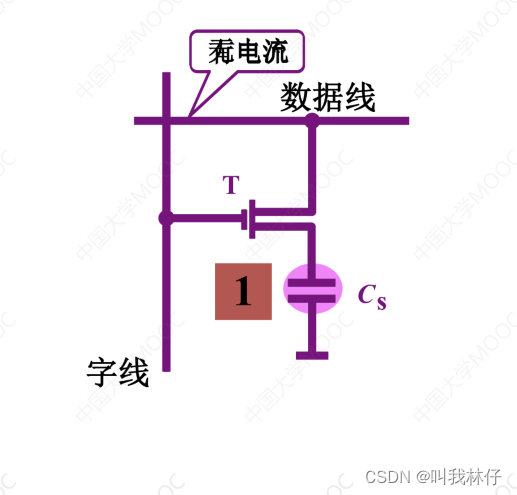

单管动态RAM基本单元电路

存储数据:

电容Cs有电荷存“1”,无电荷存“0”

读出:

数据线无电流为“0”,有电流为“1”

写入:

电容Cs充电为“1”,放电为“0”

动态RAM刷新

刷新的概念

- 将原存信息读出,再由刷新放大器形成原信息并重新写入的过程。

- 刷新必须是周期进行的,即在一定时间内,对动态RAM的全部基本单元电路做一次刷新,这段时间成为刷新周期。

- 刷新是对动态RAM的存储矩阵一行一行进行。

刷新的方法

- 集中刷新

- 分散刷新

- 异步刷新

集中刷新:在规定的一个刷新周期内,对全部存储单元集中一段时间逐步进行刷新,刷新时停止读写操作。因此集中刷新会存在“死区”,但读写操作不受刷新的影响,系统的存取速度比较高。

分散刷新:把刷新一行的操作分散到每个存取周期内进行。系统的存取周期t被分为两部分:

前一部分进行读写操作

后一部分进行刷新操作

在一个存取周期内刷新存储矩阵的一行,他的优点在于没有“死区”,缺点是加长了存取周期,降低了系统的速度且刷新过于频繁,没有充分里利用刷新间隔。

异步刷新:他是集中刷新与分散刷新的结合;既缩短了“死区”又不延长存取周期;充分利用刷新间隔。

根据行数分段,段内集中刷新,刷新一遍;段间分散刷新,刷新一遍。

动态RAM与静态RAM的比较

| DRAM | DRAM | |

|---|---|---|

| 存储原理 | 电容 | 触发器 |

| 集成度 | 高 | 低 |

| 芯片引脚 | 少 | 多 |

| 功耗 | 小 | 大 |

| 价格 | 低 | 高 |

| 速度 | 慢 | 快 |

| 刷新 | 有 | 无 |

只读存储器ROM

- MROM:由制造厂做成,用户不可进行更改

- PROM:可实现一次性编程的只读存储器

- EPROM:多次性编程,通过紫外线进行擦洗,但擦洗时间长,且只能对部分单元进行擦洗

- EEPROM:多次性编程,可用电擦写,进行局部擦写或全部擦写。速度更快

- Flash Memory

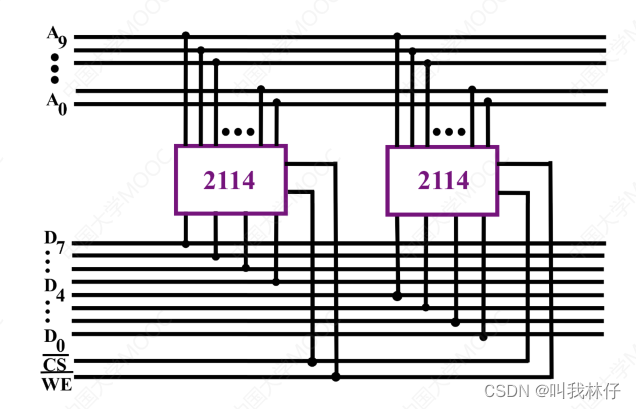

存储容量的扩展

位扩展

增加存储位数字数不变。

例如使用1K x 4位的芯片组成1K x 8位的芯片;

(1K x 8)/(1K x 4)= 2片

分析1K x 8位芯片共十根地址线即A0-A9,8根数据线。

两个1K x 4位芯片采取并联的方式如下:

两个芯片地址采用并联连接,数据线左侧芯片连接低位,右侧连接高位。

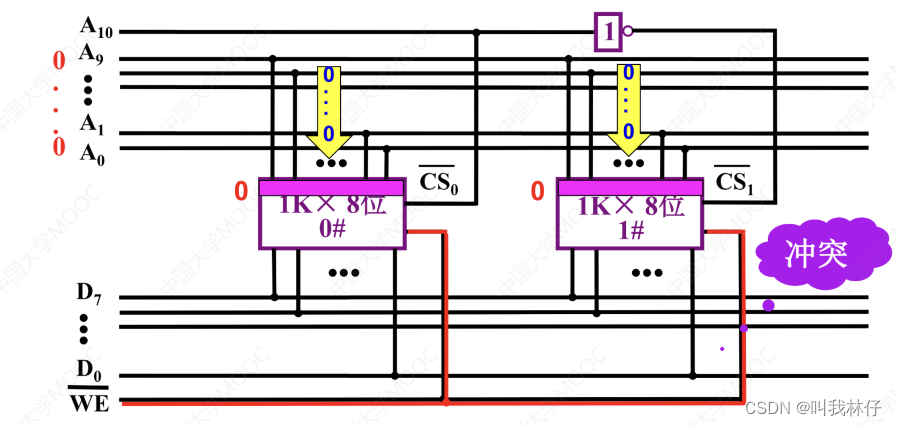

字扩展

增加存储字数,位数不变

例如使用1K x 8位的芯片组成2K x 8位的芯片;

(2K x 8)/(1K x 8)= 2片

增加存储字数,位数不变分析可得,改变片选信号如图:

此处A10作为片选信号,为1时选左侧芯片,为0时为右侧芯片。

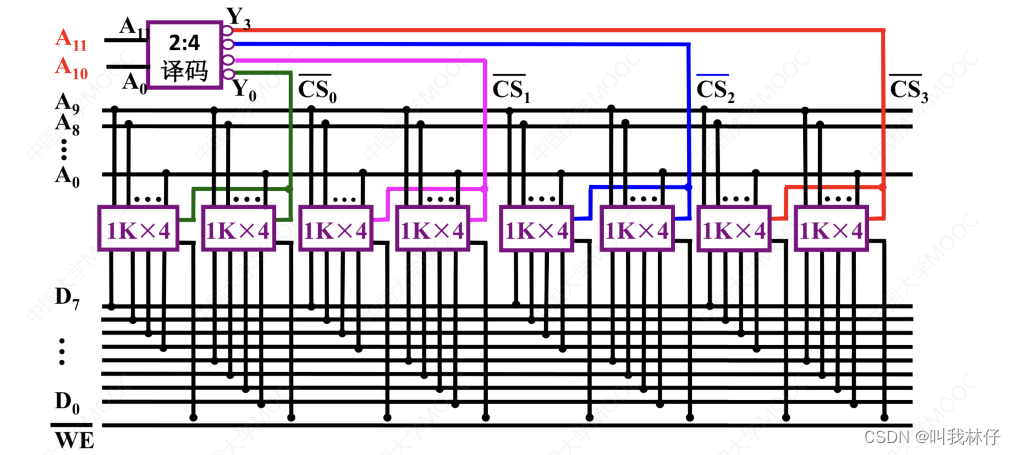

字位扩展

字数和位数同时增加,就将前两种方式组合

例如使用1K x 4位的芯片组成4K x 8位的存储器;

(4K x 8)/(1K x 4)= 8片

字数和位数同时增加应对芯片进行分组

4K/1K=4组

8/4=2片

也就是分成四组每组两片

组件片选信号不同,组内片选信号相同,也就是说需要四种不同的片选信号,这里我们选取二四译码器,不同芯片连接不同的数据线。

总而言之相同的片选信号增加的是位数,不同的片选信号增加的是字数。

本文详细介绍了存储器的分类、层次结构及关键技术指标,并深入探讨了半导体存储芯片的工作原理,包括静态RAM和动态RAM的区别,以及只读存储器的扩展方法。

本文详细介绍了存储器的分类、层次结构及关键技术指标,并深入探讨了半导体存储芯片的工作原理,包括静态RAM和动态RAM的区别,以及只读存储器的扩展方法。

6421

6421

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?