前言

最近在写一个程序中,想对存到FLASH中的结构体分配的大小做控制,希望分配的大小偶数字节大小。(因为读时是按16位读,如果奇数就可能读超了)如果结构体大小为奇数,就跳到断言处。

分析

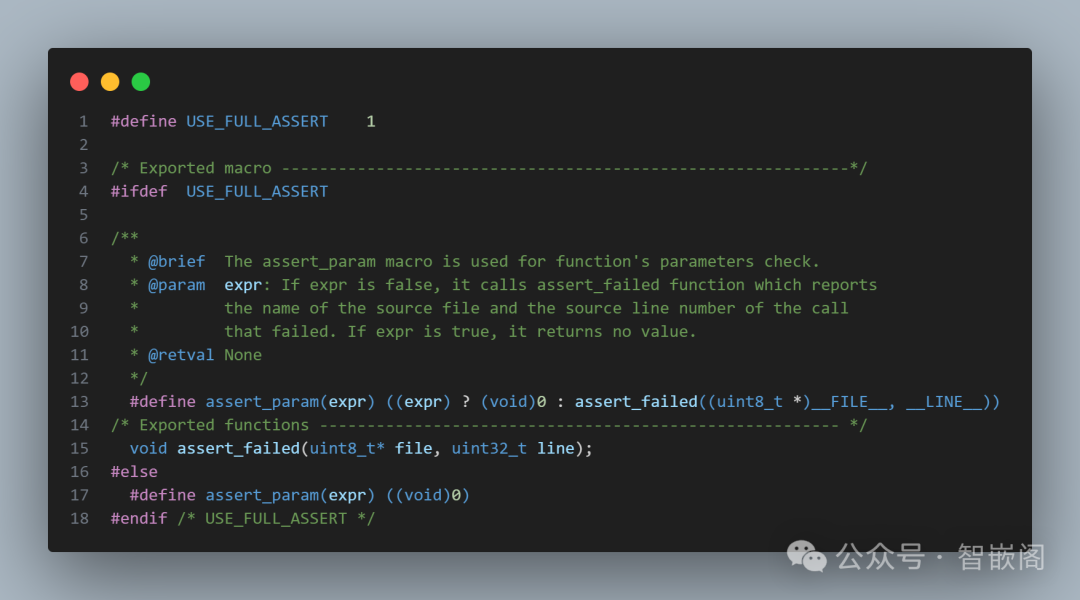

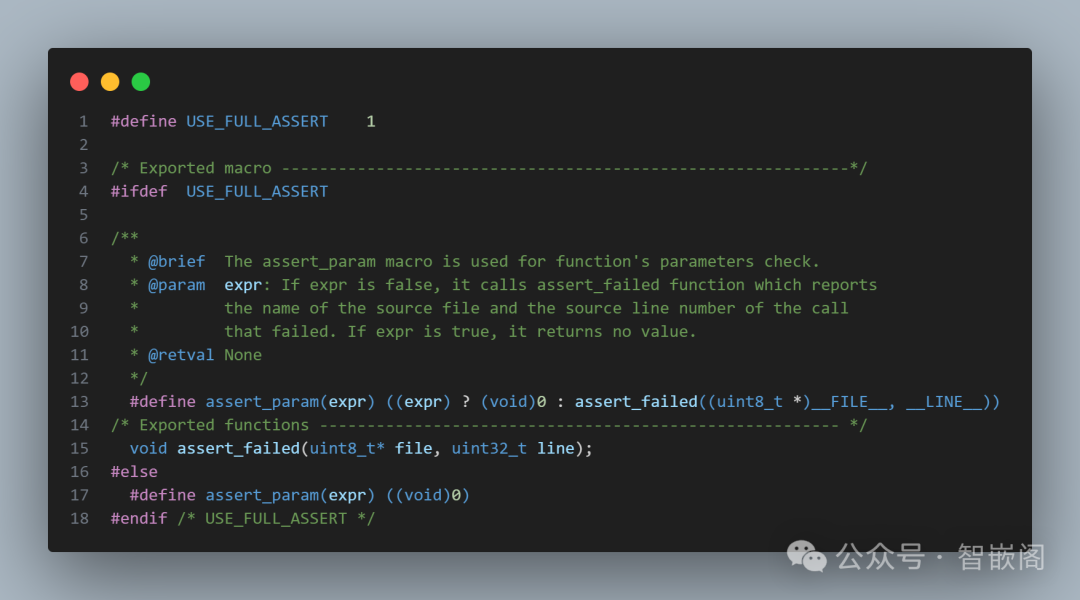

STM32F030的标准库有使用断言 在stm32f0xx_conf.h文件中进行了定义是否开启

其中去掉下面这一行的注释,使能它就可以使用了。

使用方法

附记

原来是打算在编译时,如果发现分配的结构体大小不对,最好能报错,而实际上是只有在运行仿真时,才会跳转到断言,如果大家有更好的方法,可以一起交流。

前言

最近在写一个程序中,想对存到FLASH中的结构体分配的大小做控制,希望分配的大小偶数字节大小。(因为读时是按16位读,如果奇数就可能读超了)如果结构体大小为奇数,就跳到断言处。

分析

STM32F030的标准库有使用断言 在stm32f0xx_conf.h文件中进行了定义是否开启

其中去掉下面这一行的注释,使能它就可以使用了。

使用方法

附记

原来是打算在编译时,如果发现分配的结构体大小不对,最好能报错,而实际上是只有在运行仿真时,才会跳转到断言,如果大家有更好的方法,可以一起交流。

1604

1604

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?