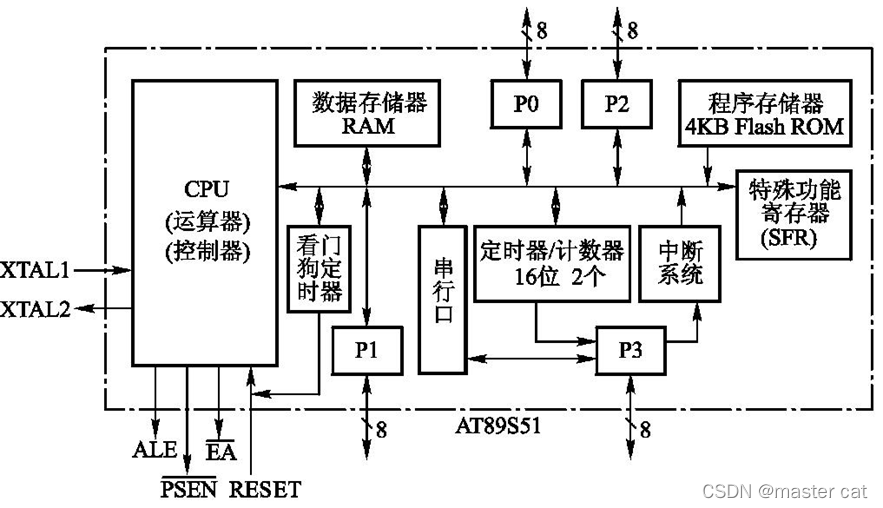

51单片机的组成

(1)8位微处理器(CPU)

(1)8位微处理器(CPU)

(2)数据存储器(128B RAM)

(3)程序存储器(4KB Flash ROM)

(4)4个8位并行I/O口(P0口~P3口)

(5)1个全双工异步串口

(6)2个16位定时器/计数器

(7)1个看门狗定时器

(8)中断系统:5个中断源、5个中断向量;

(9)特殊功能寄存器(SFR)26个;

(10)低功耗的空闲模式和掉电模式;

(11)3个程序加密位;

优点

相比AT89C51,AT89S51有

(1)增加在线可编程功能ISP功能(In System Program),现场程序调试和修改更加方便灵活

(2)数据指针2个,方便对片外RAM的访问过程

(3)看门狗定时器,提高系统抗干扰能力

(4)增加断电标志;

(5)增加掉电状态下的中断恢复模式;

各部件的功能

- CPU(微处理器)

8位,包括运算器和控制器两部分,还有位处理功能。 - 数据存储器(RAM)

128B(52子系列为256B),最多可扩64KB。片内RAM为高速RAM,可加快速度和降低功耗。 - 程序存储器(Flash ROM)

4KB Flash(AT89S52 则为8KB;AT89C55片内20KB),如不够,片外可外扩至64KB。 - 中断系统

5个中断源,2级中断优先权。 - 定时器/计数器

2个16位定时器/计数器(52子系列有3个),4种工作方式。 - 1个看门狗定时器WDT

当CPU由于干扰使程序陷入死循环或跑飞时,WDT可使程序恢复正常运行。 - 串行口

全双工异步串行口,4种工作方式。可进行串行通信,扩展并行I/O口,可与多个单片机构成多机系统。 - P1口、P2口、P3口、P0口:4个8位并行I/O口。

- 特殊功能寄存器(SFR)

26个,对片内各功能部件管理、控制和监视。是各功能部件的控制寄存器和状态寄存器,映射在片内RAM区80H~FFH内。

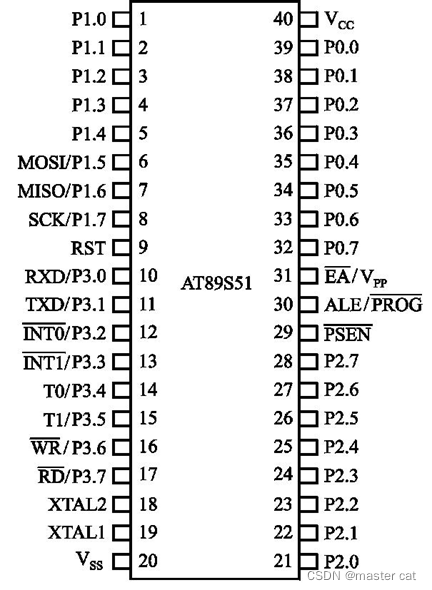

引脚的功能

1.电源引脚

(1)VCC(40脚):+5V电源引脚

(2)VSS(20脚):数字接地

左下脚接地,右上脚接电源

2.时钟引脚

(1)XTAL1(19脚)

输入端,使用片内振荡器时,应接外部石英晶体和微调电容。外接时钟源时,该脚接外部时钟振荡器输出的信号。

(2)XTAL2(18脚):

片内振荡器反相放大器的输出端。

- 使用片内振荡器,该脚连接外部石英晶体和微调电容。

- 当使用外部时钟源时,本脚悬空。

3. 控制引脚

(1)RST (RESET,9脚)

复位信号输入端

单片机要想复位,需要在RST加持续时间大于2个机器周期的高电平,可使单片机复位。

正常工作应≤0.5V。

当看门狗定时器溢出输出时,该脚将输出长达96个时钟振荡周期的高电平。

(2)EA*/VPP (31脚)

- EA*:第一功能:允许访问外部程序存储器控制。

- EA*=1

PC值≤0FFFH时,单片机读片内4KB Flash中的程序,

PC值 >0FFFH时 (超出片内4KB Flash地址范围),转向读取片外60KB(1000H-FFFFH)程序存储器空间中的程序。 - EA*=0

只读取外部的程序存储器中的内容,读取地址范围0000H~FFFFH,片内4KB Flash无效。

- EA*=1

- VPP:第二功能,对片内Flash编程,接编程电压。

(3)ALE/PROG*(30脚)

-

ALE:第一功能

为访问外部存储器提供低8位地址锁存信号,将低8位地址锁存在片外地址锁存器中。 -

PROG*:第二功能

对片内 Flash编程的编程脉冲输入

4. 并行I/O端口

剩下的32个引脚都是并行I/O口引脚

p0,p1,p2,p3共四个引脚,每个引脚8位

4个8位并行I/O端口,为P0、P1、P2、P3。

输出锁存器属特殊功能寄存器。

端口组成:每位均由输出锁存器、输出驱动器和输入缓冲器组成,

4个端口均可位寻址。

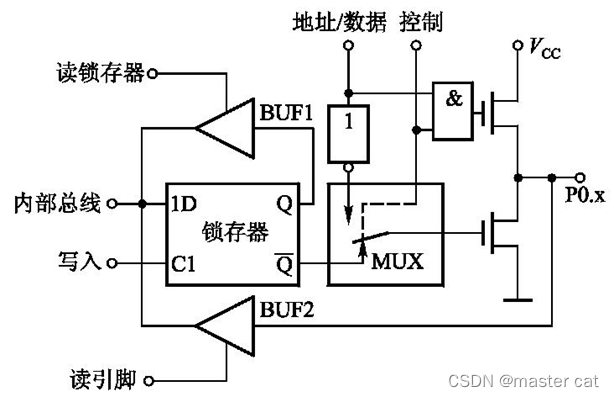

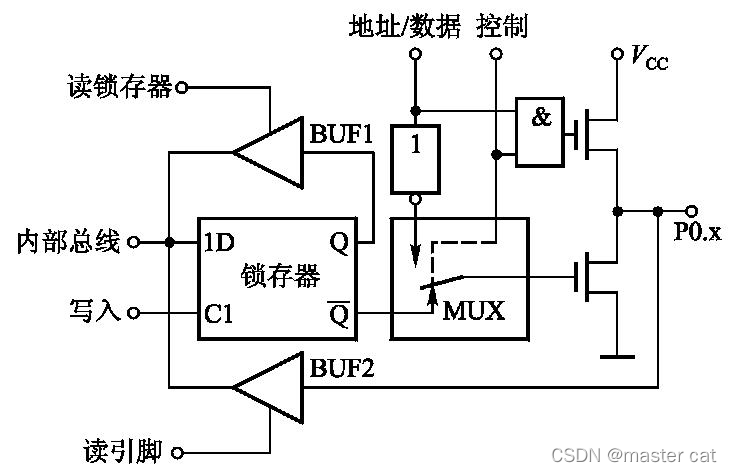

P0口

8位,漏极开路的双向 I/O口

漏极开路意味着有一个高阻态

可作为系统总线低8位地址总线及数据总线分时复用端口。

也可作通用I/O口,需加上拉电阻,这时为准双向口。如作通用I/O输入,应先向端口写入1,可驱动8个LS型TTL负载。

双功能的8位并行端口,字节地址为80H,位地址为80H~87H。

电路结构

P0口位电路包括:

(1)1个数据输出的锁存器。

(2)2个三态的数据输入缓冲器,分别是用于读锁存器数据的输入缓冲器BUF1和读引脚数据的输入缓冲器BUF2。

(3)1个多路转接开关 MUX,它的一个输入来自锁存器的 Q*端,另一个输入为地址/数据信号的反相输出。 MUX由“控制”信号控制,实现锁存器输出和地址/数据信号间转接。

(4)数据输出的控制和驱动电路,由2个场效应管(FET)组成。

工作过程

(1)P0口用作地址/数据总线

P0口

51单片机由8位微处理器、数据存储器、程序存储器、中断系统、定时器/计数器、串行口、并行I/O端口等组成。其主要优点包括在线编程功能、增强的存储和控制功能。各部件如P0-P3口各自具备特定功能,如P0口为地址/数据复用口,P1、P2、P3口为准双向I/O口。时钟电路设计确保了指令执行的时序。复位操作和特殊功能寄存器如PSW对程序运行状态有重要影响。51单片机广泛应用于嵌入式系统、控制系统等领域。

51单片机由8位微处理器、数据存储器、程序存储器、中断系统、定时器/计数器、串行口、并行I/O端口等组成。其主要优点包括在线编程功能、增强的存储和控制功能。各部件如P0-P3口各自具备特定功能,如P0口为地址/数据复用口,P1、P2、P3口为准双向I/O口。时钟电路设计确保了指令执行的时序。复位操作和特殊功能寄存器如PSW对程序运行状态有重要影响。51单片机广泛应用于嵌入式系统、控制系统等领域。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2636

2636

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?